DRAM-Less SSD units are a type of SSD that, as the name suggests, do not have onboard DRAM memory and therefore are much cheaper than conventional SSDs. But how does the lack of RAM affect such an SSD and why? In this article we explain how data access to an SSD is, how the lack of DRAM affects some SSDs and what is the future of this type of peripherals.

An SSD drive is for now much more expensive than a hard disk in terms of storage cost, to this we have to add the periods in which RAM rises in price or suffers from a shortage. In those times is when the DRAM-Less SSD drives are the cheapest if we compare their storage capacity by price with other SSDs. But are they the right ones in terms of performance?

The Flash controller on SSD drives

To understand the existence of the Flash Controller we have to understand is the way in which the CPU communicates with the peripherals in PC, this being what we call Memory Mapped I / O, which translates into I / O by memory mapping. This technique consists of assigning each peripheral a series of memory addresses. In such a way that when the CPU makes a request to said memory address then it is communicating with that memory address.

The advantage that this has, in order to communicate with the rest of the system memories, is that this allows them to see the rest of the memories as a universal well of RAM. It even allows the CPU to communicate with the memory of the different peripherals as if it were part of its own memory.

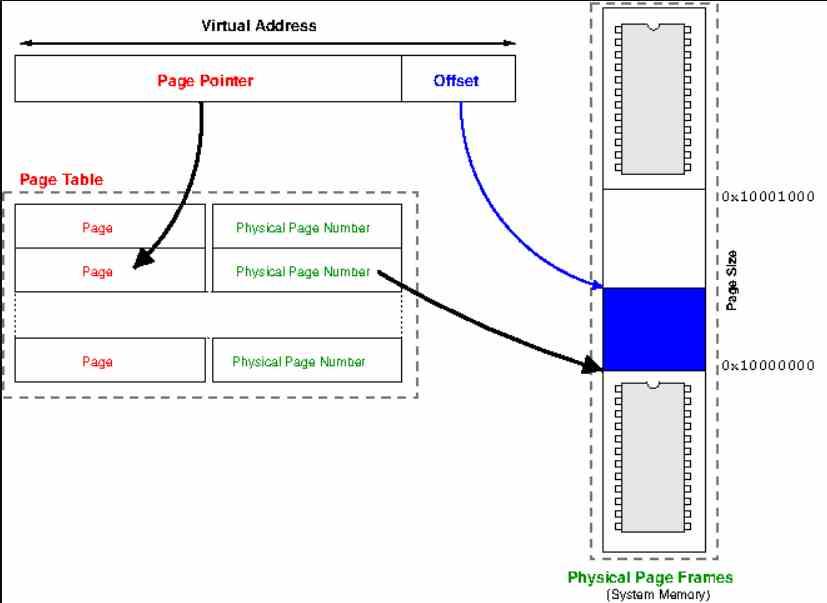

This is because the CPU uses a virtual address system that undergoes a transformation into physical addresses in the process. We are not going to go into this article about access to RAM, but we do need to take into account that each memory in the system has its own physical addressing, so to access said memory, a unit in charge of translating is necessary. the addresses, in the case of RAM is the memory controller, which is currently integrated in CPUs.

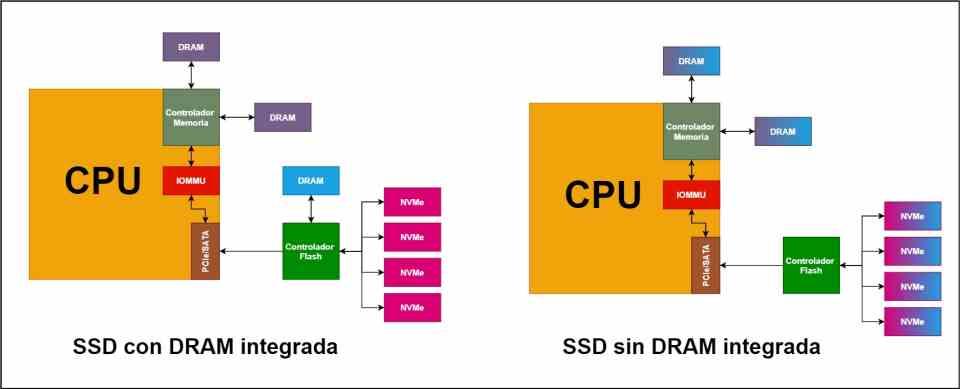

In the case of SSD or solid state disks there is the flash controller, its task is the same as the RAM memory controller, but instead of doing it with the RAM it does it with the flash memory found in the SSD. . Unlike the memory controller, it has not been integrated into the CPU today.

Why do most SSDs have DRAM memory?

When accessing any type of memory, a memory map is necessary, which is a data structure that tells the CPU how memory is organized. In CPUs with virtual memory support, it refers to Page Tables, which store the correspondence between the virtual addressing that the CPU uses to communicate with memory and the physical and real addressing of memory.

Page Tables are usually stored in RAM and are used not by the CPU itself but by one of its units, the MMU, which is inside the memory controller and is the unit that is responsible for managing the RAM memory. Before we have commented that the operation of the Flash controller is the same as the RAM memory controller, but for the flash memory.

The problem? The address moving process requires very fast memory, so it cannot be done in NAND Flash as the access latency would be high enough to completely eliminate all the benefits of the SSD. That is why most SSDs have a well of RAM, which serves to save the address transfer table and to be able to access the data required by the CPU as quickly as possible.

Why is the performance on a DRAM-Less SSD lower?

Yes, and they are called DRAMLess, their particularity? They are much cheaper than conventional SSDs due to the fact that they do not have DRAM memory integrated in them. The lack of a well of DRAM memory forces the Flash Controller in SSD DRAMLess to look for the second fastest memory that it has accessible, which although it seems counterproductive from the distance is the RAM of the system instead of the NAND Flash that is in the own SSD.

This means that in a DRAM-Less SSD to access the address table you will have to make a request as a peripheral to the IOMMU and this will make it to the system RAM. The reason why it does not make it to the NAND Flash that is closer is because such a level of activity would end up wearing down the SSD much faster, shortening the useful life of the SSD.

Of course, there are cases in which the Flash Controller does not use the system’s RAM to access, but the NAND Flash memory itself. What consequences does this have? Much faster wear and tear on the read and write cycles of the SSD’s NVMe chips, which will lead to shorter SSD life.

The future of DRAM-Less SSDs

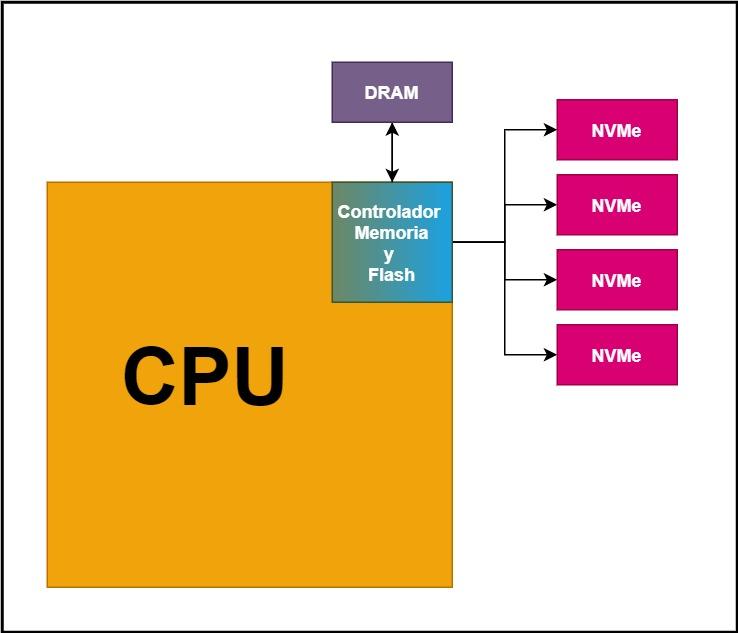

One of the things that is sought in the future thanks to the adoption of technologies such as the CXL, which will be integrated from PCI Express 5.0, is the fact that the peripherals can access the RAM memory space directly without having than going through the IOMMU drive, this will mean that the DRAM-Less SSDs will be faster.

This possibility means that the memory controller integrated in the CPUs doubles as the Flash memory controller, allowing the NVMe memory chips to be directly accessed. To this must be added the existence of DIMMs that do not have RAM memory chips, but rather non-volatile memory. Are we going to expand the storage of our PCs of the future with DIMMs? Who knows, the technology is there.

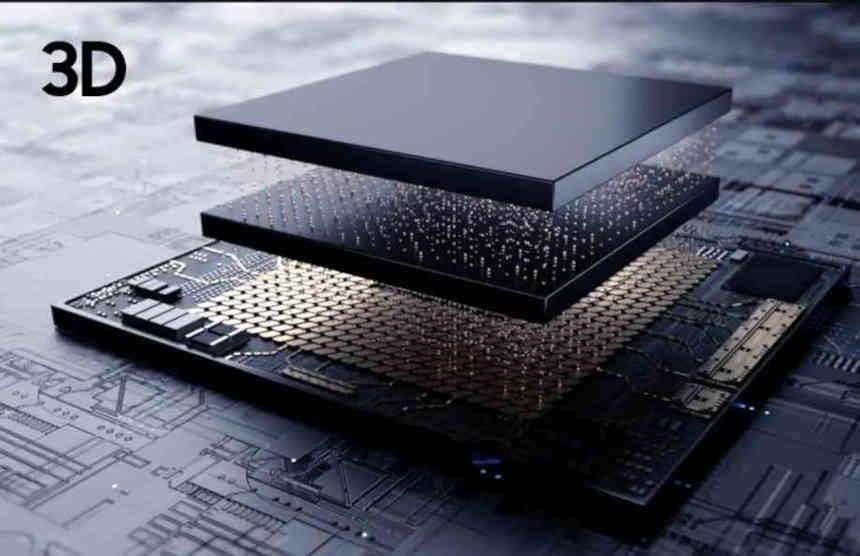

The other possibility is the use of embedded memory, especially using 3DIC configurations to put the DRAM used as cache on top of the memory controller. The DRAM would still be but not on a separate chip but embedded in the memory controller through a vertical interconnect. Due to the proximity of this memory it would be faster

We will see both concepts in the future, although in the second case we will see it more in CPUs without the Flash controller integrated within them.