One of the most widespread concepts in computing today is undoubtedly that of XMP. Any user moderately interested in hardware knows that when we talk about memory overclocking profiles, Intel has taken the measure of AMD, which constantly tries to adapt to these requirements through its AMP technology. With the departure of Alder Lake-S as a revolutionary architecture, Intel has gone a step further by presenting XMP 3.0 , but what news does it hide?

Some wonder the reasons for Intel’s decisions regarding RAM and specifically XMP. Although we will never know, the truth is that the move from DDR4 to DDR5 was an ideal time from the perspective of overclocking to implement changes and improvements, since as we are seeing the 4,800 MHz of the JEDEC they are being left behind only days after Core 12 CPUs will be introduced.

Therefore, and given how fast manufacturers accelerate and update their modules with increasing serial speeds, it remains only to wonder, has Intel taken this into account? Is XMP 3.0 up to date with what will be required of it?

Intel XMP 3.0, a necessary twist

eXtreme Memory Profile or XMP has been with us since 2007 and in this third version looking back and after 14 years it is normal for the blue giant to launch a new revision with news. Why? For the changes that DDR5 supposes with respect to DDR4. We will not go into this topic since we already dealt with it in extension, but if there is something to say about XMP 3.0 it is that it is exclusive to DDR5 as such.

The term Profile of its name comes to the finger to explain the first of the points where Intel has given the manufacturers, since as we well know this technology is based on the recognition of a series of configuration tables that each manufacturer integrates to taste by model, chip and memory version to get the IMC to recognize and apply these settings through the firmware.

What’s New in Intel XMP 3.0

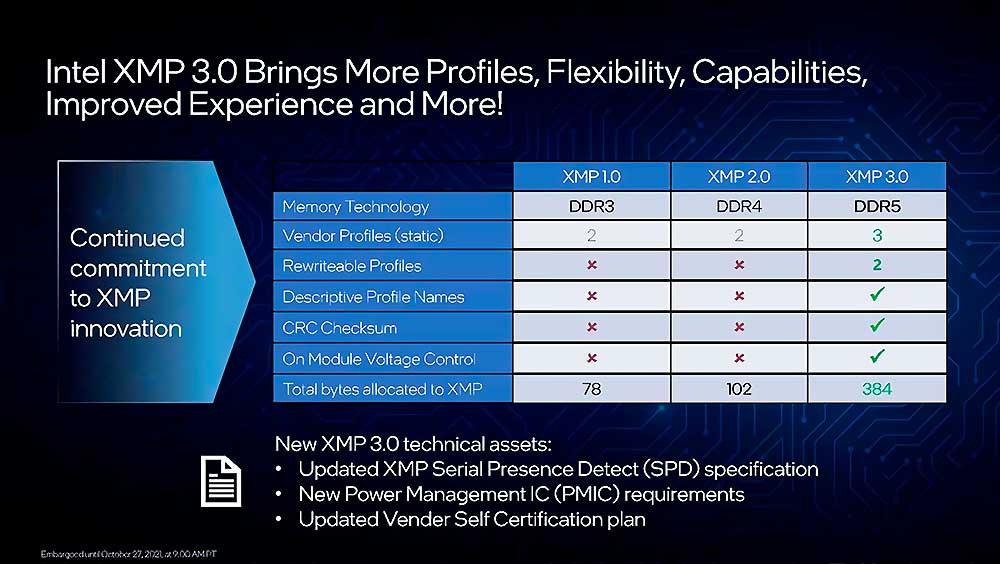

These tables include speeds in MHz, clocks and times of primary, secondary and tertiary accesses that are logically faster in some cases or slower in others, but that in all cases increase the general performance of the memory and with it the system. In the first version called by its own name, XMP, Intel managed to include in it the inclusion of reading a profile within memory plus that of the JEDEC (technically it is one profile, but they are counted as two)

XMP 2.0 raised the level to two reading profiles, where manufacturers could establish if they wanted two different values and tables, personalizing the user experience and favoring different performances (three reals counting the JEDEC). With XMP 3.0, manufacturers can now have two or three profiles to include, being able to select two customized by the user.

SPD update

One of the key points for the XMP profile is precisely the SPD or Serial Presence Detect specification . This has brought multiple headaches to manufacturers and users, mainly because they can be written from EEPROM and therefore become corrupted. There are some programs that can do it and of course, it creates crashes in the memory controller, since it cannot read the values correctly from the XMP and the memory is unusable until a new flashing takes place correctly.

Now and with XMP 3.0 we will have two updateable profiles, which helps so that if one is corrupted the other can leave the memory working, its SPD can be extracted and later it could be flashed module by module, repairing the memory as if nothing had happened.

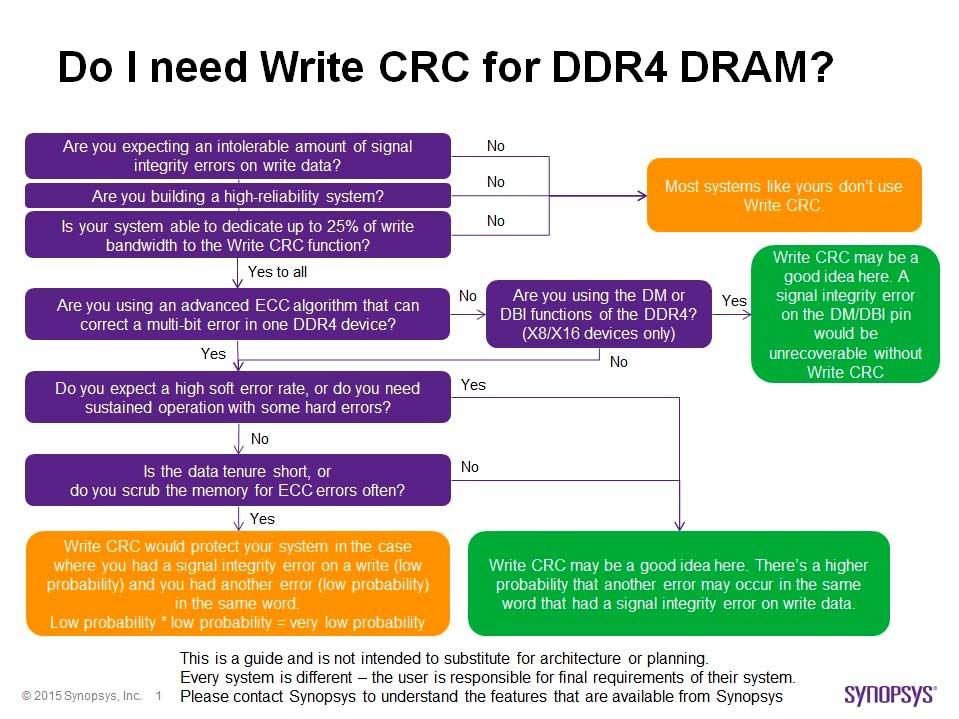

CRC Checksum

Oddly enough and already explained this, why don’t DDR4 modules with XMP 2.0 have CRC? It is not exactly like that and logically it has a why. CRC as such was added in its Write version in the JEDEC standard for DDR4, but the cyclic redundancy code has a problem: high bandwidth consumption. The data shows consumption of 25% of the total writing of the system and of course, it is not acceptable to lose that amount of bandwidth with the margins and speeds that we move today.

This is no longer a problem with DDR5, since in addition to including the PMIC in the memory itself, in the module physically speaking, the speeds are and will be monstrous compared to DDR4, especially if we have double bandwidth that integrates this type of memory. Therefore, Intel with XMP 3.0 integrates the sought after CRC Checksum that will protect the data and integrity of the SPD as well as the CPU memory controller.

Greater space increase for XMP 3.0

One of the key aspects and already understanding everything we have said about the new XMP 3.0 is that, logically, we need more space to house all this. Therefore, Intel has gone from 78 bytes per module for XMP 1.0, to 102 for XMP 2.0 and now raises it to 384 bytes of control for XMP 3.0.

This is what allows preset memory profiles like SPD to be selected from the motherboard BIOS / UEFI. The question we have then is the behavior of the BMI of the new Alder Lake and Meteor Lake processors (a significant frequency jump is expected) with the different speeds that we are going to see from the manufacturers and chips.

Are we going to see XMP 3.0 profiles above 6000 MHz? Can the BMI of the CPUs support them without overflowing the voltage and with it the consumption and degradation? At the moment we know that there are brands working on profiles for DDR5-7000, so it seems that either these new memories and chips are managing to evolve much faster than CPUs and their BMI, or it means that the potential for uploading and support / endurance of the integrated memory controllers is greater than we might think.

It must be borne in mind that although XMP 3.0 reaches very high speeds in certain modules, it is the IMC that determines if it is capable of supporting said speed and its voltage, which is logically independent of that of the RAM itself.

Having said and clarified this, we can only say that Intel has taken a very big step forward, the biggest since it launched XMP in 2007 and as such, now it is AMD that is going to have to adapt its technology and IMC to these new requirements with Zen. Four.