A few weeks ago, ARM introduced the ninth generation of the set of registers and instructions used in processors with the ISA of the same name. ARMv9 is the name under which the new version of this ISA has been baptized, which will be used in future SoCs for PostPC devices. What is ARMv9 and what is new about previous versions, what will the future ARM CPUs look like?

An ISA is nothing more than the language understood by the different processors and therefore marks what the set of ones and zeroes mean in the code they execute. The binary for an x86 CPU does not have the same meaning as the binary for an ARM CPU for example.

However, the advancement of technology makes it necessary to add new instructions to the ISAs, which gives them the ability to add new functionalities to increase their performance, security when processing data or to face new challenges that are presented to them.

In this article we are going to talk about the ninth generation of the ISA ARM, which after years aimed at low consumption CPUs and microcontrollers have decided to be more ambitious and enter the market that requires the highest performance, that of data centers and high performance computing or HPC.

Scalable Vector Extensions 2

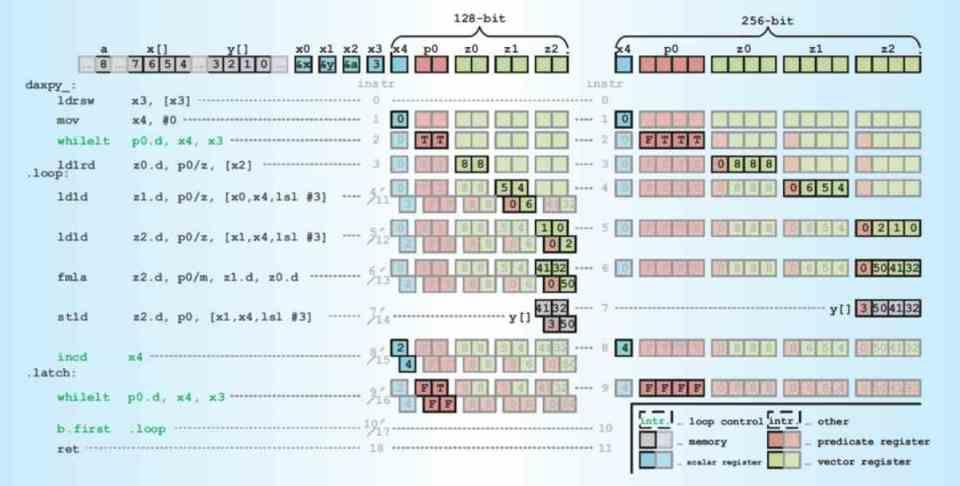

The Japanese Fujitsu created for its ARM core a series of proprietary extensions called SVE, which stands for Scalable Vector Extensions. From its name you may have guessed that we are talking about a set of SIMD instructions. Let’s not forget that in CPUs with ISA ARM for years the Neon instructions have been used. Which will be replaced by the SVE2 instructions in ARMv9.

SVE was created by Fujitsu for its Fugaku supercomputer, which makes use of its A64-FX cores. The intention? Take advantage of the data parallelism required by scientific computing, which uses higher precision numbers. This translates into much larger SIMD units and therefore more bits.

Since ARM’s interest is to bring their cores to the high performance computing market and servers they have decided to adopt SVE and merge it with Neon to create SVE2. The biggest advantage that SVE adds to Neon? These are size-agnostic instructions, so it is not necessary to have a version of each instruction for different sizes as is the case with AVX instructions on x86.

Memory realms in ARMv9

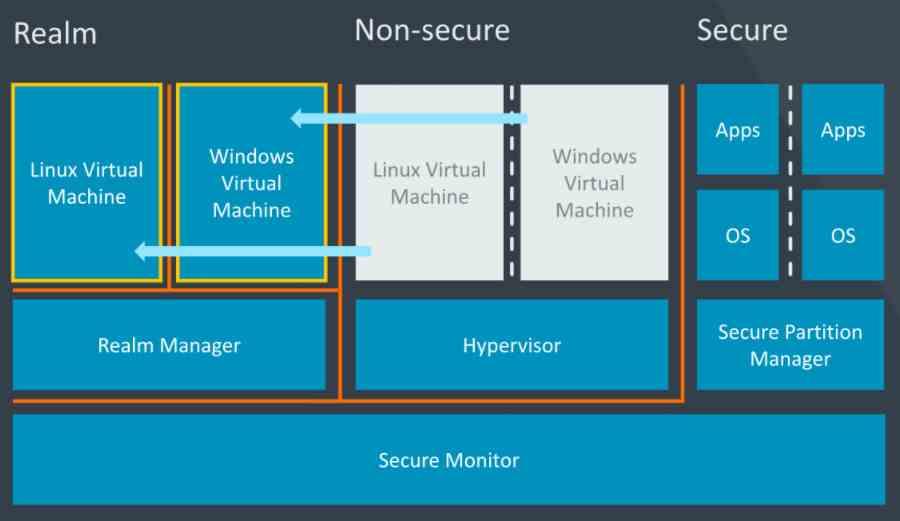

An interesting concept that the ISA ARMv9 adds to the equation is the concept of realms, which consists of being able to take part of the memory addressing and make the code that is executed in it does not affect the rest of the system, therefore it is totally isolated . Which is ideal for the implementation of virtual machines where one operating system runs at the same time as another on the same CPU.

Normally CPUs have different levels of privilege, but with the realms concept that has been added in ARMv9 it will be possible to run more easily running virtual machines on a CPU with ARM ISA, but the advantages of this are not only limited to virtual machines, but can also be used in specific applications.

So ARMv9 seems to be an extension to the ISA more prepared for data centers and other types of computers where virtualization and security are much more important than other functionalities. Not surprisingly, ARM is waging a war against Intel and AMD in the server CPU market, where x86 processors dominated the market until now.

Memory Tagging Extensions

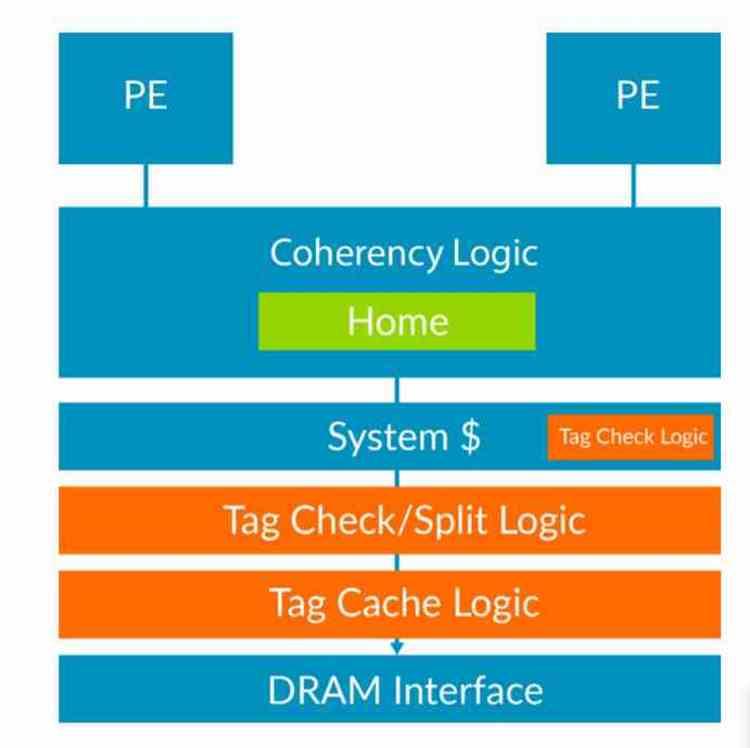

They are not new to ARMv9, but rather to version 8.5. Its utility? It is a mechanism in charge of keeping track of all illegal memory accesses made by programs. An illegal access is nothing more than an access to a memory address that the program does not have permission to access. What is the use of this? As it serves to avoid the so-called buffer overflow, a common security problem in all processors that occurs when the amount of data copied exceeds the memory reserve, writing unexpected code in neighboring memory addresses.

If the memory overflow is successful then the original code will be replaced by new in-memory code, which will be executed by the CPU as soon as it reaches memory. So it is important to avoid this, especially if we are talking about data centers that tend to serve millions of users at the same time and where a buffer overflow can be used to steal compromised user data.

The MTE is not part of the ISA itself, but is a mechanism implemented in the Northbridge of ARMv9 CPUs that tracks all memory accesses and whose functionality is to avoid memory overflows in a transparent way.

ARMv9 only for data centers and servers?

The novelties of the ISA ARMv9 that we have described in the previous sections have a marked specific character and have nothing to do with the use in the classic devices in which the ISA ARM is usually seen. Of all of them, it calls the SVE powerfully, since one of the reasons why you do not usually see large SIMD units in CPUs for PostPC devices is the enormous energy consumption that their use supposes.

At the moment the only two cores announced by ARM are two from the Neoverse family. On the one hand the NeoVerse V1 under the codename “Zeus” and on the other the Neoverse N2 under the codename “Perseus”. These are not cores that you are going to see in a future smartphone, but in the data centers and servers for high-performance computing of companies such as Amazon AWS, Oracle, Tencent, Google, etc.

ARM has not yet announced any kernel for PostPC devices such as smartphones and tablets. Although we can not forget that the goal of ARM is to displace x86 in various markets, not only on servers, but also on the PC. The purchase by NVIDIA and its great influence on the PC video game market may bring the arrival of gaming PCs with ARMs and NVIDIA GPUs, although it is a future that will need a lot of support from the developers of video games and not NVIDIA-ARM itself.