Surely the vast majority of you do not realize the fact that we are on the verge of a crossroads as far as CPU and GPU are concerned. There is not much margin, there is not much time and what remains is running out. A change is needed in a component as basic as the concept of computing itself: in the transistor. Intel has its vision of the problem and a solution: this will be the Intel RibbonFET.

To understand the solution, we first have to be aware of the problem, understand it and know what the limits are that will mark us, so in this case we are going to start there, with the problems of transistors today. A transistor is the smallest electrical unit that can be manufactured for an electronic component, an electrical element as such that is made of semiconductors and recorded by incredibly advanced scanners using a wavelength on mirrors.

It is basically a switch that is interconnected between dozens of layers of silicon (as a general rule) of a very small size and that has an extremely clear function: to alter the flow of current that passes through it, giving way or cutting it. Each cut or step represents either a zero or a one in binary and with the passage of time what has been achieved is to improve it allowing more speed in the change of state, more or less energy for said change and more or less efficiency when let the current pass.

We are approaching the edge of transistor technology

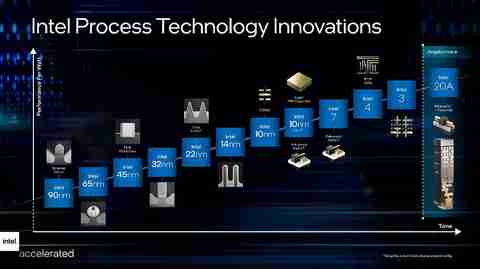

As we have already thought, every transistor has a series of designs that vary according to the manufacturer. Intel has its vision, TSMC the same and Samsung more of the same, so although all are more or less copied in the advances, the implementation and improvements are different.

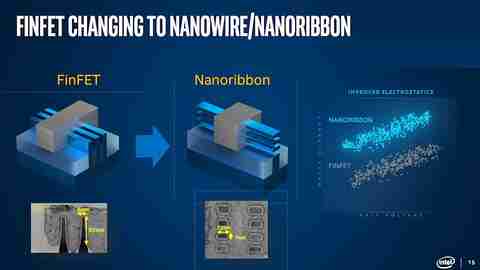

A decade ago Intel introduced the FinFET transistor, which has been chosen by all manufacturers, but that design is coming to an end for several reasons. With this type of transistor we had a flexible design of the same, normally wide, where several gates crossed it, allowing manufacturers to better control energy management, welding and construction materials, as well as continue reducing its size in nanometers.

The main problem we have is simple: it cannot be reduced much more in size, since we have limited longitudinal space and the gates of each transistor cannot join any more without losing electrons. To this must be added that the distance between them is so miniscule that welding and interconnection requires tremendously expensive new materials and alloys, some still experimental, that guarantee the passage of energy and do not trigger the price.

What is the solution? A new type of transistor that allows not only more layers to drive current, improve control, welding and efficiency, but also reduce the distance between transistors to Angstroms (molecular and atomic unit of measurement).

RibbonFET, Intel’s solution to the new limit of lithography

If you can’t keep reducing the space and controlling all the parameters without triggering the cost, it only remains to investigate a new path. This new path in the form of a new architecture for the transistor is called GAA or also known as Gate-All-Around. From here the concept is divided into three aspects or even 4 (it is not totally clear):

- TSMC GAAFET .

- Samsung MBCFET .

- Intel RibbonFET .

- Global Foundries is in a limbo with rumors, but nothing concrete.

What happens here? Well, as happened with FinFET, GAA is going to have several variants all based on the same transistor concept. We already talked about Samsung MBCFET, GAAFET has not yet been exposed as such although it will arrive with the company’s 2 nm, so after the presentation of Intel in its Architecture Day 2021 and after revealing some more details, we are going to know the bet of the giant blue: RibbonFET.

The concept is simple, but difficult to implement. They take a transistor of flexible width which will be reduced with each lithographic jump and which allows several layers, now called nanosheets, dry sheets or fins by the industry, to be connected vertically on the transistor instead of horizontally. What is achieved? Well, first of all, greatly reduce the width of the transistor, allow more nanosheets on a smaller surface and above all, a single Gate that will control all the energy of the cell.

The electrostatics has improved enormously as Intel showed in its official presentation, where we only have to see the sizes of the Pitch Gate and the Gate Stack. It goes from 6 nm x 50 nm to 12 nm x 7 nm and with more control nanosheets and better soldered.

A variable nanosheets design according to the needs of the transistor

Apparently and as we have seen in various documents since Intel spoke of this new type of transistor, it seems that the blue giant can collect a variable number of nanosheets per transistor.

This detail is important, since as Intel goes down the lithography based on better EUV scanners it will be able to either keep the same number or remove the ones it needs to optimize each Gate. The docs show from 2 to 5, but in the last datasheet the round number appears to be 4. More fins / nanosheets require more steps to create the transistor, so it raises the cost of each chip, so possibly Intel will start with a number means of them until you have improved engraving and production control, materials and welds that allow you to eliminate a number of determined nanosheets and to reduce costs without compromising the stability, speed or efficiency of the transistors.

This will logically depend on the height of the Gate and with it the number of Sheets that we can install in it, since now instead of being surrounded by three sites as happened in FinFET, each end is totally surrounded by the Gate, which means one side is optimal, but the other makes it difficult to reduce the height between the sheets.

When will Intel RibbonFET implement in its chips? According to the company itself in 2024, surely by the end of that same year if everything goes well, although if it were smooth sailing we could see it by the middle of that same year. In any case, it will be its 20A lithographic process that includes it and will compete with TSMC’s GAAFET and Samsung’s MBCFET . Intel is so confident that it will make a difference that it has already stated that it will lead the semiconductor industry and its technology again in 2025 – no doubt a declaration of intent.