Is it possible to integrate RAM inside a CPU? What benefits would it bring? Is it possible that we will see it in the future? One of the most interesting ideas is to place the RAM as close to the processor as possible. We will explain how this is going to be possible and in the event that it is fulfilled, how it will affect the hardware of the PC and the programs that it executes.

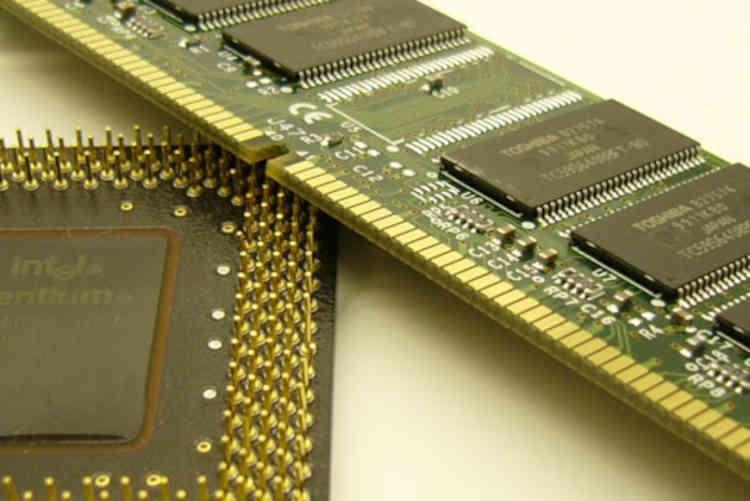

In 2003 one of the most important improvements was made as far as the important processors are concerned, the implementation of the Northbridge inside the processor, which until then had been outside of it. The Northbridge is the piece that communicates the CPU and other processors on the motherboard with the RAM.

The next step towards integration? Possibly integrate the RAM or at least part of it inside the CPU.

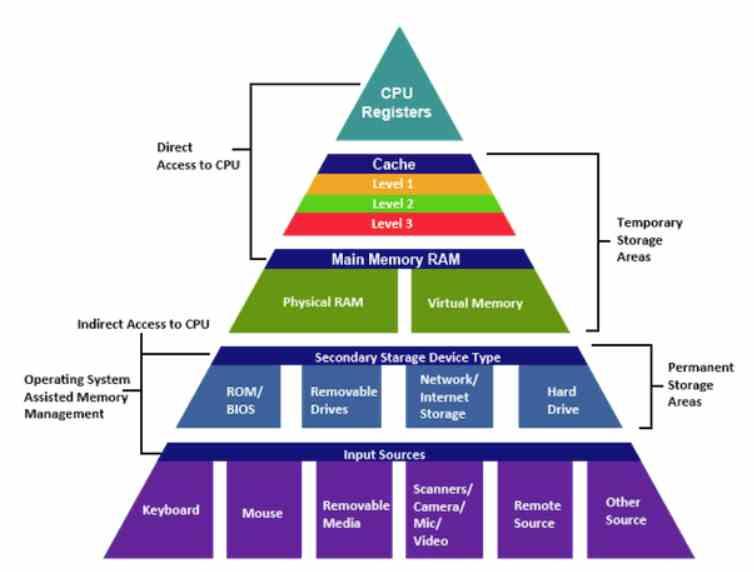

Distance to data affects performance

One of the basic principles regarding the performance of a processor is the distance between the memory that stores the data and the unit that processes the data, which the shorter the better due to the fact that the electrical signal has to travel a much shorter distance, which translates into less instruction execution time.

That is why a data that can be accessed in the first level cache will execute faster than a data that is in RAM. Ideally, you can place huge amounts of memory close to the processor.

But it is not possible to do so since space is limited and the fact of placing the RAM next to the processor would end up negatively affecting both, causing them together to reach enormously high temperatures that can lead to the combined performance of both being lower than with both separately.

Making use of 3DIC technology to integrate RAM into the processor

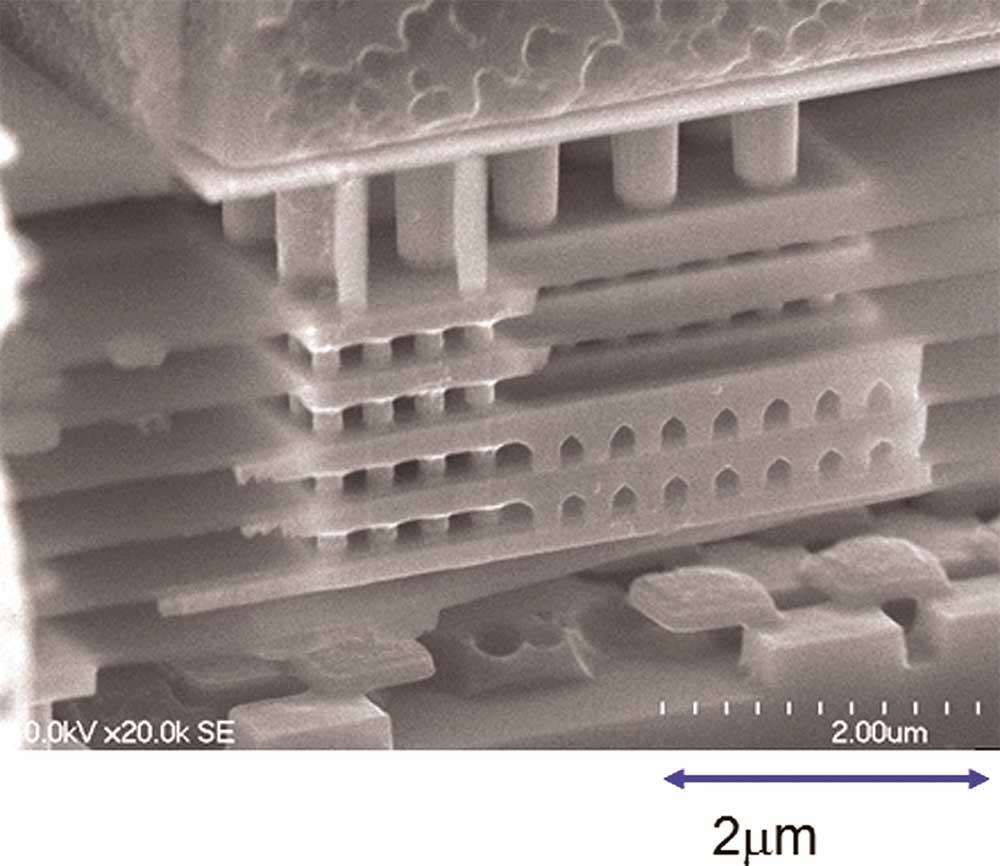

We have seen 3DIC technology combining several stacks of memory chips, but not combining the CPU with memory, especially in PCs. For example, HBM memory was initially designed to be mounted on top of a processor, but the temperatures that were reached were so high that they had to lower the clock speed of both parties.

In Samsung smartphones I try to make use of the Wide I / O standard, which consists of a vertical interface through 512-bit silicon channels, at 200 Mhz and of the SDR type. It reached only 12.8 GB / s but was considered as an alternative with lower latency and energy consumption compared to LPDDR memories of the time. The problem? It increased costs so it was rejected by the industry.

The solution has proven elusive, but one of the advantages of a 3DIC system is that it breaks the problem of the density of the embedded memory.

The problem of embedded memory capacity

DRAM memory has a density 3 times greater than SRAM, the problem is that beyond 40nm it is not feasible to implement DRAM memory inside a processor, so it was time to make use of SRAM memory. The problem is that SRAM memory even at high density makes it impossible for us to fit enough RAM density inside a processor.

The simplest logic tells us that if we place a chip with only RAM on top of a processor with 3DIC technology we should increase the density, the problem is that to increase the memory density we would need a huge memory stack, which would make the memory more expensive. processor and would not be viable.

But there is a solution, divide the RAM into two different memory wells, in a different hierarchy.

Two RAM wells, one integrated into the processor, the other into the DIMMs

The concept would consist in that on the one hand we would have a well of RAM memory connected to the processor, with very low latency and with a much faster bandwidth. On the other hand we would have the classic RAM memory in the classic RAM memory modules of a lifetime.

The idea would be to assign through the operating system the use of the different RAM wells in the system, these would not have two memory wells in view but only one where the only difference in addressing would be precisely the memory address to which I would write down each program.