The implementation of the Infinity Cache in GPUs with RDNA 2 architecture has been one of the novelties of the new AMD GPU architecture, but the question that comes to mind is: is it something exclusive to AMD GPUs or are we going to to see the Ryzen processors, both in CPUs and SoCs?

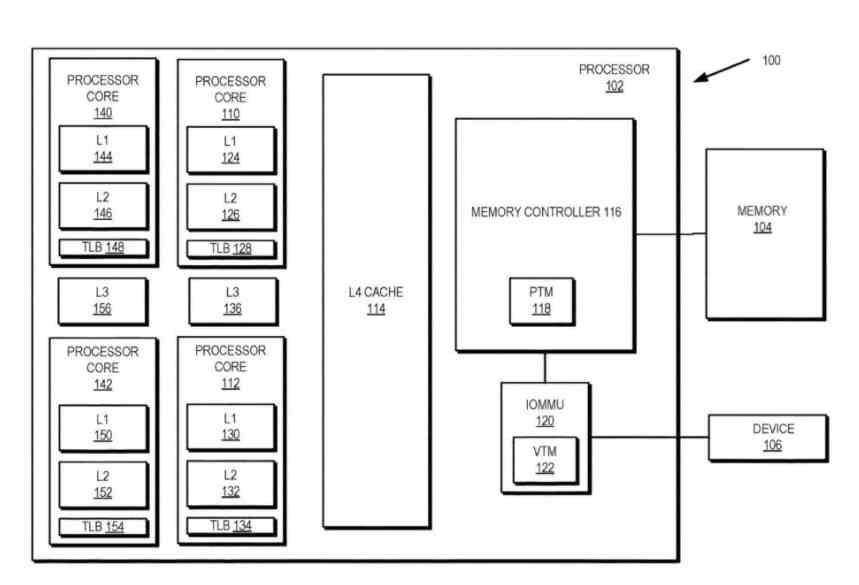

A few months ago the diagram of an AMD patent was leaked, which corresponded to a processor of the AMD Ryzen family, or so we suppose, but with the particularity of showing a fourth-level cache in the diagram, something unprecedented in the AMD processors based on such architecture.

At the same time, the appearance of the Infinity Cache in AMD GPUs brings two questions to mind: are we going to see the Infinity Cache implemented in AMD’s AMD Ryzen processors, will it be used as an L4 cache or in some other way?

The utility conflict of the Infinity Cache and the L3 Cache of the Zen cores

Both the L3 cache of the Zen cores and the Infinity Cache of the RDNA 2 architecture fulfill the same function, since both are Victim Caches and therefore have the same functionality. This means that when it comes to capturing the data and instructions for each of their corresponding processors, they are in charge of collecting the cache lines discarded by the previous cache level.

What is the problem? To understand it we have to take into account where the Infinity Cache would go if it were implemented in both an SoC and an AMD CPU, just before the memory controller and therefore in the Northbridge, as a supposed L4 cache.

What is the conflict? It makes no sense that there is a Victim Cache of another Victim Cache, since in this case the Infinity Cache would be connected to the L3 cache of the Zen cores, which causes a conflict of functions between both parties.

The Infinity Cache connectivity conflict with Zen cores

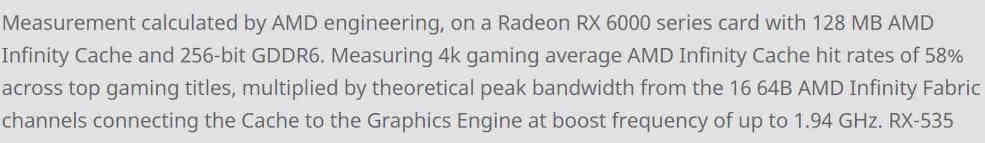

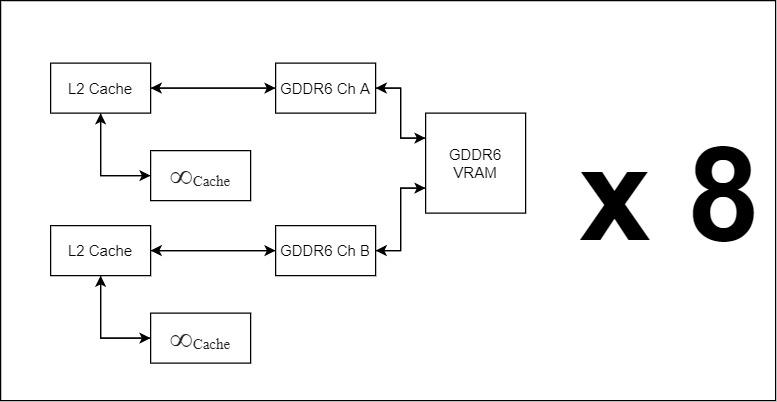

If we look at the Infinity Cache of the Navi 21 GPU, we find that there are 16 partitions in total, connected at one end to 16 L2 cache partitions under a 64-byte / cycle bus for each partition and at the other end to 16 channels GDDR6.

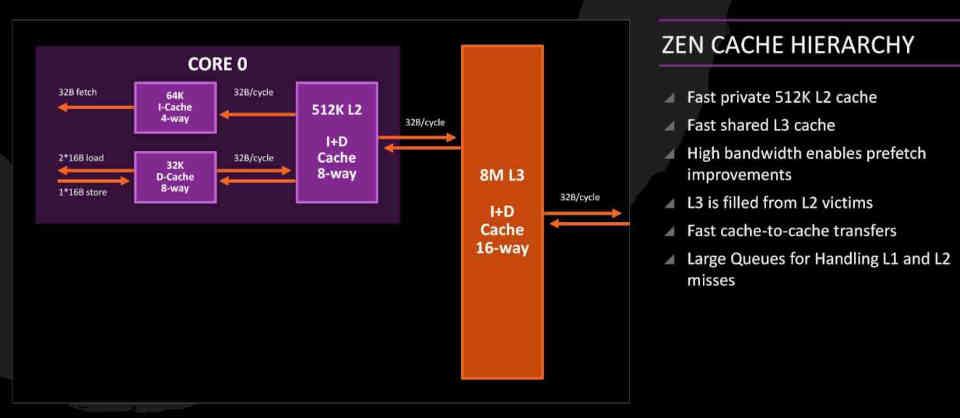

The Zen cores of the Ryzen processors are grouped into a 4-core (Zen and Zen 2) or 8-core (Zen 3) CCXs, but the CCX uses a single Infinity Fabric interface, so the supposed Infinity Cache on a single Zen processor it would be made up of a number of partitions equal to the number of CCXs at least.

So in a configuration with a CCD you would only have one partition, one with two partitions 2 CCDs and the extreme case would be something like an AMD Epyc with 8 CCDs that would have 8 partitions. As a general rule, caches increase in size with each additional level and it is always twice the sum of the previous cache level.

A single Zen 3 CCD has a capacity of 32 MB of L3 Cache, a single partition of the Infinity Cache is 8 MB, a much lower figure than what it would need to operate as L4 Cache of a Zen processor, so in connectivity It is proven that the Infinity Cache cannot function as the L4 Cache of a processor with Zen CPU.

And what about the integrated GPUs?

Since we have seen how the Infinity Cache cannot be used as an additional cache of the Zen cores, the only answer that remains is as Infinity Cache of the RDNA 2 cores integrated in the SoCs, at the moment AMD has not launched any SoC with an integrated RDNA architecture GPU, due to the launch timing we do not think we will see the first generation of RDNA.

In the case of iGPUs, it does make sense to integrate an Infinity Cache that is located between the memory controller and the graphics processor, but it would be for the exclusive use of the graphics processor within the SoC.