In the coming years, the N5 node of the largest Asian foundry will become the most important of the manufacturing nodes in the coming years. Well, through an analysis of one of the chips already manufactured under said manufacturing process, it has been discovered that the density of TSMC’s 5nm node is lower than expected . Is this bad news or a lack of sincerity on your part?

TSMC’s 5nm node and its variants are going to become the most relevant in the coming years within the PC. Not only because of the fact that AMD will use it for its future chips such as the Ryzen 7000, EPYC Genoa and the RX 7000 GPUs. Nor can we forget that TSMC is also a client and even Intel, since the integrated graphics in Meteor Lake and some Ponte Vecchio HPC graphics components will use it for their manufacturing. So in one way or another, the main players in the industry make use of this manufacturing node in one way or another. Although at the moment, the only chips using this manufacturing process are those of Apple

TSMC’s 5nm node density is lower than advertised

Although this headline may seem negative, this has an explanation and it is that from Angstronomics they have made an interesting article where they inform us of the reason why TSMC has given the density of its 5nm node wrong. By this we mean the number of transistors per area and thus how complex the chips can be built. The Taiwanese foundry officially states that it is 171 million transistors per square millimeter . However, a thorough analysis reveals that this figure is lower and that it is 137.6 million transistors per square millimeter .

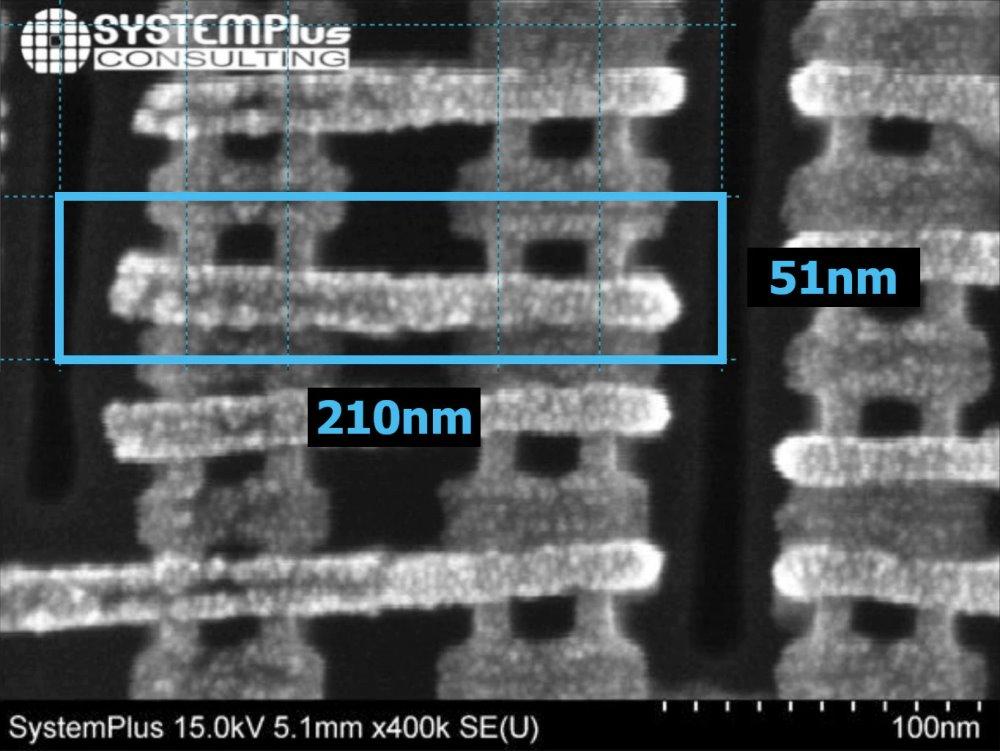

They have done this by measuring through an electronic microscope the size of the transistors used to build the Apple A15 processor of the latest generation iPhone. Which measure 210 nm in Cell Height and 51 nm in CPP . Well, both values are used in a comparative way to know the size of a transistor with respect to a previous node. Thus, TSMC’s N7 node has values of 240nm and 57nm respectively , giving it a density of 90.64 million transistors per square millimeter . In the case of Intel’s 10mm node, recently christened the Intel 7, we’re talking about a figure of 100.33.

If the numbers make you dizzy, don’t worry. This means that in the same space chip designers can fit up to 51.8% more logic gates on their 5nm-built chips than on 7nm chips . Which means that it is not a full node jump. Actually the transistors are not even 5nm. Since this metric ceased to correspond to reality a long time ago and it is more of a marketing tool.

Has TSMC given false figures?

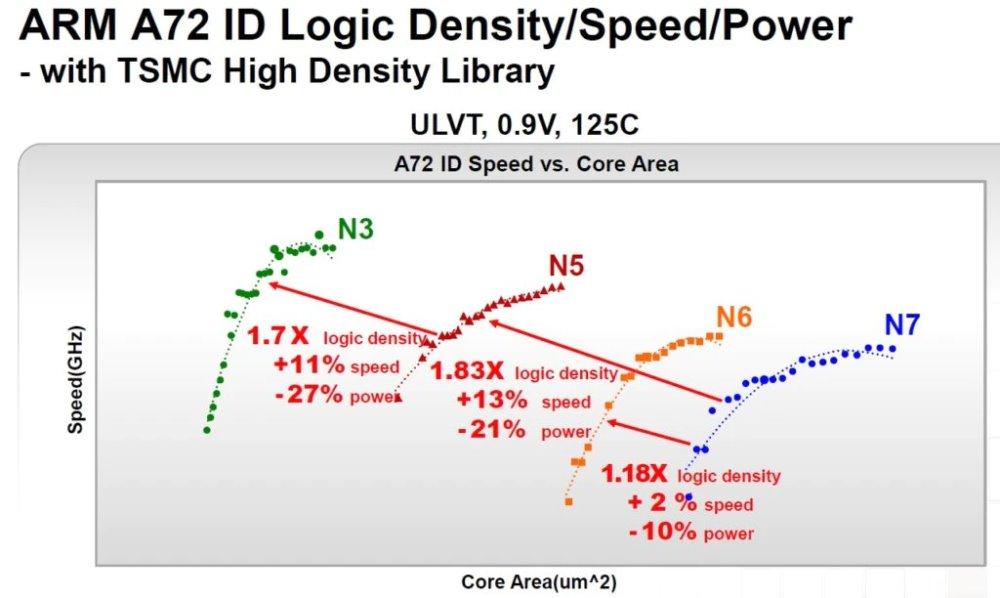

No, not really, and this is because the Taiwanese foundry does not use the metric that we have discussed in the previous section. What TSMC usually does is adapt an already known chip to the new node to get its metrics. For this they make use of the design of a Cortex A72, of course, since it is a fabless design, the foundry has all the freedom in the world when it comes to using one type of transistor or another for the construction of the different logic gates that make up the chip.

So, as you can see in the image above these lines, we can deduce where TSMC gets its figures from . And it is that it refers only to the density of logic. So the SRAM or the analog parts of the chip are ruled out, for example. By the way, it can be seen how the jump from the current nodes to the future ones does not result in a substantial saving in consumption or an important increase in speed. Which partly explains the increased consumption of high-end models of the next generation of graphics cards from NVIDIA and AMD.

In any case, this does not affect any of the partners of the foundry and the future chips that will be made in it. Many of them already finished and about to be printed on their wafers on a large scale.