If there is anything evident in the processor industry, it is that Intel and AMD completely dominate the market in a duopoly that seems unrivaled. However, in recent times the ODM (this means that they do not manufacture chips, they only design them) ARM is gaining more and more importance, especially with designs such as DynamIQ , a bet that promises to improve the power of processors while maintaining the consumption, and in this article we are going to tell you what it consists of.

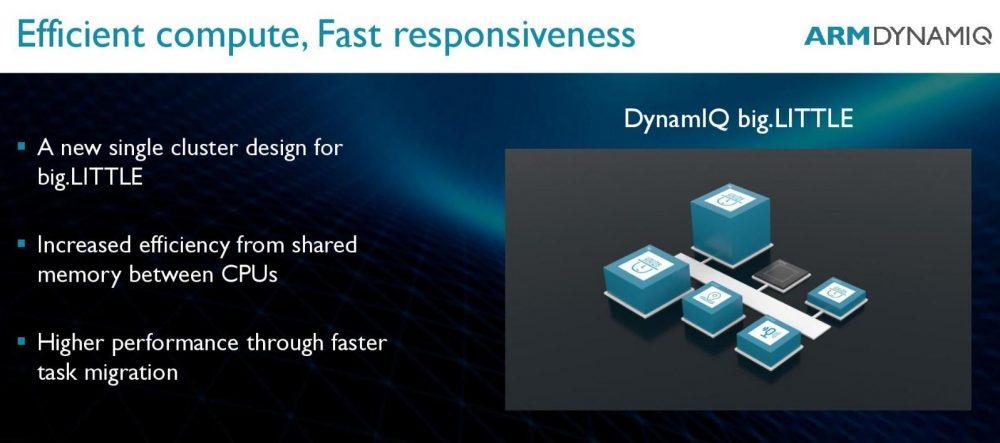

Actually, if there is an ARM design that is known, it is big.LITTLE , consisting of a heterogeneous architecture that consists of larger and more powerful cores to perform demanding tasks and other smaller and low-power cores to save energy when the equipment does not. requires great power. This architecture has been implemented in smartphone chips for a long time and not long ago that Intel (and it even seems that AMD with Zen 5) has adopted a similar paradigm (but in its own way) in its desktop processors, so everything points which is the way to go.

ARM DynamIQ, how to increase power without increasing consumption?

The ARM architecture has been running for many years as an alternative to Intel and AMD, but especially in mobile phones and servers thanks to its low consumption, but it was not until Apple decided to create its own M1 chip and integrate it into its computers until that ARM has truly entered the domestic PC industry.

This new architecture that ARM has called DynamIQ (it is a play on words in English that combines the word “dynamic” with “IQ”, IQ) in principle is aimed at mobile devices and IoT devices, but they have confirmed that they also intend that reaches the ecosystem of personal computers and even servers, since its potential is tremendous.

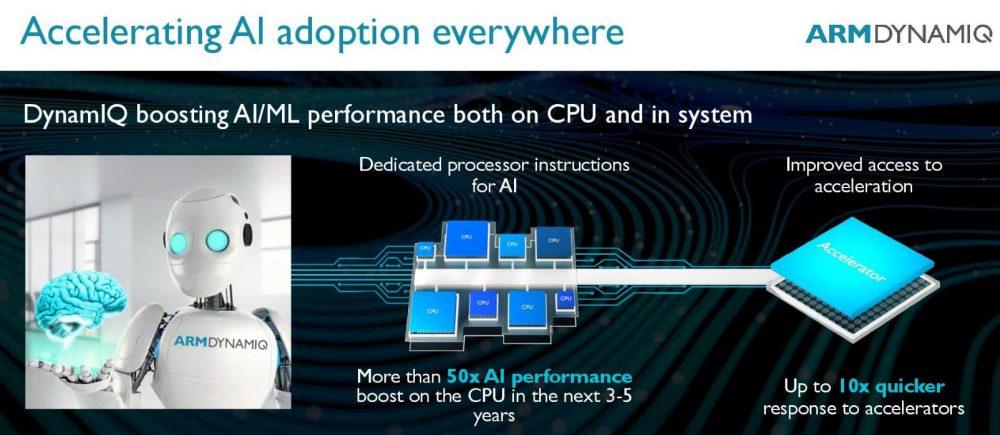

According to ARM, the objective of this architecture is to make it possible for their chips to be equipped with virtual reality and machine learning systems, and for this they have added more cores and a greater number of instructions (and this is precisely what ARM has always done ” weak “compared to x86, as its chips have much smaller and more specific instruction sets), delivering up to 50 times more power overall for AI tasks.

The underlying theme of DynamIQ is heterogeneous scalability; These two words hide a lot of jargon from the ecosystem, but as ARM predicts another 100 billion ARM chips will be sold in the next 5 years, they point to key areas such as automotive, artificial intelligence and machine learning at the interesting end of this growth. As a result, performance, scalability, and latency will be key metrics going forward that DynamIQ intends to enable.

One step beyond big.LITTLE

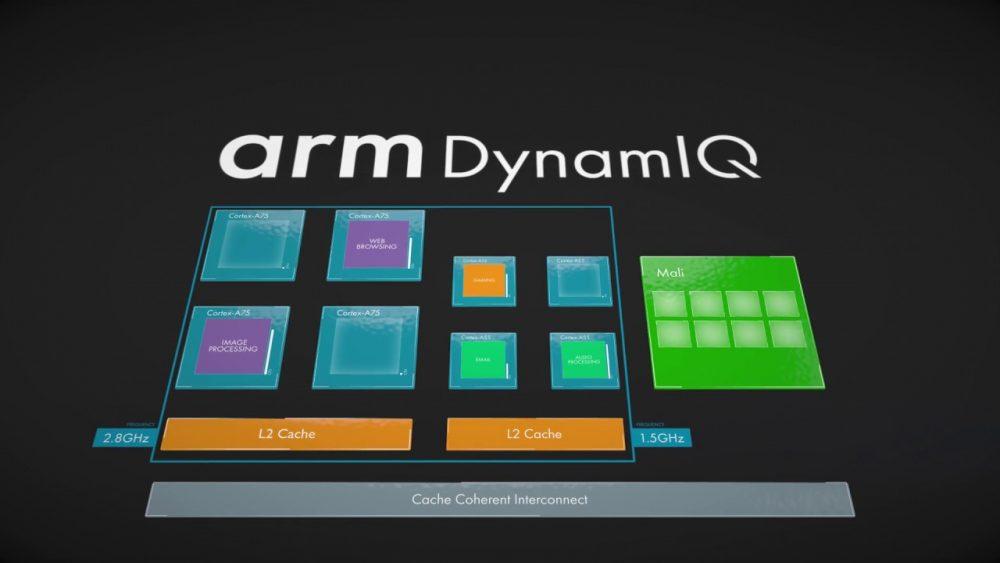

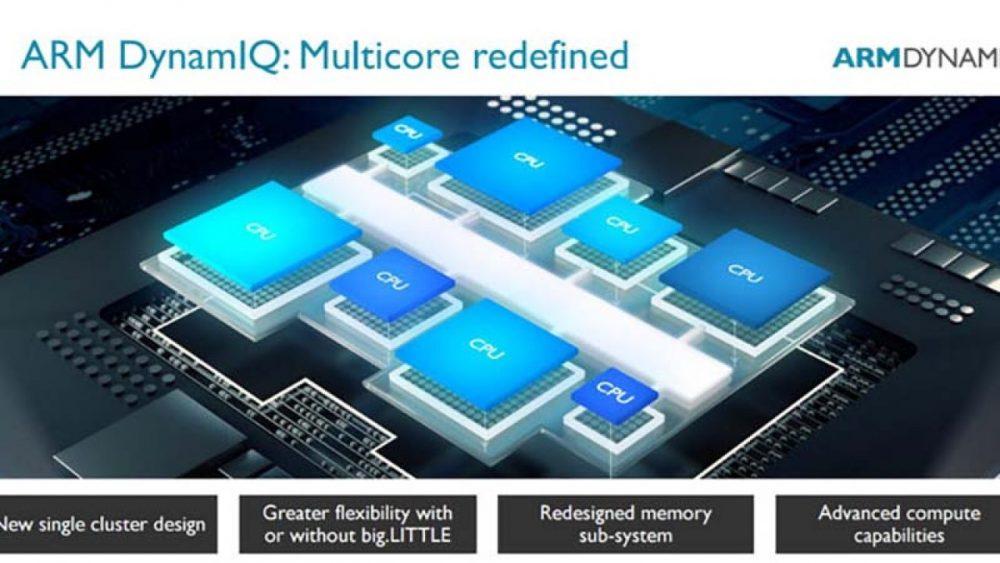

The first stage of DynamIQ is a larger cluster paradigm, which means up to eight cores for each of them. However, this means that there can also be a variable core design within a cluster; Those eight cores could be completely different from each other, and even from different Cortex-A families in different configurations.

The similarity with big.LITTLE is more than evident, only that instead of having “large nuclei” and “small nuclei”, here it would directly allow to have a defined number of nuclei and that each one of them was different from all the nuclei. others (this is the difference with big.LITTLE, really).

Many questions arise here, such as how the cache hierarchy will allow threads to migrate between cores within a cluster (perhaps similar to how threads migrate between big.LITTLE clusters today), even when the cores have different cache layouts. ARM hasn’t gone into this level of detail yet, so it’s still up in the air. Each variable-core configuration cluster will be part of a new fabric, with additional power-saving modes, and its goal is to provide much lower latency.

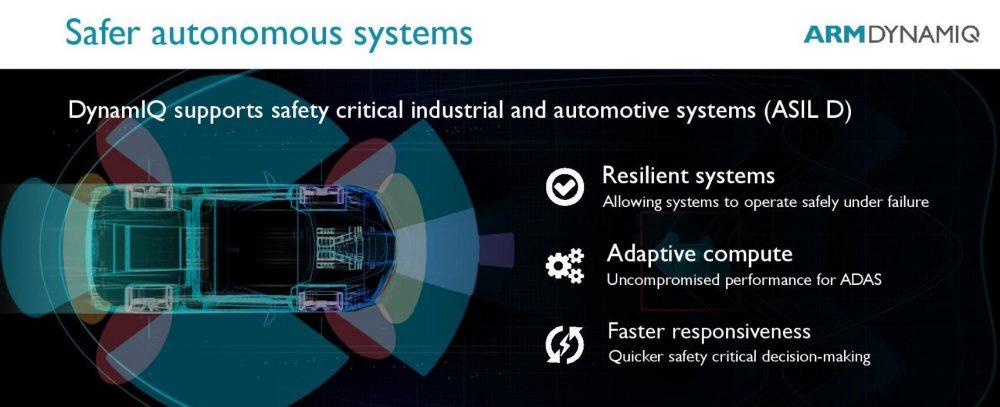

The underlying design also allows each core to be independently controlled for voltage and frequency, as well as power-saving sleep states. According to the slides provided by ARM, various other IP blocks such as accelerators, should be able to connect to this fabric and benefit from that low latency; items cited by ARM as safety critical automotive decisions could greatly benefit from this.

One of ARM’s main focus areas is redundancy. The new structure allows a seemingly unlimited number of clusters to be used, so that if one fails, the others can take its place. That said, the kind of redundancy that some of the ARM chip customers might need is failover in the event of physical damage, such as might happen in an autonomous car accident. It will be interesting to see if the vision of ARM with DynamIQ extends to that level of redundancy at the SoC level or if this type of implementation will depend on ARM partners.

Along with the new framework, ARM stated that a new memory subsystem design has been implemented to help with compute capabilities; however, nothing specific is mentioned. On the further computational line, ARM claims that new dedicated processor instructions (such as limited precision operations) for AI and Machine Learning will be integrated into a variant of the ARMv8 architecture.

We are not sure at the moment if this is an extension to ARMv8.2-A that introduced medium precision for data processing, or if it is a completely new version. ARMv8.2-A also adds RAS features and memory model improvements, which is consistent with the “new memory subsystem design” mentioned above. ARM has said that new cores will be needed to make processors with this architecture.

For now, ARM DynamIQ is focused on new and future technologies such as AI, automotive and mixed reality, although it is true that it is clear that DynamIQ can be used in other existing use models such as tablets, smartphones, PCs and servers. This will depend, yes, on how ARM makes it compatible with current core designs, since they could simply release it as a separate license.