Intel and AMD have been announcing the use of 3DIC technologies of all kinds to build future processors, a trend that will grow in the coming years. But how could future Intel and AMD CPUs built with this technology? In this article we will try to shed light on how these processors of the future could be.

As new manufacturing nodes are used, it can be seen how the costs grow more and more, this forces not only to take new strategies in terms of the design of new processors but also new ways of building them.

What do we understand as 3DIC?

3DIC is the acronym for a three-dimensional integrated circuit, which is the name given to all the processors or sets of the same that are made up of several different chips interconnected with each other making use of vias through silicon or TSV. So far in the PC hardware components market we have seen the 3D-NAND memory of different brands, as well as the different generations of HBM memory as only demonstrations

One of the advantages of the 3DIC is that we can use several chips with different manufacturing nodes in a combined way, this is an advantage because not all the elements of a processor need to be scaled to a new manufacturing node, since they do not provide a higher performance to them.

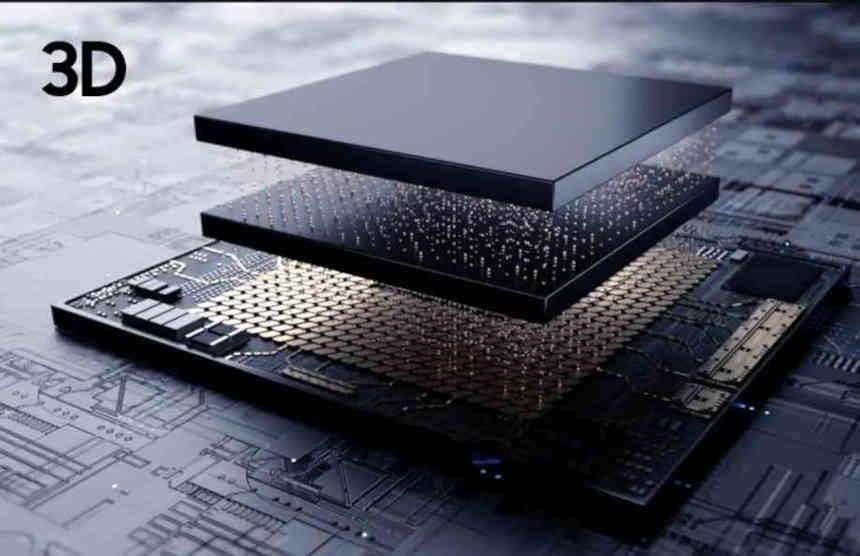

Direct die-to-die or how to build a complex processor using 3DIC

The idea of connecting two logic chips one-to-one in a 3DIC structure, making use of a vertical TSV interconnect, has the potential to completely change all sectors of the processor industry. From the very low-power SoCs that serve as the central processor in your phone to the high-end chips specialized in data centers.

The idea of separating a processor into two or more vertically aligned parts is something we have already seen in the Intel Lakefield, in which the CPU cores and the Northbridge are separated from the Southbridge on different chips and making use of manufacturing nodes. different. But, we should start looking at some models of SoCs and even CPUs.

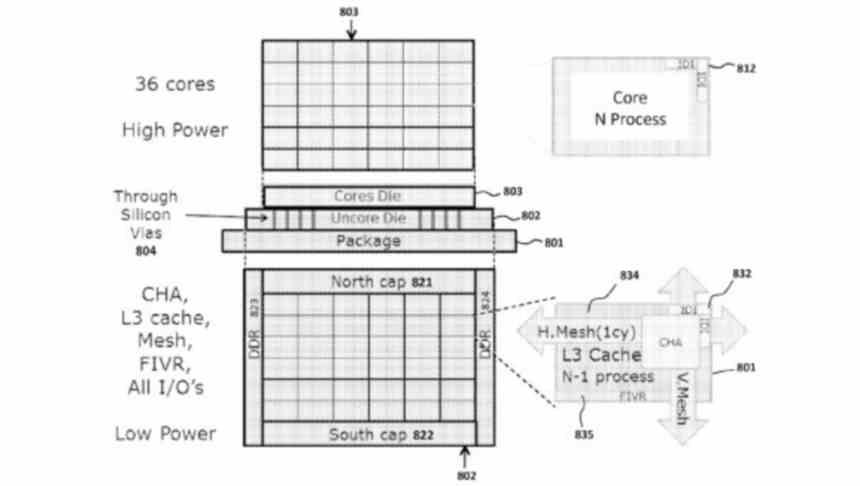

But Intel architecture is not the only way to build a contemporary CPU using 3DIC technology, but there is also another type of configuration, in which the CPU cores and the “uncore” of the same processor are separated into two or more different chips interconnected via TSV.

The biggest challenge facing CPU architects at the moment is the energy cost of data transmission in the processor, which in a configuration we are talking about is greatly reduced, hence the 3DIC not only going to be the future bet of Intel and AMD but it is also something that we are going to see in the ARM world.

A possible future 3DIC processor by Intel or AMD

For our example, we will take as an example the desktop processors based on Zen 2 and Zen 3, which divide the cores of the uncore, an element that is also known as Northbridge, although AMD calls it Scalable Data Fabric. We are going to use this architecture because it has a very clear division of the components.

AMD, or Intel, could release a future processor in which we would seemingly see a monolithic configuration, but really to be a 3DIC processor where the uncore is on a different chip in the stack than the different cores.

This would mean that the connectivity between the CCDs or Chiplets with the SDF would not only be more direct and therefore with less latency but would also consume less, thanks to the fact that it would be possible for AMD or Intel to use a greater number of pins at a lower speed, but without losing bandwidth to communicate the different cores with the rest of the processor, which in turn will allow to considerably increase the performance per watt of the different CPUs.

The idea of separating the processors into several levels will allow things like building multi-core systems that go beyond 8 cores on the same chip and intercommunicating all of them at a sufficient speed, with good latency and consuming very little energy compared to current models.

What handicaps do Intel and AMD face in deploying the 3DIC?

The major trade-off is the enormous cost of making a 3DIC processor, which requires additional manufacturing steps, but the biggest trade-off is what is called thermal stalling, which occurs when two components are so close that the temperature of one. it affects the performance of another, not allowing components to reach the clock speeds that they could achieve separately and even in a 3DIC configuration.

This makes these configurations also require much more complex and expensive cooling systems, which together takes them away from home systems and makes them ideal for servers of all kinds, but paradoxically they are also the future of SoCs for PostPC devices, They are limited in size and cannot expand more horizontally, so they can only do so vertically.

The reason for this is that with each new node not only is the cost of each wafer millimeter squared increasing but it is also increasingly difficult to build larger and larger processors without a dangerous failure rate. All of this will force most designs to go from being one huge monolithic chip to being made up of several vertical chips, just because the cost per wafer will be so high that even the high cost of 3DIC manufacturing will not be an impediment.