We always talk about new lithographic processes and improvements, those that take hardware to the next level. But we do not usually talk about the problems that companies like TSMC or Intel itself have to face to keep moving forward and innovating. Now that the Taiwanese have reached mass production of their 5nm and are about to start at 3nm, it is a good time to understand the main obstacles they have faced.

A given chip has to face a number of problems when it is introduced into a high performance product. From heat to varied vibrations, through the frequencies it reaches, everything becomes more and more complex to work precisely because reducing transistors and increasing node density requires inspecting, measuring, and testing each chip in a more complex way, that is, each lithographic jump adds certain problems.

The 5nm as a successor to the 7nm represents only some important changes

Chief among them is that the transistor fin itself must be physically stronger. Reducing the size of each end and gate requires a series of larger vertical layers if the typical FinFET transistors are maintained .

Fins and gates lengthen, get taller, so the amount of materials and their deposit of them is crucial to keep the current flow uniform in the three walls of said door. We could think that by increasing the height it is possible to pass a greater vertical current flow in each transistor, but the truth is that the ratio of width and height is the key to increasing its performance, since the proportions are not equivalent to performance .

This incurs a control problem on the fabs to ensure that the transistor engraving process is correct. To try to avoid this, artificial intelligence is being used through machine learning to detect certain problems before the wafer has finished certain vital processes, so that it is known in advance if it is a wafer predisposed to failure.

The second problem facing 5nm is curious, since it is the excess of data from the wafer and chip itself. Here again, Deep Learning takes the lead, since it is able to determine by means of machine vision images and with certain algorithms the problems and points of interest where engineers must focus to improve the manufacturing process of the node.

This fact has caused a shortening of the effective delivery times of this 5 nm lithographic process, since thanks to deep learning TSMC was able to see and anticipate where the most serious problems were without having to waste huge amounts of hours based on evidence and wafer engraving errors.

The 3nm could be the paradigm shift for the new generation of nodes

If the 5 nm have forced the transistors to be lengthened vertically in order to group them horizontally in greater numbers and thereby increase the density of the node, the 3 nm will represent more important changes.

Although not confirmed by TSMC, NVIDIA and AMD may have to redesign their architectures for engravings, as Taiwanese are more than likely to go the Samsung path and replace FinFET transistors with GAA or Gate-all-around .

The preventive intention is not this, since that would imply a drastic change, starting with the blank masks and ending with a new type of engraving and lenses. Furthermore, what little is known is that even if TSMC managed to keep FinFETs for one more generation, the new transistors will require new materials in the wafers, such as cobalt or ruthenium.

As if that were not enough, the films and layers should be thinner to favor the electrical transfer of current, but this implies that they will be more difficult to clean, polish, measure and, of course, inspect. As if that were not enough and given another curious paradigm, a digital logic of a smaller chip in its transistors they acquire a more analogous behavior.

New materials and functionality of each transistor

If we add this to the new materials that will define the fins and the gates, we will find some of the problems of yesteryear, but multiplied in terms of difficulty in solving them. Energy leaks, structural weaknesses, unmeasured stresses and of course higher inductance will be some of the problems facing all companies in the industry, not just TSMC as a wafer manufacturer.

The key data will be in the functionality of each transistor. Formerly when a transistor died it stopped working, same case if it was damaged. Currently this does not happen due to the manufacture and design of the same: it will continue to work, but with a lower performance which, if expanded, reduces the set of them to a lower level.

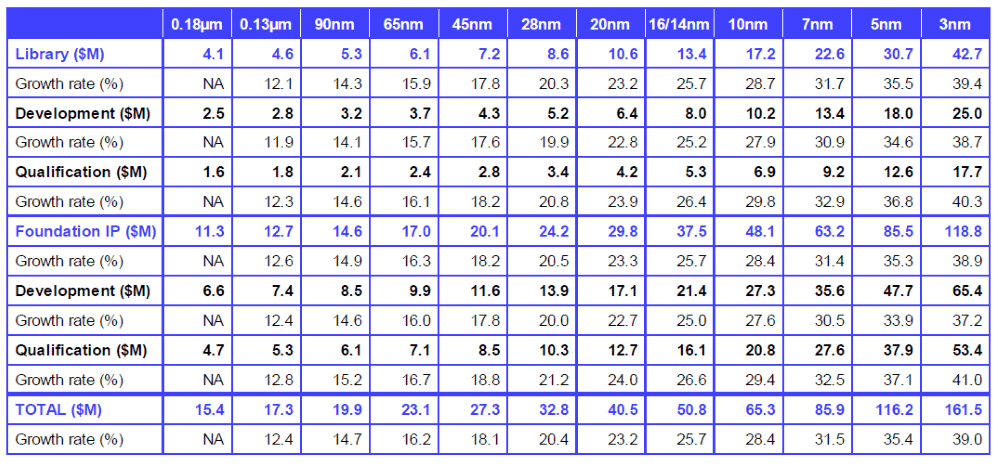

Therefore, the perfect functionality of transistors is key in the industry and involves billions of dollars in research, prevention and detection of errors, something that in the 3 nm will be key if you want to increase the performance of each chip. It’s funny how the industry is turning. The difficulty of a node is not so much to obtain functional wafers, but to make sure that these wafers obtain the rate of performance and reliability that are intended and for which they were designed, there is currently the challenge, because a wafer with a high density for chip if the final performance of these is below its predecessor.

The next challenge will be the atom as such and from there an incredible field opens up where silicon may only be the basis of a series of molecular compounds that allow it to reduce its size below the atom, something truly incredible.