In the past, a marketing strategy of processor manufacturers ( Intel and AMD ) as well as motherboard manufacturers was to count the PCIe lanes offered by their platform, and even today many continue to do so. However, at present this has stopped making sense because they are no longer a limiting factor, and in this article we are going to explain why.

The number of PCIe lanes on a processor has always had to do with which lanes come directly from the PCIe root, offering full bandwidth and the lowest possible latency for the processor. In modern systems this is already built into the processor, while in older systems it had to do with the Northbridge; According to this metric, a standard Intel processor has 16 lanes, an AMD Ryzen has between 16 and 20, an Intel HEDT has 28/44 depending on the model, and an AMD Threadripper has up to 60. What is all this for?

What is the use of counting the PCIe lanes?

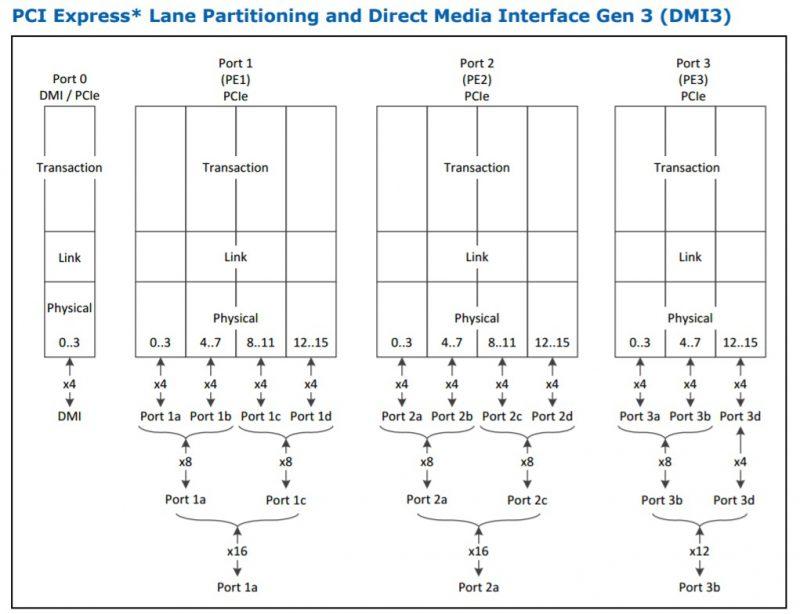

Intel’s technical documentation explicitly lists what is available on the processor through the PCIe root complexes: here, 44 lanes come from two batches of sixteen and a complex of twelve lanes. The DMI3 link to the chipset is on all but one of the PCIe 3.0 x4 links, but is not included in that total.

The number of PCIe lanes on a chipset is a bit different. Chipsets are PCIe switches for all practical purposes, as using a limited bandwidth uplink, it is designed to carry traffic from low bandwidth controllers (such as SATA, Ethernet, or USB). For its part, AMD has limitations in this regard because it has spent more time trying to re-enter the performance race against Intel than developing new technologies, and for that it has outsourced to ASMedia, in fact.

Intel has been increasing its support for PCIe 3.0 lanes in its chipsets for at least three generations, and now supports 24 PCIe 3.0 lanes. There are some caveats as to which lanes which drivers can support, but generally we consider these 24 the manufacturer says.

Due to the shared uplink, the PCIe lanes coming from the chipset (for both AMD and Intel) can be blocked very easily, as well as being limited to PCIe 3.0 x4. The chipset introduces additional latency to operation compared to having the controller connected directly to the processor, so we rarely see important hardware (GPU, RAID controllers, FPGAs, etc.) connected to them.

The combination of the two lends itself to a wide variety of platform functions and configurations. For example, the AMD X399 platform that has 60 lanes from the processor has the following “recommended” settings:

| Use | PCIe lanes | Total | |

|---|---|---|---|

| Content creator | Use 2 x Pro GPUs 2 x M.2 Cache Drives 10G Ethernet 1 x U.2 Storage 1 x M.2 OS / Apps 6 x SATA Local Backup |

PCIe x16 / x16 from CPU lanes x4 + x4 from CPU x4 from CPU x4 from CPU x4 from CPU from the Chipset |

Total 52 lanes |

| Extreme pc | Use 2 x Gaming GPUs 1 x HDMI Capture Card 2 x M.2 for Games / Stream 10G Ethernet 1 x M.2 OS / Apps 6 x SATA Local Backup |

PCIe x16 / x16 from CPU lanes x8 from CPU x4 + x4 from CPU x4 from CPU x4 from CPU from the Chipset |

Total 56 lanes |

| Streamer | Use 1 x Gaming GPU 1 x HDMI Capture Card 2 x M.2 Stream / Transcode 10G Ethernet 1 x U.2 Storage 1 x M.2 OS / Apps 6 x SATA Local Backup |

PCIe x16 from CPU lanes x4 from CPU x4 + x4 from CPU x4 from CPU x4from CPU x4 from CPU from the Chipset |

Total 40 lanes |

| Rendering farm | Use 4 x Vega FE Pro GPUs 2 x M.2 Cache Drives 1 x M.2 OS / Apps 6 x SATA Local Backup |

PCIe x16 / x8 / x8 / x8 lanes x4 + x4 from CPU x4 from CPU From Chipset |

Total 52 lanes |

What has started to happen is that companies are combining CPU and chipset PCIe lane counts to promote more of them, and this is despite the fact that not all lanes are the same or offer the same performance. . This matters very little to manufacturers, because you already know that the “war of numbers” (see who offers the highest number of something, whatever it is) is something common in marketing, whose only objective is to sell more. As a result, Intel is also promoting its Skylake-X processors with 68 PCIe lanes, whose metrics are similar to what we have shown for AMD’s X399.

PCIe lane metric is misleading

Counting the number of PCIe lanes on a PC platform is misleading for the simple fact that they are not all the same or serve the same purpose, and that in the best of cases because on many occasions we have even seen falsified data (especially given the history of how this metric has been provided in the past). The fact that a number is larger / smaller than what a provider expected does not give them the right to redefine it and mislead consumers, right?

To cite a precedent: In the smartphone space, around 2016 vendors counted just about anything on the main processor as an additional core to provide a “full core count.” This meant that the CPU segments became “cores” as well as specific IP blocks for signal and image processing or IP blocks for security, causing quad-core processors to be sold as deca-core as if such thing.

It was absurd to hear or read that a smartphone processor had fifteen cores, when the main general-purpose cores of the processor were a quartet of ARM Cortex A7 designs. Users who follow the evolution of the mobile phone industry will have realized that this nonsense fortunately stopped quite quickly, since it was illogical to count anything as a processor core, and if we had continued in this vein today we would have reached the absurdity of smartphone processors with 40 cores.

The same thing is starting to happen with PCIe lanes: if AMD, Intel, and motherboard manufacturers start counting any lane and of any kind in their metrics, this will no longer make any sense.