Although PCIe 4.0 has just landed with us and not even NVIDIA is up to date with its gaming graphics, it just so happens that the top three brands in the market for desktops and servers as well as HPC are waiting for their next PCIe 5.0 release as may. Why so much speed in wanting to implement it? What reasons push the three to want to include their characteristics?

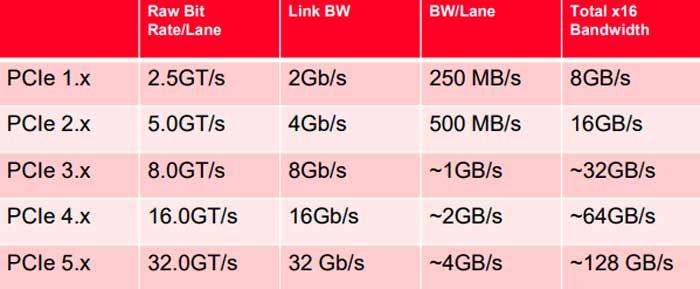

It is necessary to take into account in the first place and to understand the requirements of each other that PCIe 5.0 is a very important leap compared to its predecessors and that the big three have their eyes set beyond gaming.

![]()

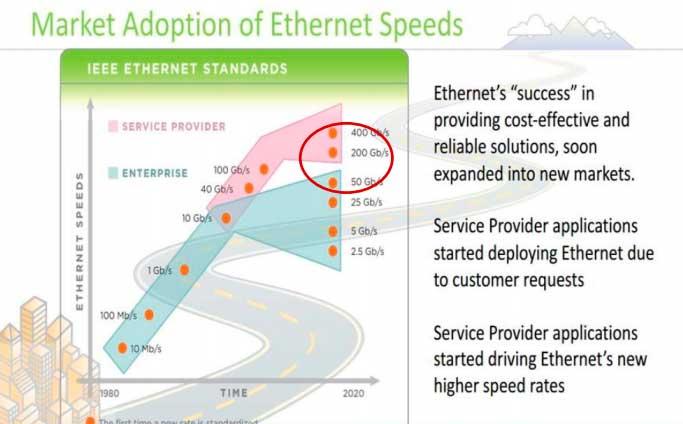

High-end network solutions with 400 Gb Ethernet or dual 200 Gb / s InfinityBand , accelerators and GPUs, but above all being able to have continuous use of L1 substates for lower power consumption are some of these improvements that They wait, but for this we must understand the improvements that this new bus will bring.

PCIe 5.0: news and features

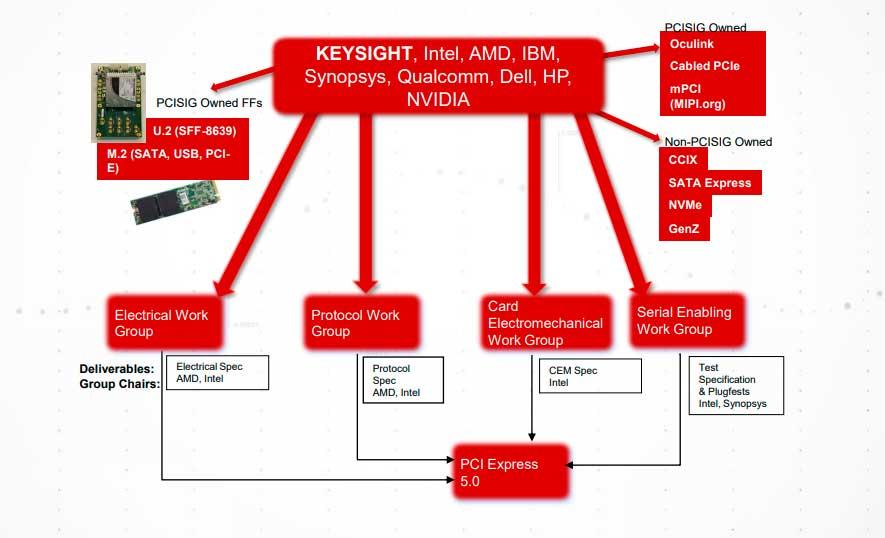

If we look at the original roadmap for this standard we will see that, at the very least, it will be introduced two years late, where PCIe 5.0 drags the backwardness of its predecessor version 4.0. In principle, it will arrive at some point in 2021, where PCISIG ordered the first revision as a draft at the end of 2019 where the bases of said standard were established.

The main novelties of this version and for what it is so expected are:

- Improved SMT connector.

- Same pinout as its previous versions.

- Signal duplication up to 32 GT / s.

- You only need to enable speed reduction to meet the specifications.

- EIEOS.

- Improvements in data rate bits.

- Permanent coding 128/130.

- Loss bugets between 35 and 36 dB.

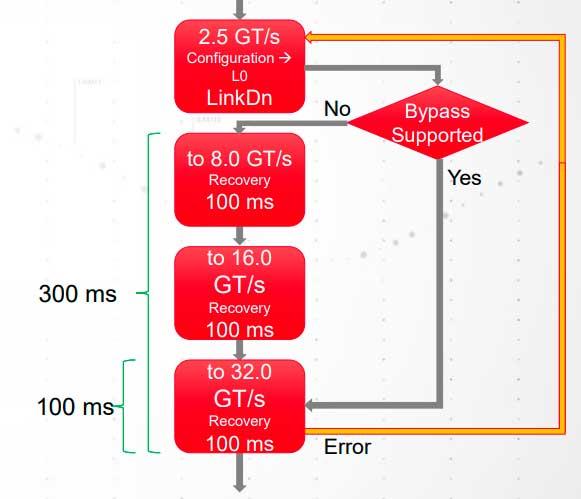

- Equalization 8 GT -> 16 GT -> 32 GT / s.

- Scaled Flow Control.

In addition to this, we cannot forget the retro compatibility with all previous versions of PCIe, but if we focus it on networks and FPGAs, the improvements do not end there:

- BER 10e-12.

- TX Presets P0-P10.

- Same approach for TX and RX in Gen 4.

- Same TX voltage and jitter parameters as Gen4.

The topology of each channel, key in adoption and speed

The first thing we must understand is that all companies currently need and in the near future is speed. It is the main claim of PCIe 5.0, but for this they will all have to adapt to certain criteria in the topology that will determine more demand in each channel.

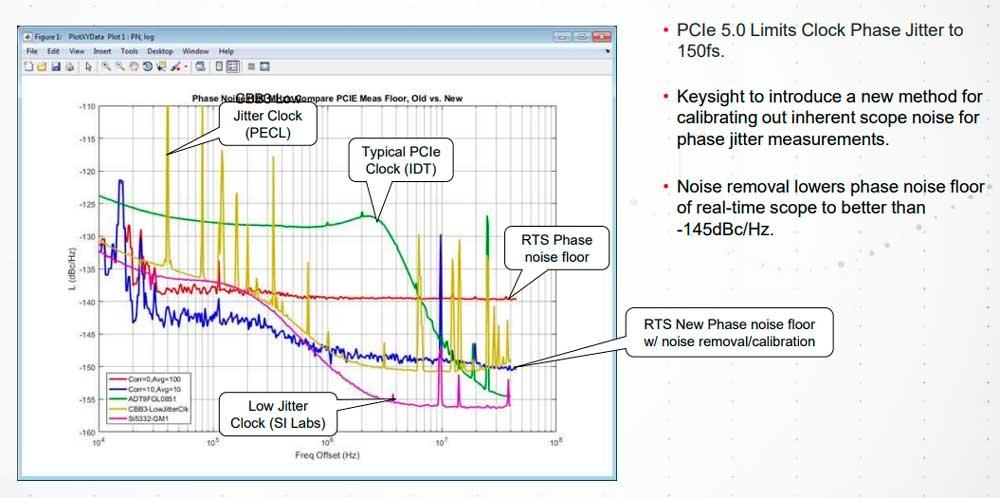

Thus, PCIe 5.0 specifies a shorter channel with a 50 ohm termination for jitter measurements, where in addition the lower limit of the PLL bandwidth is set to just 0.5 MHz for 16 GT / s.

This is vital for AI and ML systems, which process large amounts of data and, as we know, the market has been expanding abruptly in recent years and nothing suggests that it will not continue this way. With daily data rates of around 4TB, it is understandable that more bandwidth is needed.

If we add to this the use of CXL or CCXI as new interconnection methods between coherence devices, we can get an idea of where the market is currently and what the future of the industry will be. As for the desktop, the big three are currently surpassed in terms of speed with PCIe 4.0.

Ampere G100 isn’t even expected to be able to fill bandwidth completely, so gaming graphics is more than likely to continue in Gen4 for quite a few years, at least until PCIe 5.0 is more affordable driven by industry demand.