As you know, the chips that we use in our day to day, such as PC processors, are made up mostly of transistors , transistors that, following Moore’s law, are getting smaller and smaller in order to increase the density (put a greater number in same space), but engineers have been struggling for some time to do this. Intel has what seems to be the solution: transistors stacked on nanoplates , and in this article we are going to tell you what it consists of and how, thanks to this, they will not only maintain but extend Moore’s law for a long time.

Moore’s law tells us that approximately every two years the number of transistors in a microprocessor doubles, and to do this, what has been done for decades is to reduce the size of these transistors, whose size is on the order of nanometers . However, it is increasingly difficult to make them smaller and in order to continue integrating more in the same space, they have had to look for alternative techniques like the one we are going to tell you about today.

What are Nanoplate Stacked Transistors?

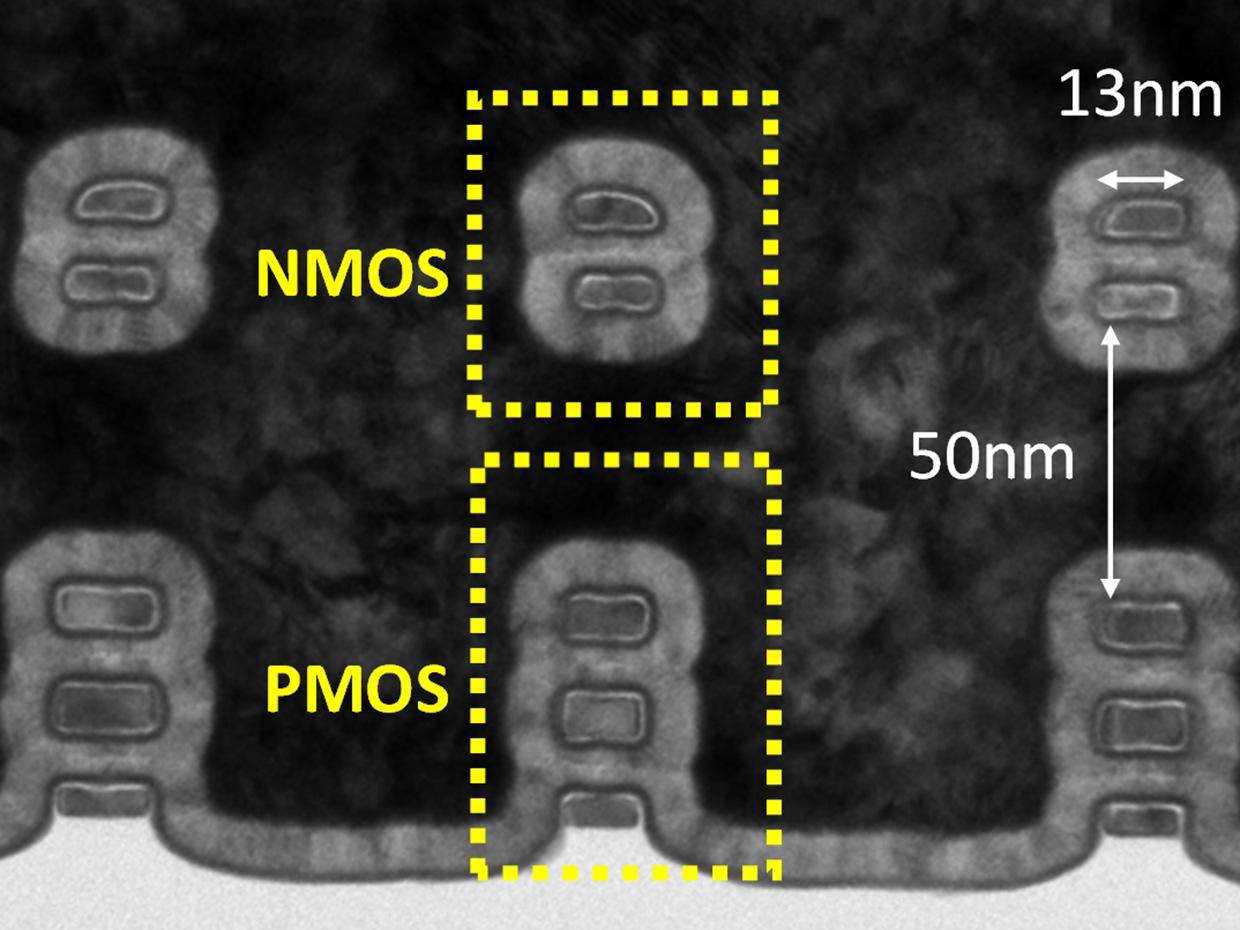

The logic circuits behind almost all digital devices today are based on a pairing of two types of transistors: NMOS and PMOS. The same voltage signal that turns one of them on turns off the other, and putting them together means that electricity should flow only when one bit changes in value, greatly reducing power consumption.

These pairs have been sitting side by side for decades, but if electronic circuits are to keep shrinking they will have to get even closer. Now Intel has shown a different approach to how to position the transistors: stacking one on top of the other. The scheme effectively cuts the space that transistors take up in a simple CMOS circuit in half, meaning that the density of transistors a chip has can be easily doubled .

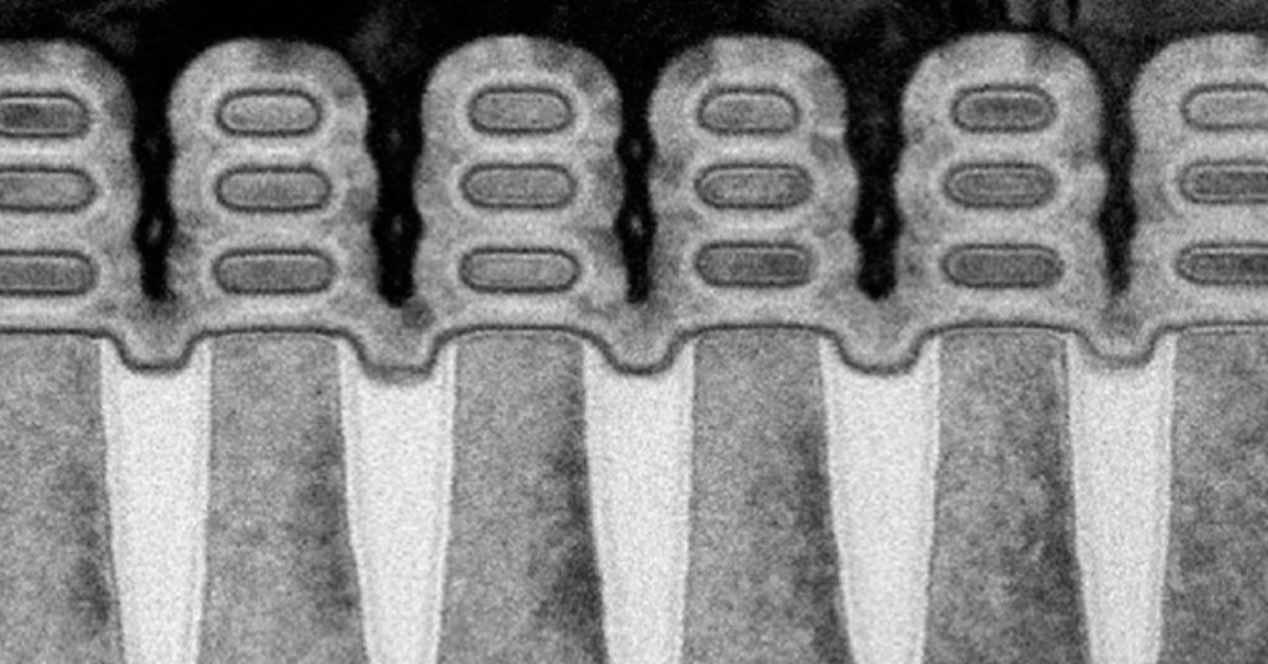

The scheme begins by using what is widely accepted as the next-generation transistor structure, variously named: nanoplates, nanosheets, nanoribbons, nanowires … or simply GAA (gate-all-around). Instead of the main part of the transistor consisting of a vertical silicon fin as is done today, the channel region of the nanoplate consists of multiple horizontal nano-thick sheets stacked on top of each other (you can clearly see this in the image above).

How is this type of circuit implemented?

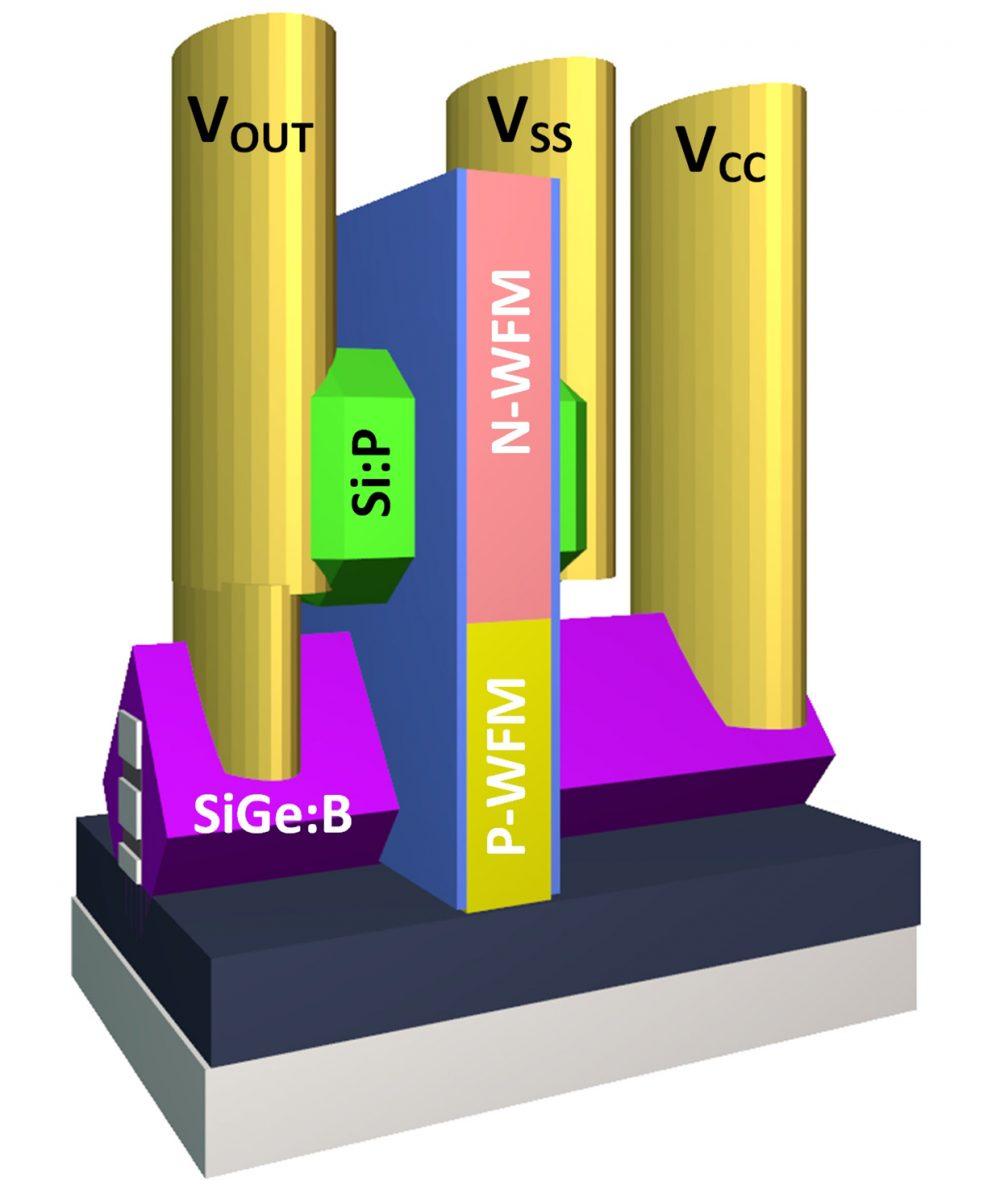

Intel engineers used these devices to build the simplest CMOS logic circuit – an inverter. It requires two transistors, two power connections, one input and one output interconnect. Even when the transistors are placed side by side as is done today, the arrangement is very compact, but by stacking the transistors and adjusting the interconnects the area is cut in half.

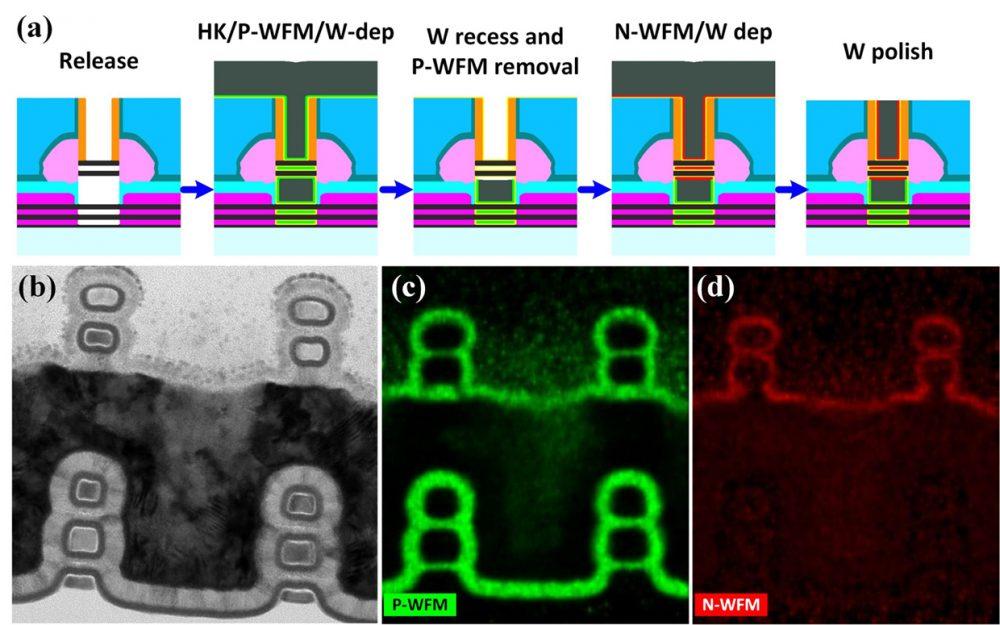

Intel’s recipe for creating these nanoplate-stacked transistors is called a self-aligning process because it builds both devices during the same production step. That’s important because adding a second step, say by building two separate wafers and then putting them together, could lead to misalignments that would destroy the circuit.

In essence, the process is a modification of the steps involved in manufacturing nanoplate transistors. It begins with repeating layers of silicon and silicon germanium, which is then carved into a tall, narrow fin, and the silicon germanium is etched to leave a suspended array of silicon nanoplates. Normally, all nanoplates would go on to form a single transistor, but here the top two nanoplates are connected to phosphor-doped silicon in order to form an NMOS device, and the bottom two to boron-doped silicon germanium to produce PMOS .

The full “integration flow” is, of course, more complicated (you can see it in the image above), but Intel researchers have worked to keep it as simple as possible (according to Robert Chau, director of component research at the company). Once they have mastered the fabrication technique, which is where they are now, the next step will be to go after the performance.

EWs likely that will involve upgrading PMOS devices, which are currently lagging behind NMOS in their ability to drive current. The answer to that problem is introducing voltage into the transistor channel, according to Chau. The idea is to distort the lattice of the silicon crystal in such a way that the charge carriers (holes in this case) pass faster. Intel already introduced tension in its devices in 2002, and in several research documents the company has already shown that it is possible to produce compressive and tensile stress in nanoribbon transistors.

Other research organizations are also working on nanoplate stacked transistor designs, although they are sometimes called complementary FETs or CFETs. The Belgian organization Imec pioneered the CFET concept and reported on its construction as early as 2019, but the Imec components were not made entirely from nanoplate transistors instead the lower layer consisted of a FinFET and the upper part a single plate. . In Taiwan they also reported the production of a CFET structure that has a single nanometer sheet for PMOS and NMOS (in contrast, Intel’s has a two-board NMOS on top of a three-board PMOS, with an aspect that is probably closer to of this concept of stacked transistors).