Intel ed AMD hanno annunciato l'utilizzo di tecnologie 3DIC di ogni tipo per costruire futuri processori, una tendenza che crescerà nei prossimi anni. Ma come potrebbero le future CPU Intel e AMD costruite con questa tecnologia? In questo articolo cercheremo di far luce su come potrebbero essere questi processori del futuro.

Man mano che vengono utilizzati nuovi nodi di produzione, si può vedere come i costi crescano sempre di più, questo costringe non solo ad adottare nuove strategie in termini di progettazione di nuovi processori ma anche nuovi modi per costruirli.

Cosa si intende per 3DIC?

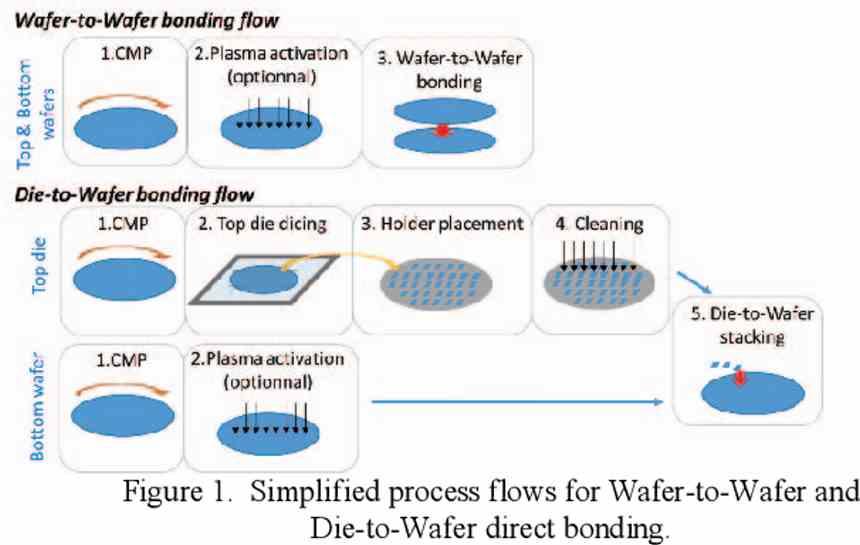

3DIC è l'acronimo di un circuito integrato tridimensionale, che è il nome dato a tutti i processori o insiemi dello stesso che sono costituiti da più chip diversi interconnessi tra loro facendo uso di via tramite silicio o TSV. Finora nel mercato dei componenti hardware per PC abbiamo visto la memoria 3D-NAND di diverse marche, così come le diverse generazioni di memorie HBM come solo dimostrazioni

Uno dei vantaggi del 3DIC è che possiamo utilizzare più chip con diversi nodi di produzione in modo combinato, questo è un vantaggio perché non tutti gli elementi di un processore devono essere scalati su un nuovo nodo di produzione, poiché non forniscono una prestazione superiore a loro.

Die-to-die diretto o come costruire un processore complesso utilizzando 3DIC

L'idea di collegare due chip logici uno a uno in una struttura 3DIC, utilizzando un'interconnessione TSV verticale, ha il potenziale per cambiare completamente tutti i settori dell'industria dei processori. Dai SoC a bassissima potenza che fungono da processore centrale nel telefono ai chip di fascia alta specializzati nei data center.

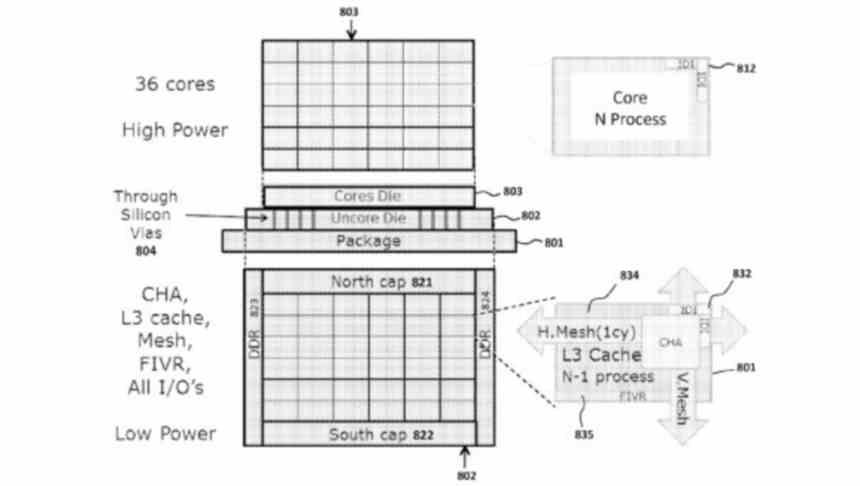

L'idea di separare un processore in due o più parti allineate verticalmente è qualcosa che abbiamo già visto nell'Intel Lakefield, in cui il CPU core e il Northbridge sono separati dal Southbridge su chip diversi e facendo uso di nodi di produzione. diverso. Ma dovremmo iniziare a guardare alcuni modelli di SoC e persino CPU.

Ma l'architettura Intel non è l'unico modo per costruire una CPU contemporanea utilizzando la tecnologia 3DIC, ma esiste anche un altro tipo di configurazione, in cui i core della CPU e "uncore" dello stesso processore sono separati in due o più chip diversi interconnessi tramite TSV.

La sfida più grande che devono affrontare gli architetti di CPU al momento è il costo energetico della trasmissione dei dati nel processore, che in una configurazione di cui stiamo parlando è notevolmente ridotto, quindi il 3DIC non sarà solo la scommessa futura di Intel e AMD, ma lo è anche qualcosa che vedremo nel ARM mondo.

Un possibile futuro processore 3DIC di Intel o AMD

Per il nostro esempio, prenderemo come esempio i processori desktop basati su Zen 2 e Zen 3, che dividono i core dell'uncore, un elemento noto anche come Northbridge, sebbene AMD lo chiami Scalable Data Fabric. Useremo questa architettura perché ha una divisione molto chiara dei componenti.

AMD, o Intel, potrebbe rilasciare un futuro processore in cui apparentemente vedremmo una configurazione monolitica, ma in realtà essere un processore 3DIC in cui l'uncore si trova su un chip diverso nello stack rispetto ai diversi core.

Ciò significherebbe che la connettività tra i CCD o Chiplet con SDF non solo sarebbe più diretta e quindi con minore latenza ma consumerebbe anche meno, grazie al fatto che sarebbe possibile per AMD o Intel utilizzare un numero maggiore di pin ad una velocità inferiore, ma senza perdere banda per comunicare i diversi core con il resto del processore, il che a sua volta consentirà di aumentare notevolmente le prestazioni per watt delle diverse CPU.

L'idea di separare i processori in più livelli permetterà cose come costruire sistemi multi-core che vanno oltre gli 8 core sullo stesso chip e comunicarli tutti ad una velocità sufficiente, con una buona latenza e consumando pochissima energia rispetto ai modelli attuali.

Quali handicap devono affrontare Intel e AMD nell'implementazione del 3DIC?

Il principale compromesso è l'enorme costo di realizzazione di un processore 3DIC, che richiede ulteriori fasi di produzione, ma il più grande compromesso è quello che viene chiamato stallo termico, che si verifica quando due componenti sono così vicini alla temperatura di uno. influisce sulle prestazioni di un altro, non consentendo ai componenti di raggiungere le velocità di clock che potrebbero raggiungere separatamente e anche in una configurazione 3DIC.

Questo fa sì che queste configurazioni richiedano anche sistemi di raffreddamento molto più complessi e costosi, che insieme le portano lontano dai sistemi domestici e le rendono ideali per server di ogni tipo, ma paradossalmente sono anche il futuro dei SoC per dispositivi PostPC, hanno dimensioni limitate e non possono espandersi più orizzontalmente, quindi possono farlo solo verticalmente.

La ragione di ciò è che con ogni nuovo nodo non solo aumenta il costo di ogni wafer millimetro quadrato, ma è anche sempre più difficile costruire processori sempre più grandi senza un pericoloso tasso di guasto. Tutto ciò costringerà la maggior parte dei progetti a passare dall'essere un enorme chip monolitico all'essere composto da diversi chip verticali, solo perché il costo per wafer sarà così alto che anche l'alto costo della produzione 3DIC non sarà un impedimento.