Yesterday we talked about the advantages that Intel had over AMD, where one of the sections was precisely that of innovation. Proof of this is what was presented by Intel for its 3D stacking technology, which will form the high-performance chips of the future, not without problems of course. The company seems to have found the solution to almost all the problems that this technology entails through what it has called Intel ODI.

Before going into the matter of explaining what this technology consists of, we must understand what have been the reasons that have led Intel to develop it, what have been the problems and where were the limitations.

Only in this way can we understand the complexity of this whole matter and how the company has managed to solve these problems in a very intelligent way.

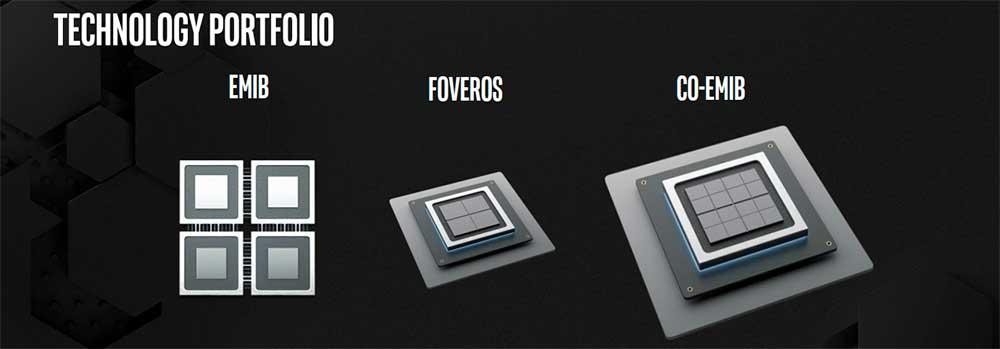

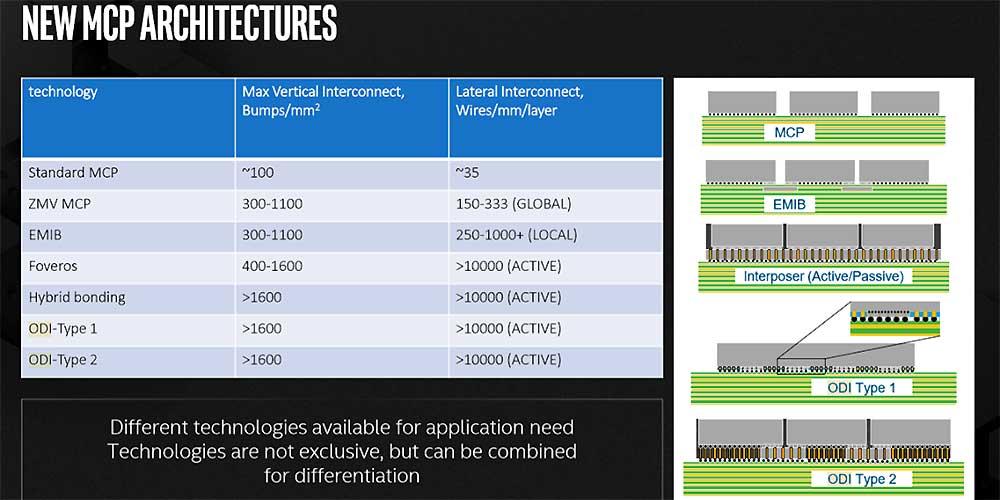

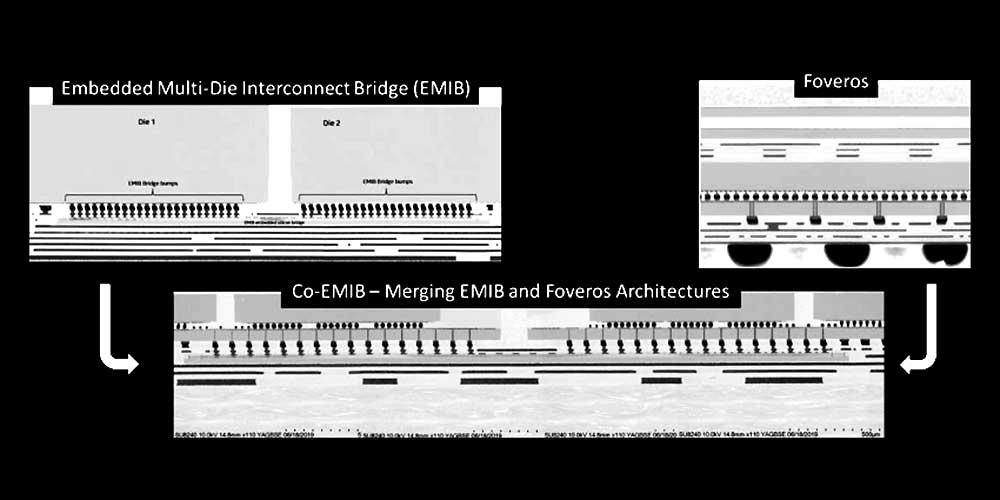

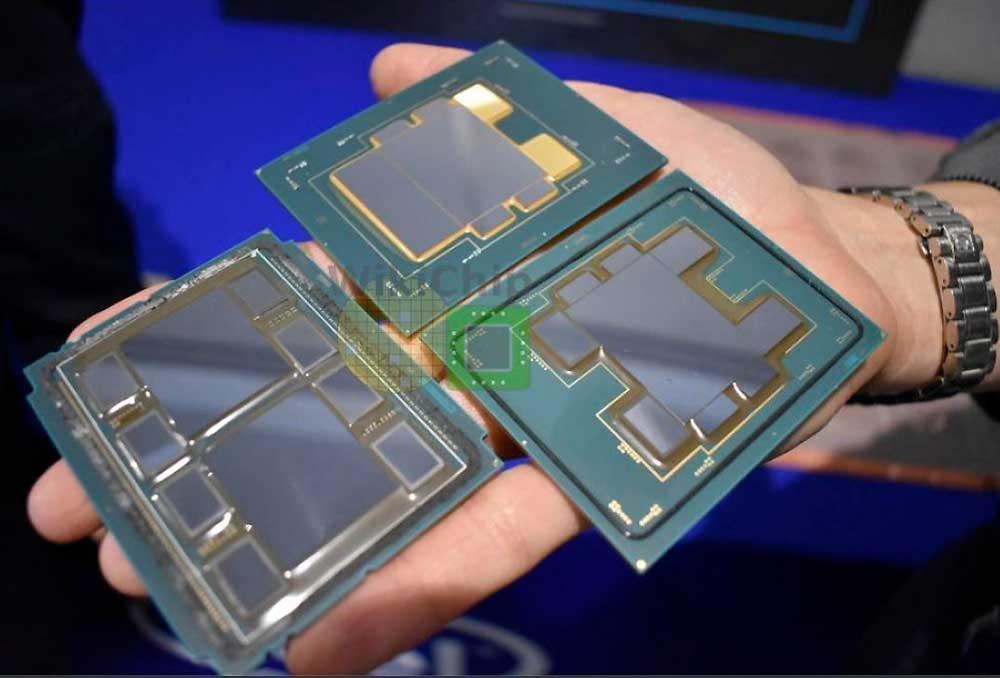

First of all, and to make a mental scheme, Intel currently works with three different stacking technologies that range from least to most complex: EMIB, Foveros and CO-EMIB.

The first is the so-called 2.5D technology, the second is the first real 3D generation, while the latter combines both to offer much more complex products. Although we have already seen them separately, we will make a quick review of all of them to situate ourselves again.

Intel EMIB

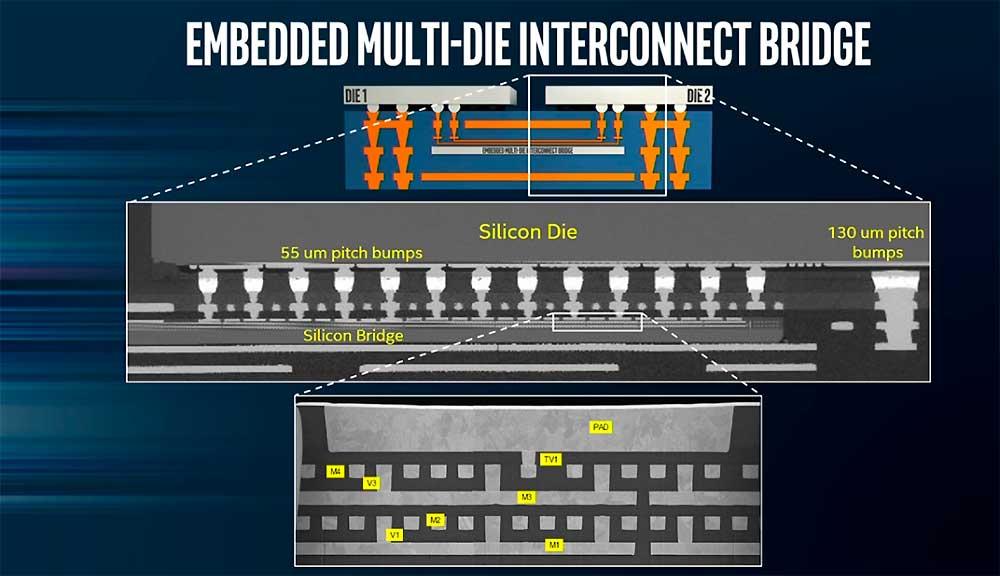

Acronym for Embedded MultiInterconnect Bridge, it is a 2.5D system that is already familiar to us, since it debuted with Kaby Lake G and included an Intel die with its corresponding cores, cache, registers etc …, a die belonging to AMD through an RX Vega M and a 4GB HBM2 stack, all in a single interposer that was soldered to laptop motherboards.

EMIB is therefore a medium-scale interconnect technology that allows you to extract the full performance of each chip that is included in the interposer.

Intel Foveros

It is the first step in the revolution that we will witness, real 3D stacking. This is nothing more than interconnecting various die vertically, one on top of the other, instead of horizontally as it has been done until now.

It is what Intel calls Face-to-Face and represents a series of quite interesting and at the same time somewhat logical problems. The first is an electrical problem, since it is necessary to bring enough energy to the upper die and to do this, it is necessary to go through the intermediate one / s. This was partially solved with the TSV calls, but these are reluctant to supply large amounts of voltage and although adding more this can be solved, there is the problem that the most expensive of a 3D chip at present is precisely adding TSV of quality and volume.

Finally, Intel faces a temperature problem. The upper die can be refrigerated, but at the same time it represents a thermal resistance for the lower ones, since at each vertical die the upper one obstructs the transfer of heat and generates a chain problem.

Intel CO-EMIB

It is basically a merger, to call it in some colloquial way, between EMIB and Foveros. It is a 3D stacking where the horizontal length is used and therefore alleviates in some way the problems of both, but does not solve them.

So Intel had to come up with a new technology that was compatible with all three of its packaging models and at the same time put an end to all the problems we’ve talked about, and this is precisely where ODI comes in.

Intel ODI

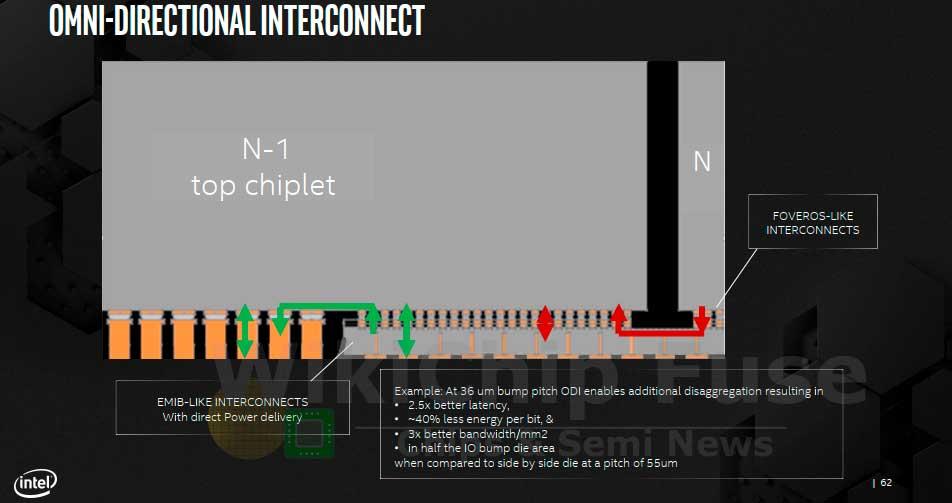

ODI is the acronym for Omni-Directional Interconnect and it is not a technology in itself, but a group of them, that is, ODI encompasses a series of specific solutions that may increase over time or evolve as such.

Its main function is based on power delivery and aims to end the problems of EMIB and Foveros, since doing this by default ends the problems of CO-EMIB.

Everything is based on what Intel calls 3D packaging Flows , which are nothing more than internal interconnection pathways to improve the arrival of energy and at the same time improve heat dissipation with a single type of technology.

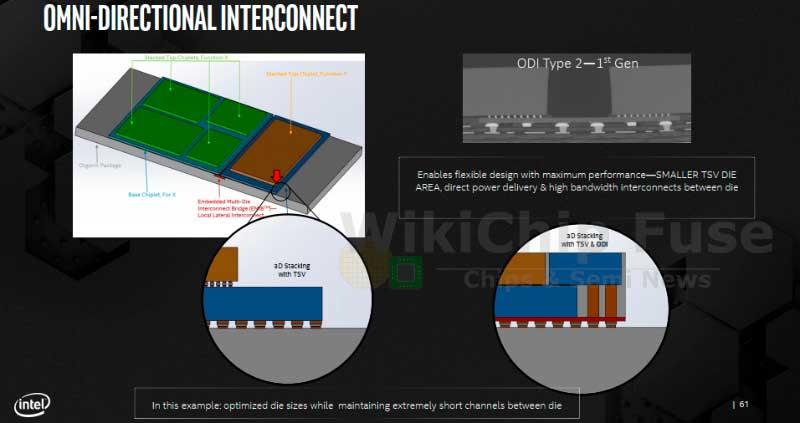

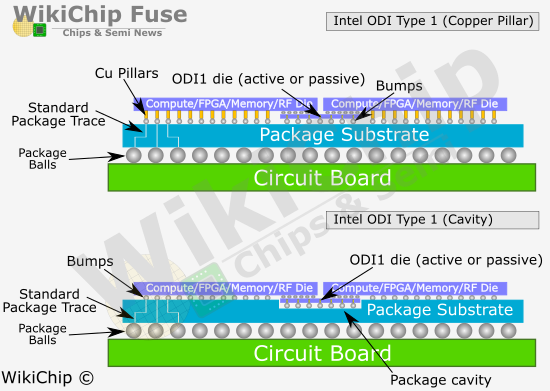

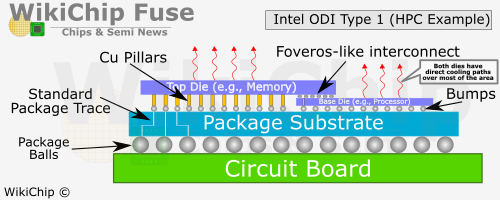

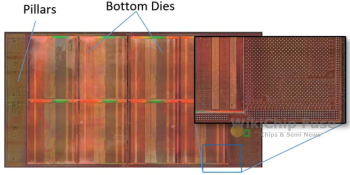

At the moment, Intel ODI is divided into two general types and these in turn into two complementary technologies, making a total of four variants. The Type 1 variant focuses on problems between the lower and upper dies, while the Type 2 does so between the lower dies that are, vertically speaking, completely below an upper die.

That is, a Foveros package and a CO-EMIB package, where Intel EMIB logically enters. Explained this we go with the different types more in depth.

Intel ODI Type 1

The first thing we must imagine is that the die we are going to talk about are of different sizes, which is important because the way of interconnecting them varies due to their dimensions. With this in mind we have to imagine a larger die that is below two smaller upper dies, or in the most extreme case, it is a larger die that is below another smaller die that logically does not cover all the lower area.

To give a more or less simple simile, it is a pyramid effect: the lower base is always of greater area than the upper one, with the difference that here there is only one die and on top it can have a smaller one or several, but they never reach be as big as the bottom one.

The advantage of this is that Intel has designed the system so that the bottom die only covers the portion of the top die where bonding between them is required. The reason for this has its logic: you eliminate the disadvantages of TSVs and keep all those of Foveros. Since only the part of the union between the dies is used, Intel can make an active or passive Type 1 ODI.

This means that in the case of being passive it is only limited to the union between both dies, but if it is active, it works as an interconnect data transmitter, which is very useful if you want to add from HBM stacks to external cache or an iGPU . Therefore and going back to the mental scheme, if several die of different sizes are used by means of ODI 1, all of them are allowed to have access to better heat dissipation, where the IHS will have to be in some cases specific, but an access is achieved. direct to it and therefore the temperature problems are solved.

This is important because if we looked at both dies from a zenith view, there would only be a part of them that would be connected, the essential one, while the rest of the die is independent and remains in the air in each case, with two different heights of course and this is precisely what sets it apart from EMIB as a technology.

Not to mention that the union between both dies has to be made with thermal compression, among other things.

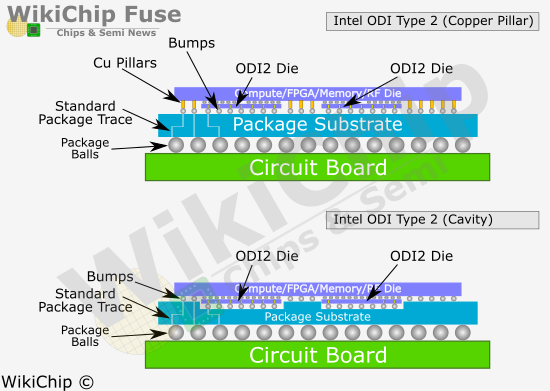

Intel ODI Type 2

Here the problem increases, since the lower die is always below the upper die, that is, there is no part of the die that is below that protrudes from the one that is above. This brings the disadvantage of heat, but at the same time it has a clearer advantage: the lower die can be placed exactly where required compared to the upper die and the number of connections can be much higher.

This technology is focused on alleviating performance and connection problems between dies, where the superior’s performance is always maximized, such as better input and output interconnections, more speed in the caches, outsourcing them without penalty and endless. of possibilities.

You could do a Zen 2-style I / O, leaving the caches out of the cores in different die, making intact cores and in three different levels without loss of performance because they are directly connected to each other through physical unions with TSV. The advantages of this are so evident that it is absurd to even comment on them.

Here the problem is the temperature, but with ODI Type 2 what is intended is to place the die with the lowest energy consumption in the lower part and to scale vertically until placing the dies that generate more heat in the upper stratum, being able to be refrigerated with the IHS, which gives some really amazing CPU configuration options and enables segregation for inclusive efficiency.

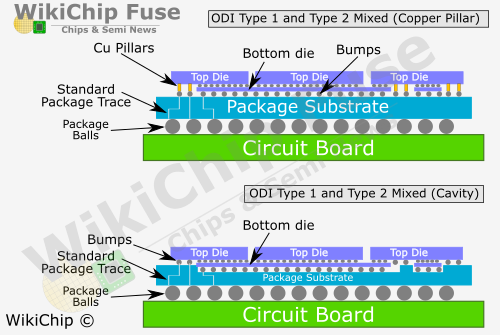

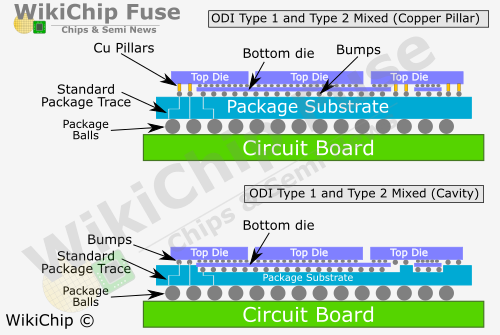

As we have said, ODI Type 1 and Type 2 have two different versions: Copper Pillar and Cavity , where in the first one copper pillars would be used to compensate for the greater height, while in the second the substrate would mold to the lower die allowing to use bumps instead of pillars.

Intel ODI can mix both types to offer more complex CPUs

Another advantage of ODI as a technology is that it is not exclusive, that is, both types can be used with their two versions on the same CPU. Therefore, the modularity that we are going to be able to see in the CPUs of the future is of such a caliber that the complexity in its design will be the main challenge for Intel.

The most obvious question is at the same time the most pertinent: when will we see these CPUs on the market? A really difficult question to answer. Keep in mind that ODI as a technology is only a few months old, it is currently being implemented and it has to improve in terms of simplifying the process, but Intel has dared to offer approximate dates: 2022 or 2023.

ODI as technology will manage to shorten the deadlines, since it solves the two main problems of the three Intel technologies, so the first processors (they do not have to be for the desktop obviously) could be seen in production in 2024, being really optimistic, since As is often the case, less powerful versions are released first and when both process and production are polished and improved then the high performance version is offered.

In any case, this is not science fiction, this is a reality, palpable, which has already been on the market with Kaby Lake G and Stratix 10 and which is undoubtedly the future of processors, which is a much greater revolution than The multi die or MCM due to its complexity, is the definitive step to be able to palliate the wall that we will find with the lithographic processes back in 2030 and it can be without a doubt the previous step to more complex technologies that leave what we currently have in diapers in the market.