We tend to look ahead, but rarely do we look back. Sometimes doing that is more than convenient to know where we are going and what we have learned, or simply to understand why things are like this. In the world of wafers, of their interconnections and packages, a generalist technology changed everything, to the point that nowadays evolutions of it are used to create from high-performance processors to mobile SoCs. We are talking about InFO, a technology that was developed by TSMC .

For the evolution of processors and chips to take place, a foundation is needed to determine the performance and capabilities of the new technologies that they will host. Even if an engineer has in mind how these should be approached for years to come, the way to do it is the really complicated step. We have seen how the industry turns towards chiplets, but, although they are a reality that is gradually taking over the market, one of the key technologies and concepts is little known. How did we get here?

InFO and its two variants PoP and oS are the key to evolution

Before we dive into the technology itself, we need to know what InFO is. As such, InFO is the acronym for Integrated Fan-Out , what is often referred to in the industry as wafer-level packaging, which translated would arrive as a technology platform for systems integration.

That is, a method of adding subsystems or components to the chips already within the wafer itself. A clear example is HBM inside any chip in vertical format (not horizontal like GPUs that need a substrate or interposer, do not confuse them) although any type of DRAM would also work, for example.

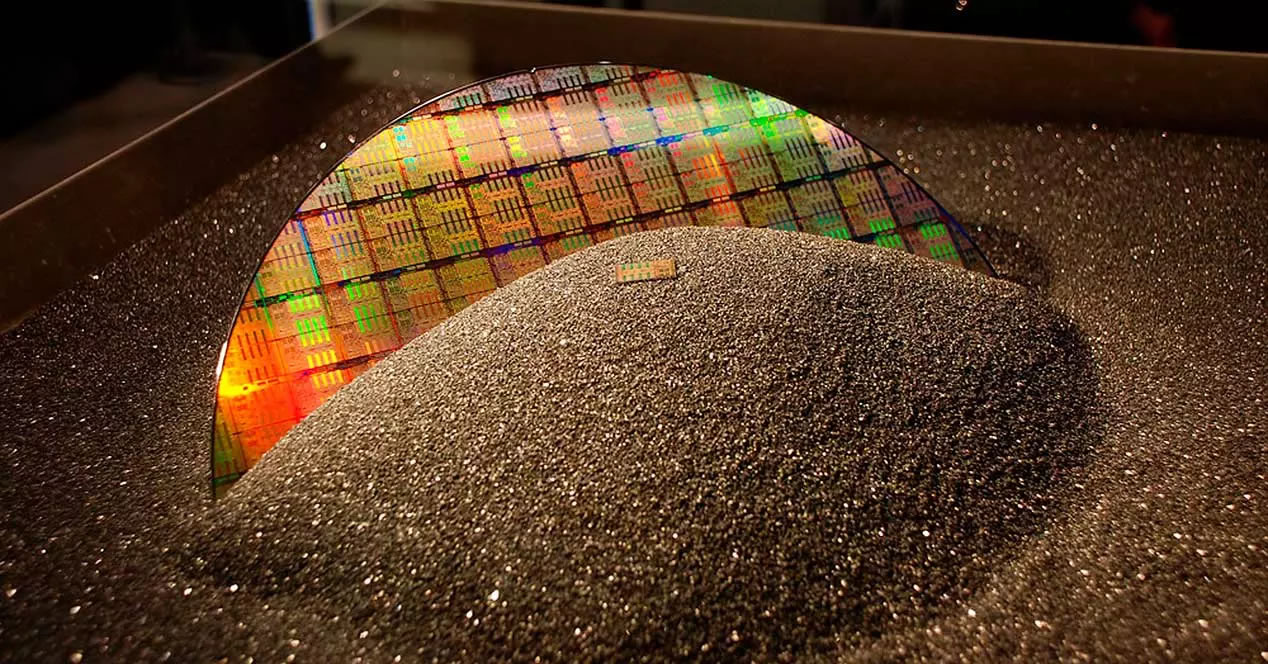

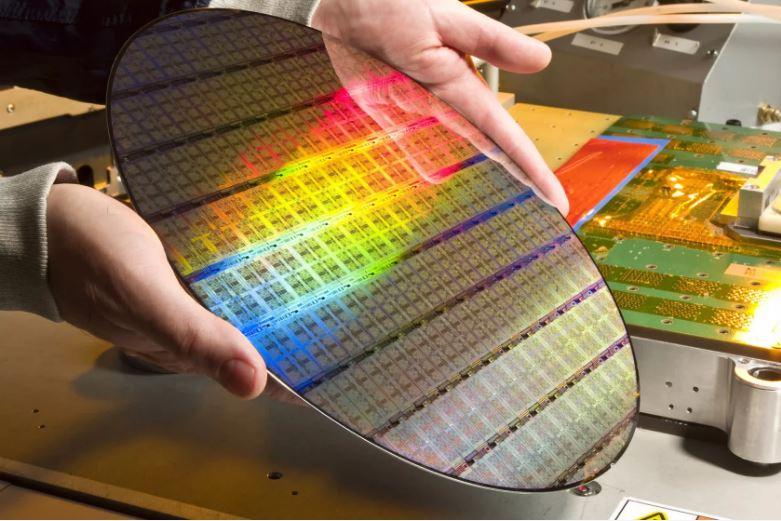

In order to integrate a subsystem or component at the wafer level, it will be necessary to use high-density RDL (Re-Distribution Layer) and also TIV (Through InFO Via) technology to make the interconnections between both layers without losing performance. The process involves cutting the chips from a silicon wafer and then placing them very precisely on a thin “reconstituted” or carrier wafer, which is then molded. The redistribution layer is created and then solder balls are formed on top, as in a wafer-level chip scale package. After that, the new wafer formed by chips is baked so that the compound is cured and it would be ready for production.

Variants involve being able to design 2D or 3D chips

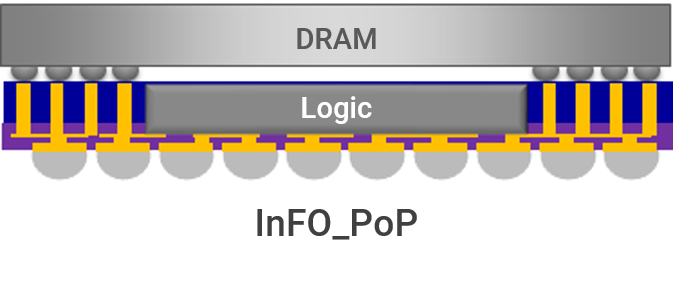

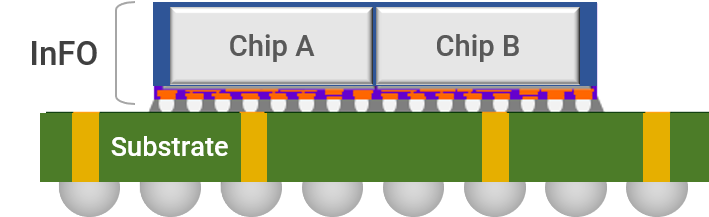

As we have discussed, InFO has two variants that, depending on the design of the chip and its complexity, can be used for its creation on the wafer. We are talking about PoP and oS, where each one has its peculiarities and for the moment and despite the fact that they have been used since 16 nm, neither ends up imposing the other as a clear dominator.

InFO_PoP is the first Fan-Out package for the industry within the 3D wafer concept. It is the most used when integrating components such as dies, DRAM or interposed substrates for more layers. It has the particularity of using finer welds, which gives it a thinner final profile and better electrical and thermal performance due to the fact that it lacks an organic substrate.

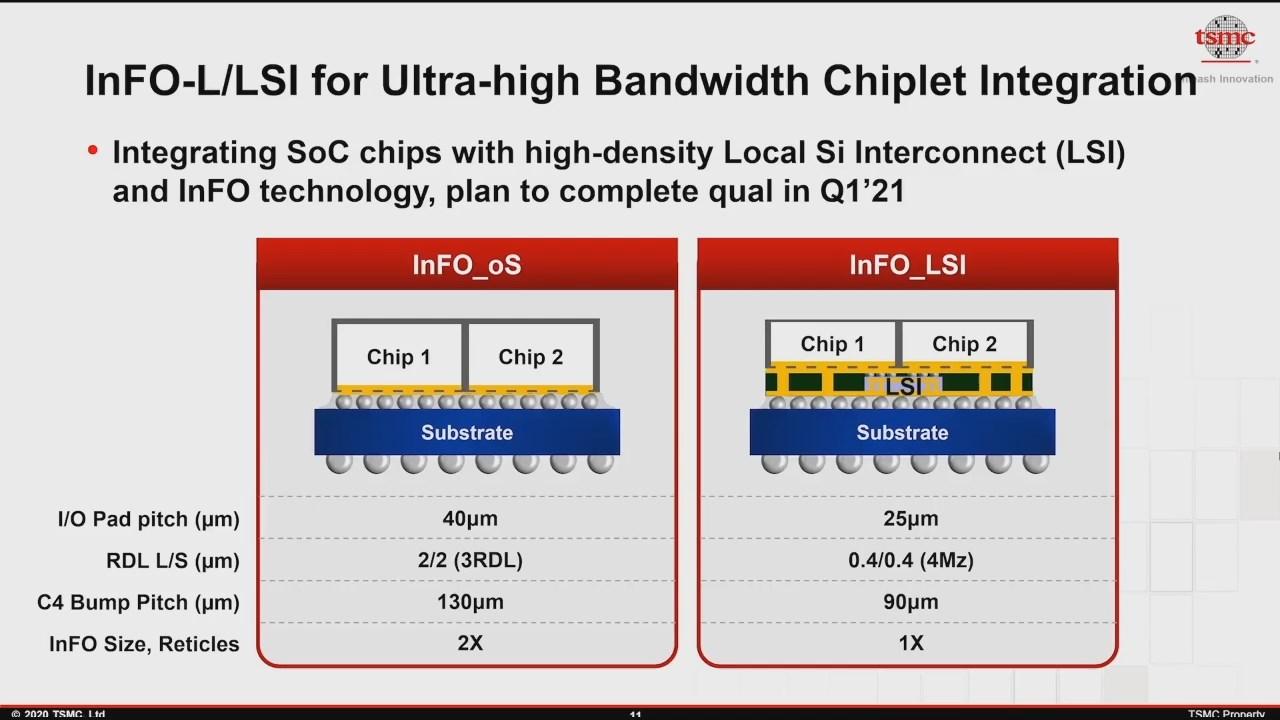

On the other hand, InFO_oS does need a substrate to be able to take shape, where the normal height will be approximately 2 micrometers. The advantage is that by including substrate more chips can be interconnected with it and it does not depend on something as individualized as the PoP method. Giving I / O or input measurements is complicated, since each company has its own and each node requires a resizing of the same, but in any case we always talk about micrometers.

It is this technology that has allowed Intel and TSMC to put off Moore’s Law for yet another few years, albeit by scaling multi-wafer systems.

InFO-L / LSI, the ultimate in system scalability

A new technique within InFO should be nearing completion to be mass produced as early as 2022. We speak of InFO-L or InFO_LSI , as you prefer, where an interconnecting layer of silicon is integrated between the substrate and the chips that improves aspects such as the integrity of the signals and even the voltages or temperature, since they require lower values.

The problem is that the chips must be designed with a lower thickness so as not to raise the overall height of the die too much, thermally limiting the dissipation between layers. This is interesting when it comes to the GPU or CPU cores plus HBM in any of its variants.

Adding height limits the maximum tolerable values, as we saw for example in the i9-9900K or in the Radeon VII, so it is not something to really despise. New chips coming out of the factory have to do this, so it will be interesting to see how much they rise relative to the original substrate.