The announcement of the 2 nm process by IBM is a demonstration that the hardware will continue to scale for the next 5 years as it has always done and continuously, but in turn said announcement generates a series of unknowns since the number of nanometers for a long time corresponds more to marketing than to physical reality.

This week we saw the new IBM manufacturing node announced. What can we expect from this node and what will be the leap compared to the nodes currently used for the manufacture of different chips and memories?

Comparison of IBM’s 2nm node with current ones

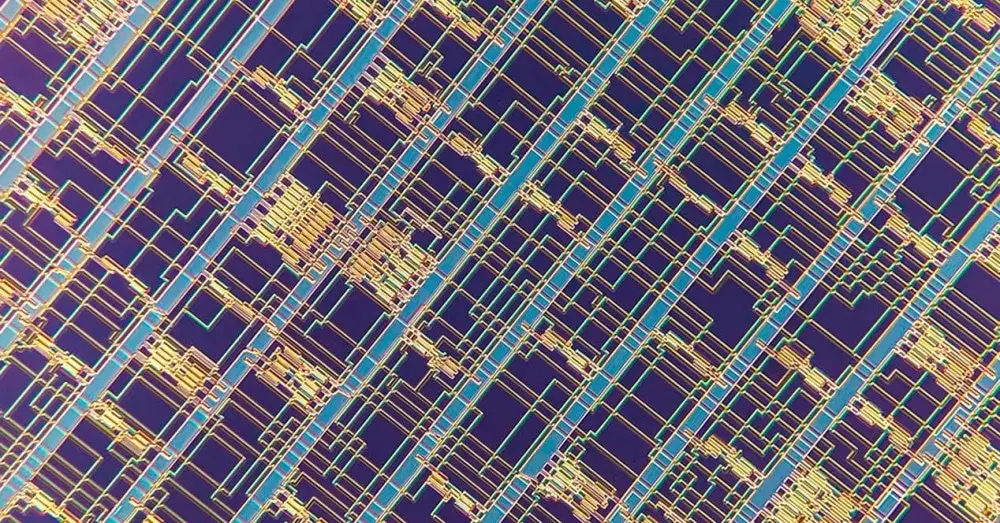

The sample chip that has been manufactured with IBM’s 2nm node has a density of 333 million transistors per square millimeter. Keep in mind that the density of the transistors depends on what is built with them and that memory is much denser than logic, so not all areas of the processor manufactured by IBM in its experimental 2 nm node they have such a density. In any case, measuring the density from what the SRAM occupies in each node is normal in these cases.

The news is important in the face of a situation in which Moore’s Law seems to be slowing down more and more and with the general feeling that a node will be reached that in terms of development costs, deployment or physical limitations does not allow the chips to be scaled further. .

In reality we are facing a node so we should wait for 2024 or 2025 at least in terms of its launch on the market.

Are they really 2nm?

TSMC’s 7nm node density is 96.5 million transistors per square millimeter. It must be taken into account that the density of the transistors increases quadratically with the decrease in their size. For example, to double the density of any node we just need to multiply the size by 0.7. For example, if we take the 7 nm one we only need to multiply that size by 0.7, which gives us a 4.9-5 nm node.

But are we really looking at a 2 nm node? To know the density that a hypothetical future node would have, we just have to do the following calculation:

Scaling factor of the node to convert to = (1 / known node) ^ 2

Then we just have to do the following:

Transistor density of the new node = Transistor density of the known node / Scaling factor of the node to which it is intended to convert.

With the first formula we obtain a scaling factor of 0.08, which indicates that a hypothetical “real” 2 nm node would have a density of almost 1200 million transistors per square millimeter. Almost four times more than that announced by IBM, but it is also necessary to add to this that the 7 nm of TSMC is not really exactly 7 nm, but a much lower density and therefore a much higher node in real nanometers.

How does it compare to the rest of the existing nodes?

The reason it is called a 2nm node is because its density is higher than the 3nm nodes advertised by Samsung and TSMC. In Samsung’s case, the advertised density for its 3nm node is 180 million per square millimeter, while TSMC’s 3nm process has an advertised density of 315 million.

The reason IBM calls its node “2nm” is simply because its specifications are far superior to those of TSMC and Samsung. Now we will see the arguments for it.

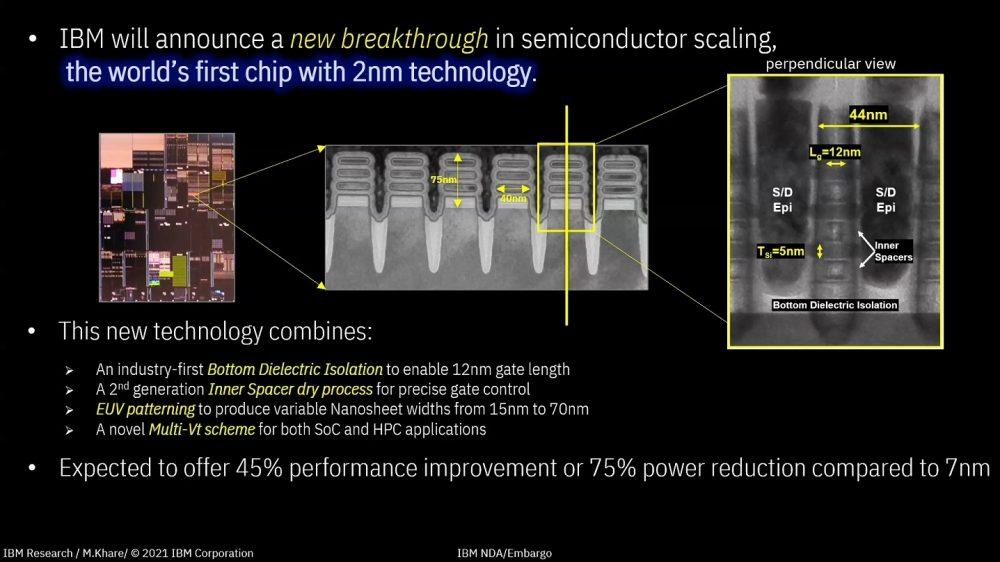

IBM 2nm node speed and power consumption

Another important point is how processors scale in speed and consumption, that is, if we manufacture an existing chip under the new node. How fast would it reach or how would consumption be reduced? Both at the same time cannot be, so the two figures are given separately.

A processor that was manufactured under the 7nm node of TSMC, under the 2nm node of IBM would go 45% faster in clock speed under the same consumption. Whereas if we kept the clock speed then the energy consumption would drop to 75%.

The clock speed, however, has a trick, since the exact point of the voltage and clock speed curve that is the highest is always sought. The same is the case with the consumer one, where it seems that IBM has obtained a better node from the perspective of the energy consumed.

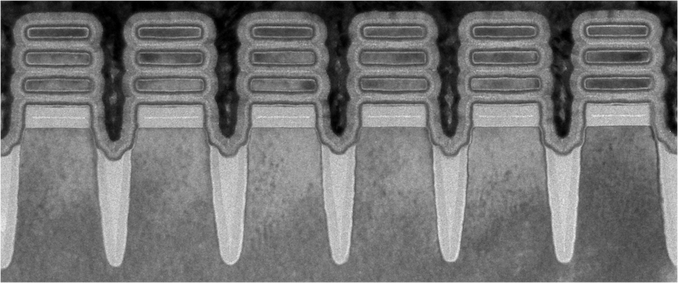

It is in the highest energy efficiency that the IBM 2 nm node receives its name, and this is due to the use of what is called HNS or Horizontal Nanosheets, a technology that Intel will use in its 5 nm node, which will compete from your to your face to the 3nm nodes of Samsung and TSMC. We know that Samsung will adopt them in the future but we do not know if TSMC will do so or if they will opt for another solution.

The joint venture between IBM and Intel

Yes, this statement may seem very shocking to you, but we must bear in mind that IBM, unlike Intel, does not have its own foundries, but it does design chips and, above all, invest a lot in the design of new chip manufacturing nodes that it licenses to third parties. So it is a different business model than TSMC, Samsung and Intel have.

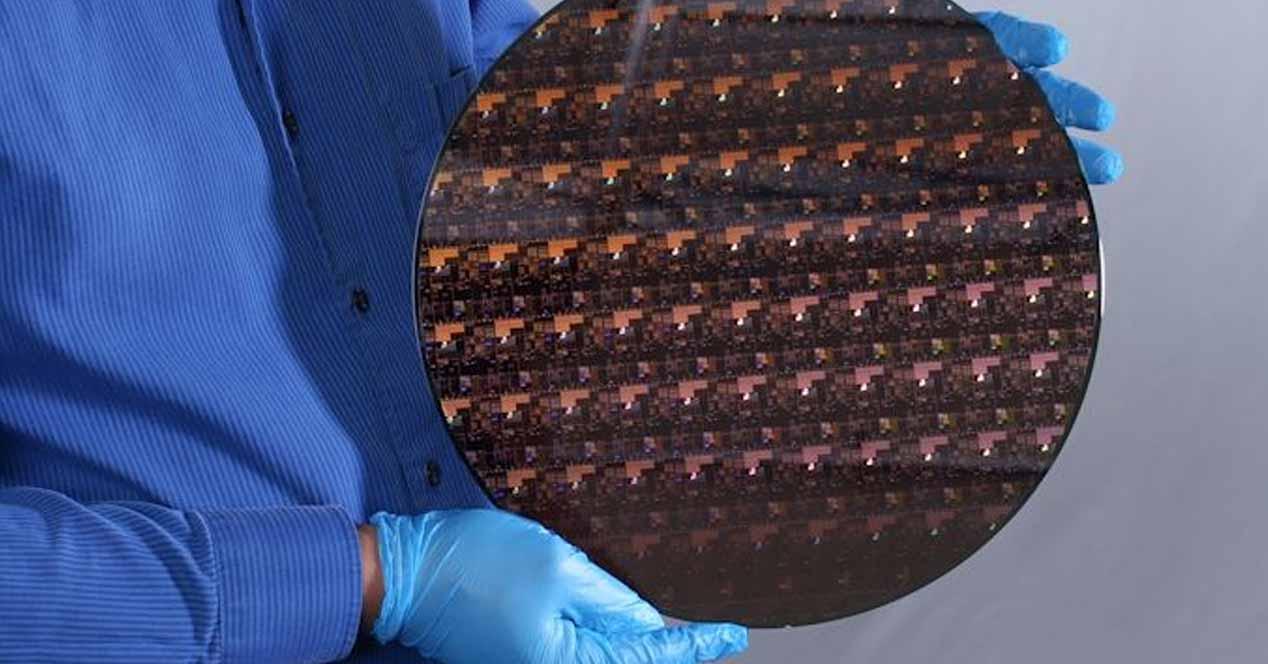

That is to say, what IBM has done is to design the standards for a new manufacturing node and then it has created a sample chip, which is a design that brings together all the common elements in the design of a contemporary processor and has recreated using an experimental version of its 2nm node.

IBM has routinely worked with GLOBAL FOUNDRIES, but they dropped out of the race entirely and didn’t get into 7nm. So the IBM partner in this case is Intel and we may be looking at the specifications of a future lntel node.

Moreover, it is possible that we are facing the specifications of the 5 nm node from Intel, with which they would stand up to the 3 nm nodes from TSMC and Samsung that we have discussed earlier in this article.