At the 26th TSMC Technology Symposium, the manufacturer gave the first details on its progress with the 7nm node N7, as well as the 3nm N5, N4 and N3 nodes. TSMC also shared details about its new 3DFabric technology and provided some clues as to which technologies it will use to continue scaling beyond the 3nm node. In this article we will tell you how this ace up its sleeve works by means of which TSMC is already looking at Intel in the rearview mirror.

TSMC has already disrupted the hierarchy of the semiconductor industry when it bypassed Intel and Samsung and moved to its industry leading 7nm node, propelling Intel’s competitors (AMD among others) to the Vanguard. Still, the company shows no signs of slowing down its rapid pace of innovation and has plans to start mass production of its 3nm technology by 2022 (to put this in perspective, Intel plans to introduce its 7nm technology by the end of 2022 or early 2023).

TSMC manufacturing processes

TSMC’s 5nm N5 process employs EUV technology “extensively”, and offers the expected benefits of scaling lithography relative to 7nm N7. TSMC claims that the N5 process offers up to 15% more performance (with the same consumption), or a 30% reduction in consumption for the same performance, with a logical density gain of 1.8X times over the N7 process . They also claim that the defect density learning curve for N5 is much faster than N7, which means that this process will reach higher throughput rates and faster than its predecessor.

| N5 over N7 (7nm) | N5P over N5 | N4 (5nm) over N5 | N3 (3nm) over N5 (5nm) | |

|---|---|---|---|---|

| Power for equal performance | 30% | 10% | ? | 25-30% |

| Performance with the same consumption | fifteen% | 5% | ? | 10-15% |

| Density improvement | 1.8X | ? | ? | 1.7X |

| Risk / Mass Manufacturing | In production | By 2021 | 2022 | Second half of 2022 |

TSMC also has its enhanced node N5P, which is under development for high-performance applications, with plans for mass production in 2021. N5P offers 5% more performance or a 10% reduction in consumption over N5. According to the company, they already have their next server chip in the N5 process, so it is clear that TSMC has already cleared most design hurdles for 5nm.

Due to support for node N5, the 5nm N4 process offers easy migration with performance, power and density improvements that have not yet been estimated. TSMC hasn’t given much detail, but the manufacturing process is known to require fewer layers, and they plan to start hazard production in Q4 2021, reaching mass production by 2022.

The company also said that its N3 node at 3nm would start risk production in 2021 and reach mass manufacturing in the second half of 2022. This node offers full node scaling over N5 and will bring a performance improvement from the 10-15%, or a consumption reduction of 25-30% along with a density improvement of up to 1.7X. The node continues to use the FinFET architecture and offers a 1.2X increase in SRAM density and 1.1X increase in analog density.

Nodes below 3nm will look for alternatives to silicon

TSMC is also working on defining their next node beyond N3, sharing some of the industry advancements that could help them reach beyond 3nm, though it did not name the technologies they would use. They listed nanosheets and nanowires among the advancements along with the use of new materials such as high mobility channels, 2D transistors and carbon nanotubes as candidates in which they are already investigating.

TSMC has over 15 years of experiences with nanosheets technologies and has shown that it can produce 32Mb nanosheets SRAM devices that operate at 0.46V. They have also identified several non-silicon materials suitable for 2D that could scale the channel thickness even below 1 nm. Of course, carbon nanotubes are also part of their plans.

For this, the company continues to deepen its investigations and the investment of 2.96 billion in 2019 alone proves it. They are building a new R&D center with 8,000 engineers next to the company headquarters, and the first phase of this project is expected to be completed in 2021.

3DFabric, TSMC’s ace up the sleeve

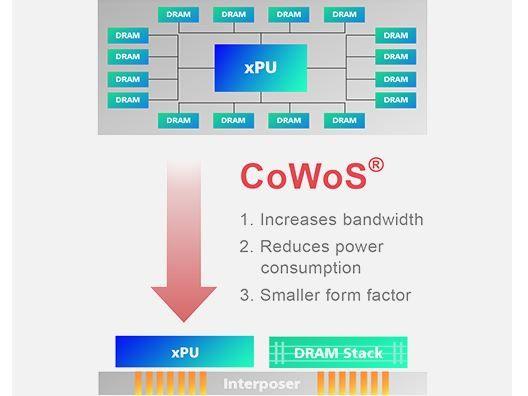

Reflecting what we’ve already heard from other industry players, TSMC believes that advanced packaging technologies are the key to higher density scale, and that 3D packaging technologies are the way to go. That’s where 3DFabric technology comes in.

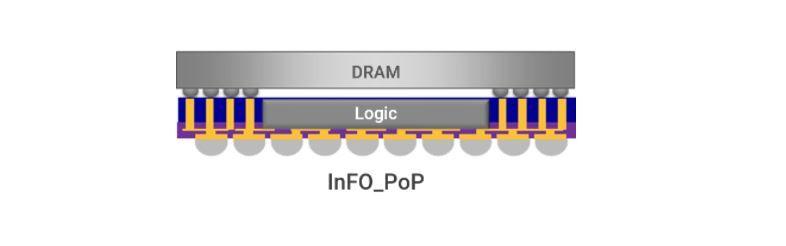

TSMC already has a strong portfolio of 3D packaging technologies in its wafer-level 3DIC technologies, CoWoS (Chip-on-Wafer-on-Substrate), InFO-R (Integrated Fan Out), COW (Chip on Wafer) and WoW (wafer on wafer). The company is now trying to implement these technologies under the name 3DFabric, which appears to be a new branding scheme for its 3D packaging technologies that bind chiplets, high-bandwidth memory, and specialized IP into heterogeneous packages.

So, in short, 3DFabric is a kind of “family” that includes all the different technologies in which TSMC is working both for the node at 3 nm and for those that will come after, and they foresee that they will be able to go down even from 1 nm using this technology.