Moore’s Law has been the guiding principle of the semiconductor industry for more than fifty years. For thirty of these past thirty years, Robert Chau (current Director of Research and Components at Intel) has been a part of Intel’s technology development organization, giving you an overview of groundbreaking innovations that have enabled constant improvements in density, performance and efficiency in transistors. And according to Chau, Moore’s Law still has a very bright future ahead and we are far from reaching the tipping point where it can no longer be met .

At its simplest level, Moore’s Law refers to the doubling of transistors within a chip with each generation of the manufacturing process. Over the years this exponential increase in transistor density has remained remarkably constant, but two things have changed along the way: how we achieve these density increases, and the benefits to be gained at the product level.

The future of Moore’s Law according to Robert Chau

Whether it’s higher frequencies and lower power consumption or more functionality built into a chip, Moore’s Law has been future-proofed and has evolved to meet the demands of every generation of technology, from mainframes to mobile phones. This evolution will continue as we move into a new era of unlimited data and artificial intelligence.

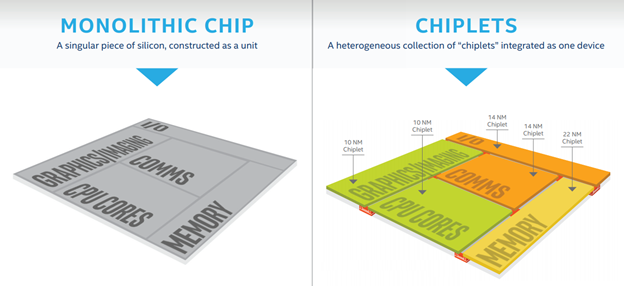

What innovations will Moore’s Law drive over the next decade? I think they can be collectively categorized into two fairly broad areas: monolithic scaling and system scaling. The monolithic scale can be referred to as the “classic” scale of Moore’s Law, with a focus on reducing transistor sizes and operating voltages while increasing the performance of each transistor. System scale enhancements are the gains that help us to incorporate new types of heterogeneous processors through advancements in chiplets, packaging, and high-bandwidth chip-to-chip interconnect technologies.

Intel is investing heavily in research to support both vectors; At the 2019 annual meeting of the world’s leading semiconductor process technology drivers, IEDM in San Francisco, Intel engineers presented nearly twenty papers demonstrating groundbreaking work ensuring a bright future for Moore’s Law for generations to come. . What follows is a high-level summary of these exciting technology options.

Monolithic scale: a new dimension

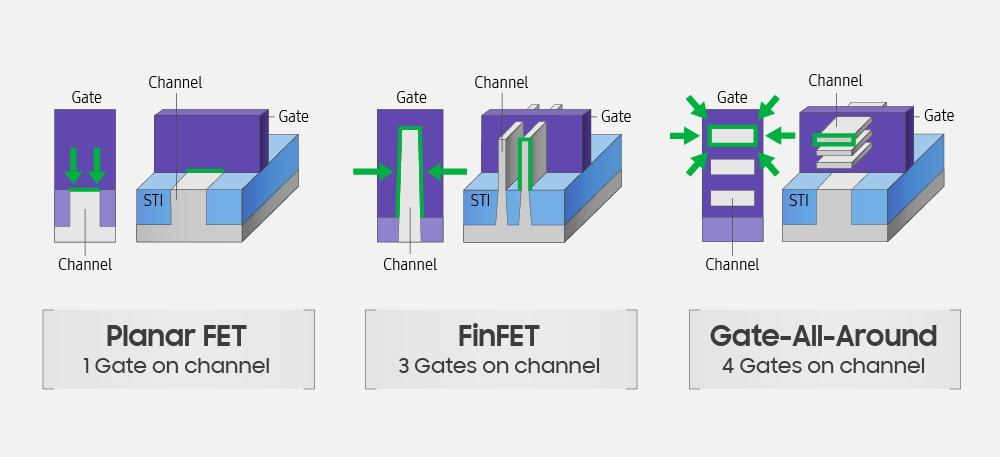

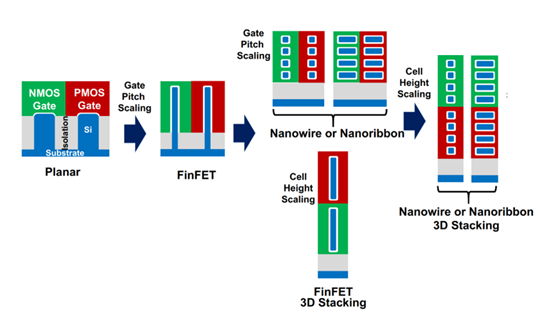

Current generation Intel processors are based on a transistor structure known as a FinFET, in which the gate surrounds the fin-shaped channel on three sides. As Intel’s compute nodes have advanced, they have made the fins taller but narrower, reducing the number of fins required to achieve a certain level of performance.

While FinFET still has a lot of life ahead of it, sometime in the near future the industry will transition to a new type of transistor architecture: Gate-All-Around (GAA) FET , in which the gate wraps the channel in all its sides. There are multiple potential implementations for GAAFET, from thin nanowires to wide nanoribbons. What they share in common is the ability to pack more high-performance transistors into a given area, thus reducing the width of the standard cells our designers use to build new processors.

In addition to this new transistor architecture, another way to drive cell area scaling is through vertical stacking of transistor devices. Modern semiconductors are built from complementary pairs of positively and negatively charged transistors called NMOS and PMOS. The height of a standard cell can be significantly reduced by monolithic stacking of an NMOS device on top of a PMOS device, or vice versa. This can be achieved by stacking FinFET, GAAFET, or even a combination of both.

Monolithic stacking of transistor devices not only offers improved density, but is an interesting way to integrate multiple materials onto a single silicon substrate, providing significantly improved performance and opening the door to completely new product classes with a unique functionality.

System scaling: beyond the transistor

Continuing to drive the future of Moore’s Law requires integrating improvements into all aspects of the manufacturing process, not just at the transistor level. For decades, many in the industry viewed packaging as simply the final manufacturing step, the place where we make the electrical connections between the processor and the motherboard. However, this has changed dramatically in recent years and is now a crucial point in the entire manufacturing process.

Ten years ago, the emphasis in SoC integration was on implementing CPU and I / O functionality on the same die as a high-performance CPU. In the future, advanced packaging technologies will be used to link different types of processors, but without forcing them to share a single manufacturing material or process node.

This kind of decay may seem, at least initially, to be the antithesis of what Moore’s Law is intended to achieve, but the performance and density improvements gained by matching each processor type to its own design implementation and logic of Lower-tuned transistors often outweigh the negatives caused by breaking up a monolithic die into smaller chiplets. In fact, in his original 1965 article, Moore stated that “it may be more economical to build large systems from smaller functions that are packaged and interconnected separately.”

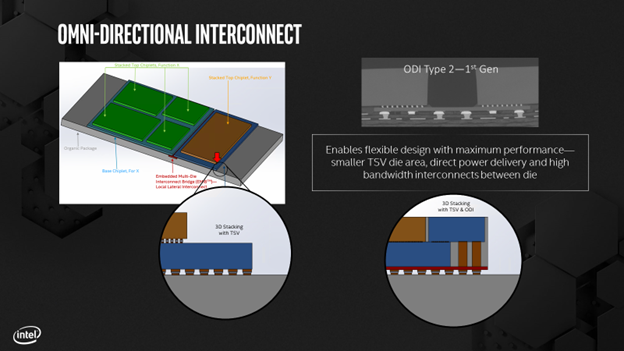

Intel has already implemented technologies such as EMIB (Embedded Multi-die Interconnect Bridge) and Foveros to connect chiplets in two and three dimensions, such as placing HBM memory between CPUI and CPU (as in Kaby Lake-G, with EMIB), or to connect the 10nm compute matrix used in Intel’s Lakefield processors face to face with the 22nm I / O matrix directly below. They also have plans to combine Foveros and EMIB together in a technology called Co-EMIB, in which multiple Foveros 3D chips are connected via EMIB, allowing Intel to build chips much larger than the size of the grid for any processor. monolithic and scale chip designs in a much broader way than before.

Intel is already looking, in fact, beyond the Co-EMIB towards a new standard called “Omnidirectional Interconnection” (ODI). One of the problems with stacking chips on top of each other using existing methods like silicon vias is that the amount of energy that can be pushed through such small wires is very limited. ODI uses much thicker pathways for power delivery, while offering the same capabilities as Foveros when implemented for face-to-face 3D bonding.

ODI can be used to connect chiplets in a wide variety of configurations, including scenarios where one die is partially “buried” and acts as a bridge between two others, or even between two slightly overlapping dies, with ODI used between them for a few. thicker power pillars, allowing the chips to pack much closer together.

The ability to integrate 3D stacks of processors presents another method of enhancing the density of silicon that is totally decoupled from the transistor-focused “classic” concept of Moore’s Law. Traditional monolithic scaling will continue at 7nm with the introduction of EUV, then 5nm and well beyond, but it is not the only area where Intel hopes to deal with further improvements from generation to generation in both density and performance.

The improvements that will drive the future scaling of Moore’s Law at Intel are not driven solely by reductions in process nodes or improvements in lithography, but by collaboration between multiple engineering teams involved in different parts of the design process. Here, Intel’s unique status as an embedded device manufacturer (IDM) is an advantage, as Intel makes its own products and there is close collaboration between the design teams and the engineers who make the parts. Thus, we have the option of modifying an architecture to better suit the capabilities of a process node, or of adjusting a node to match the capabilities we want to offer in a given architecture.

It cannot be denied that we face significant challenges in the industry, but the future of Moore’s Law will be anything but a slow decline into obsolescence. Expanding the scope of how we deliver generational-scale improvements has broadened the possible options for implementing them, and Intel has never been more optimistic about the long-term health of Moore’s Law than now.