While chip making node technologies and Moore’s Law are in full and apparent slowdown, chip makers and designers continue to seek creative new solutions to enable device scaling and performance to continue to increase. Advanced encapsulation technologies are one of those areas where we have seen great innovations in recent years, such as the introduction of silicon interposers , the integration of HBM memory on the chip itself, or the shift towards modularization with chiplets. Today we are going to talk to you about TSMC’s LSI technology , with which they intend to build their chips in the future and which can change -for the better- how this industry works.

Silicon interposers pose cost challenges as they are very expensive and require a fairly large amount of silicon, while chiplet designs using conventional packaging on organic substrates are limited by input / output bandwidth and energy efficiency. One solution to this problem has been the introduction to the industry of intermediate silicon matrices that connect two logic chips together, but only in a limited scope and without using the same footprint as a full silicon interposer. Intel‘s EMIB (Embedded Die Interconnect Bridge) has been the most talked about implementation of this technology lately.

TMSC LSI, will it be the future of the industry chips?

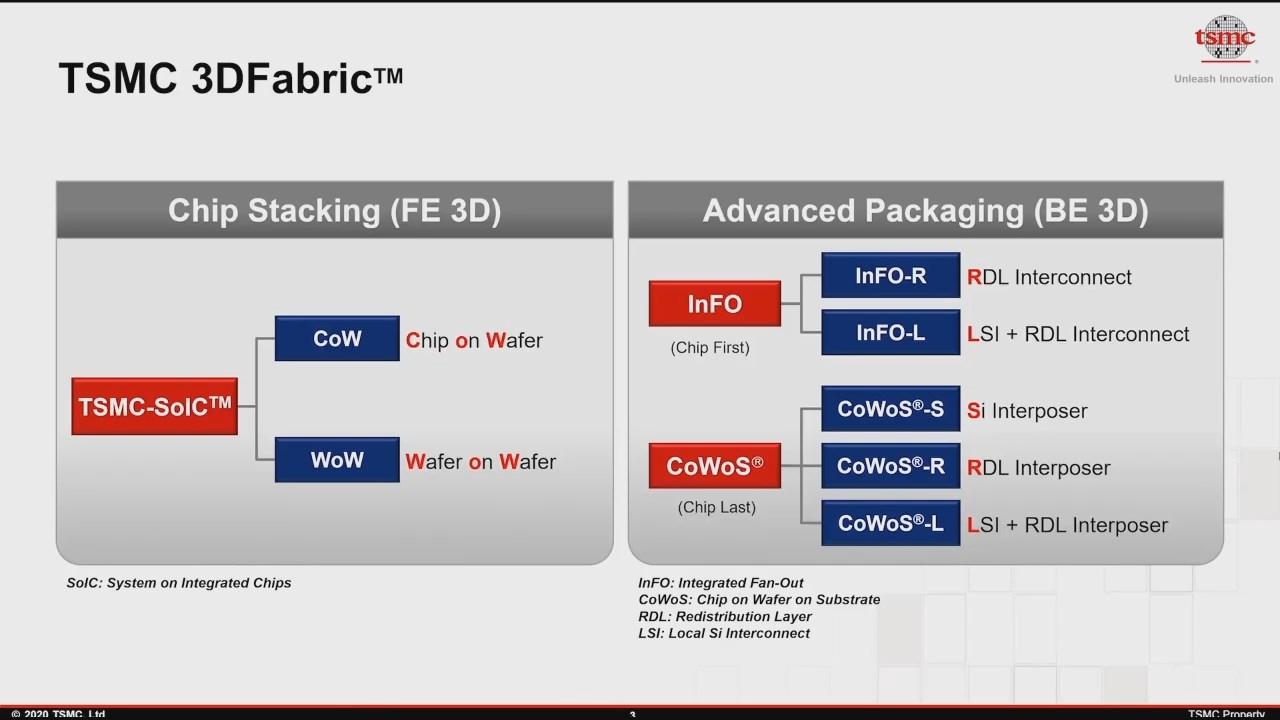

During TSMC’s 2020 Technology Symposium, the Taiwanese manufacturer detailed its own variant of such technology, called Local Si Interconnect (LSI), which will be offered for InFO and CoWoS encapsulation technologies in the form of InFO-L and CoWoS-L.

The new advancements are part of what TSMC now calls its 3D Fabric packaging technology, which offers a fairly versatile repertoire of encapsulation and integration options including, of course, SoIC, InFO, and CoWoS.

A brief explanation for our readers who are not familiar with these terms: SoIC (System on Chip Integrated) is TSMC’s hybrid bonding and chip stacking integration technology, which allows multiple chip arrays to be stacked together, making the width of band is extremely high and has a junction between dies of low consumption silicon. Currently, this technology is unmatched in the industry.

InFO is TSMC’s fan packaging or encapsulation technology, in which a die is removed from a silicon wafer and placed on another carrier wafer, upon which larger structures such as copper RDL are built. (redistribution layer) and subsequently the carrier substrate.

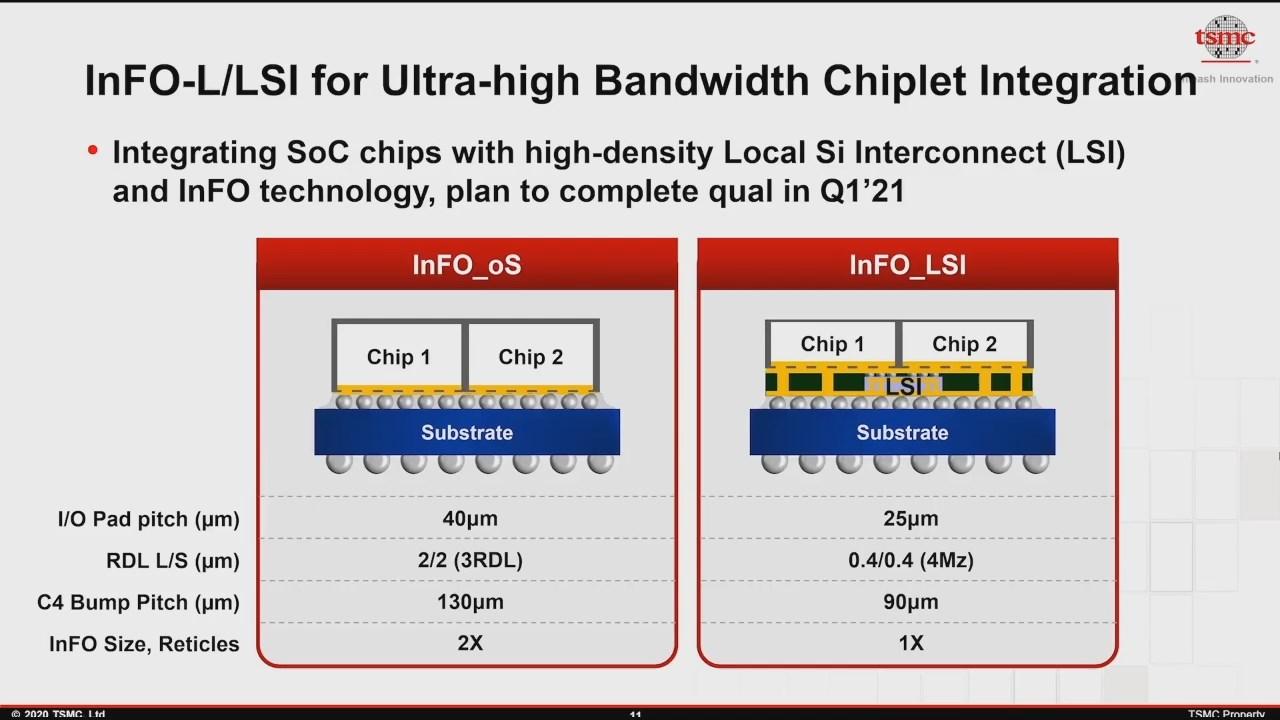

The TSMC variant of InFO with LSI integration is called InFO-L or InFO-LSI, and follows a similar structure with the new addition of this local silicon interconnect middleman chip for communication between both chips.

TSMC’s CoWoS (Chip-on-Wafer-on-Substrate) was originally described as the company’s 2.5D silicon interposer packaging technology, which is currently still under the CoWoS-S specification, but in the meantime also covers other encapsulation technologies. As its description says, the RDL is built first on the base substrate and only as a last step is the silicon chip added to the set.

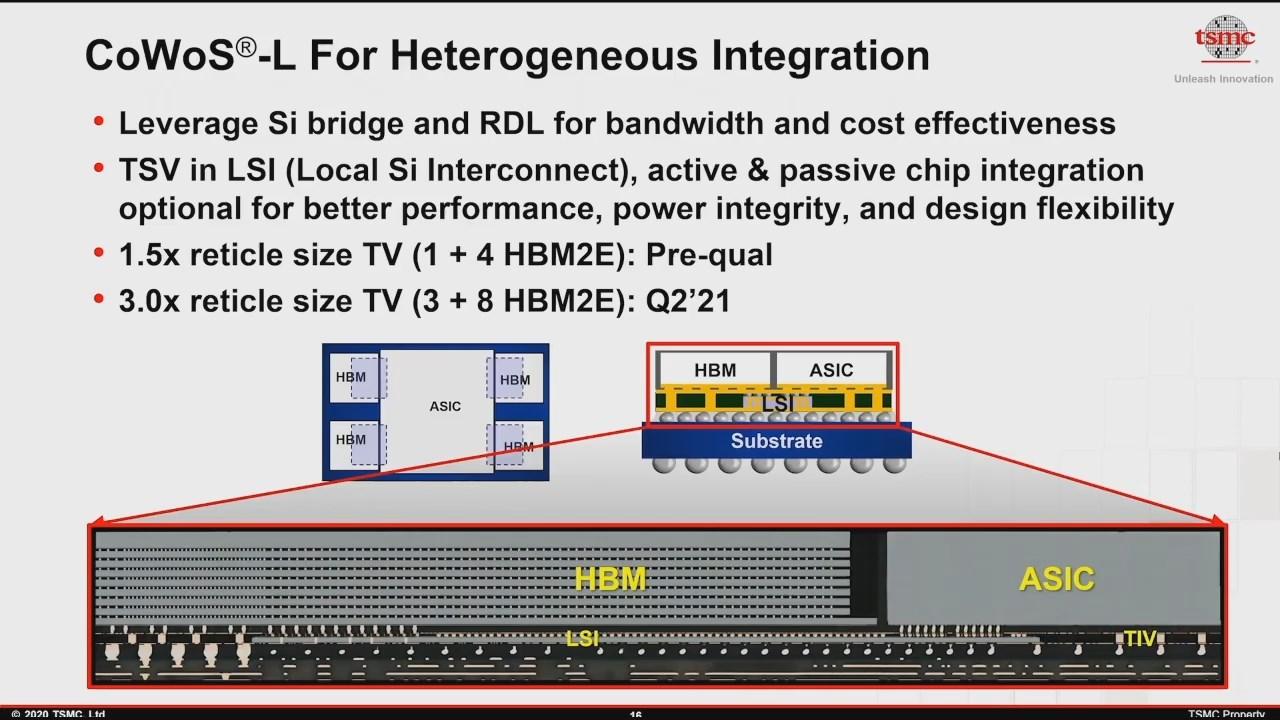

CoWoS-L is the new variant of TSMC’s chip packaging technology, adding local silicon interconnect that is used in combination with a copper RDL to achieve higher bandwidth than using an RDL packaging implementation. (CoWoS-R), and also has a lower cost than if a full silicon interposer (CoWoS-S) were used. In other words, with this encapsulation technology you get better performance at lower cost .

TSMC describes LSI as an active or passive chip (depending on the needs of the chip designers and their budget). The TSMC smelter expects to complete the InFO-L qualification in the first quarter of 2021, while CoWoS-L is in a prequalification process at the moment. Silicon bridge interconnect technologies like LSI and EMIB are expected to deliver high-performance chip designs at lower cost to both the designer and the consumer.

In short: chips with higher performance and cheaper, something that should translate (for the user) into more powerful and cheaper processors .