It is very possible that you have an electronic device that uses FinFET technology and you do not know it. This technology is present in SSDs and processors, among other components. So, we ask you to join us to discover it.

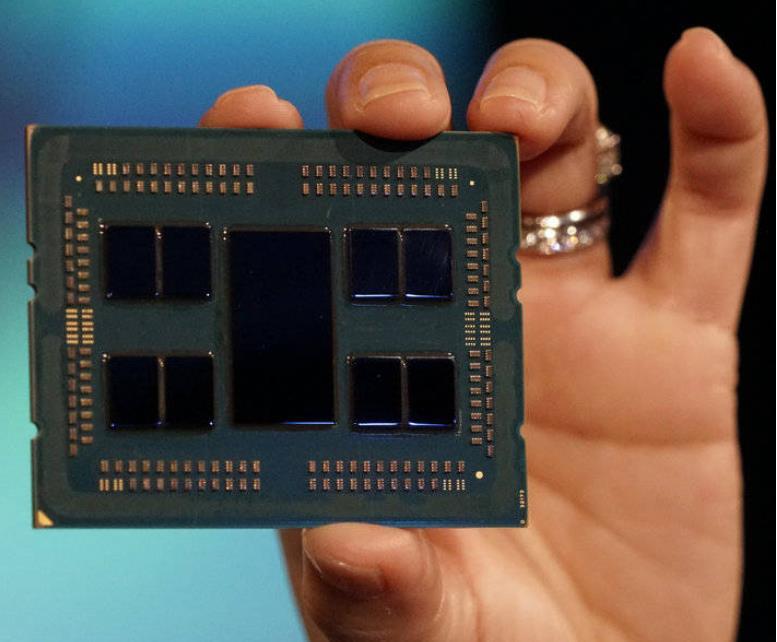

Intel was one of the first manufacturers to use FinFET transistor technology in the manufacturing of processors. FinFET transistors are present in most electronic devices, but not everyone knows for sure what this technology is or where it is used.

What is FinFET manufacturing technology?

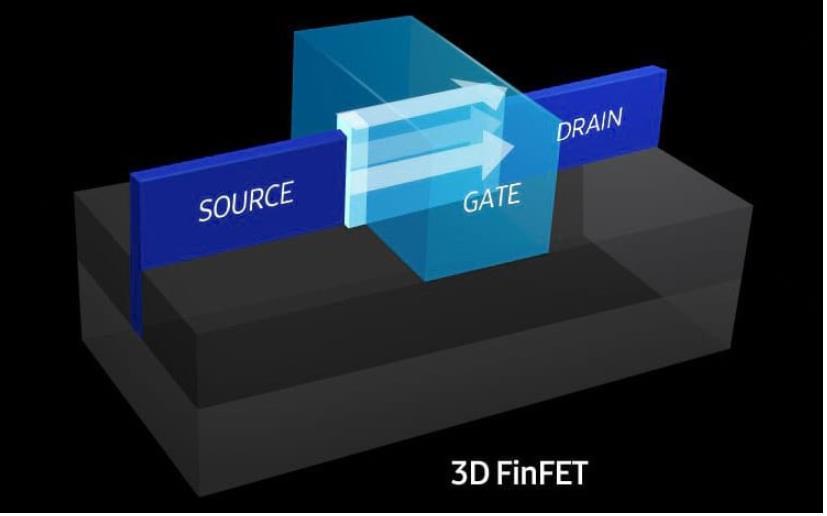

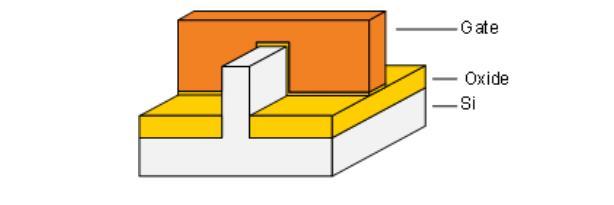

The word FinFET comes to be an abbreviation of ” Fin Field Effect Transistor “, which translated into Spanish means “Fin field effect transistor (fin)”. It is a transistor that is built on a silicone insulator (SOI) substrate. The FinFET transistor consists of a source, a drain contact, and a gate to control the flow of current. It differs from MOSFETs in that the inclusion of a 3D rod on top of the silicon substrate: the fin.

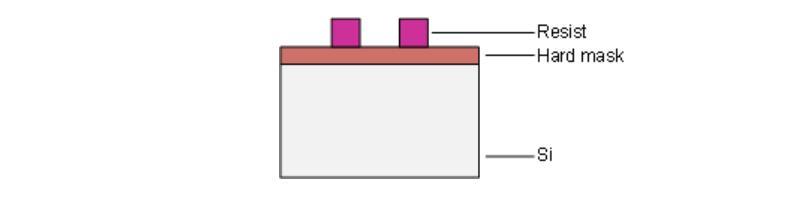

Intel was the first to use FinFET technology in 2012 with its Ivy Bridge processors. FinFETs are 3D structures that are stacked on top of the substrate. The construction of a FinFET transistor consists of the following steps:

- Substrate . It is the base of every FinFET transistor and has a hard layer on top of it.

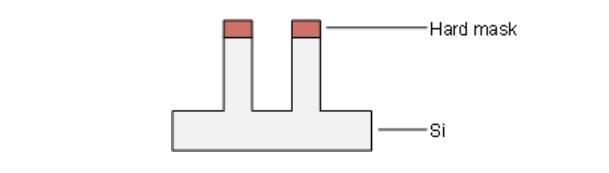

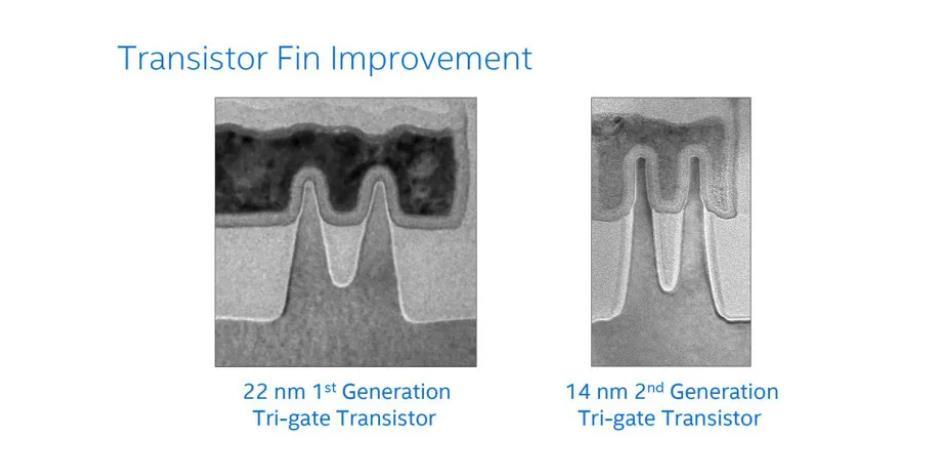

- Fins An important issue is the dimensions of the fins. For example, in a 22nm process, the width of the fins could be 10-15nm.

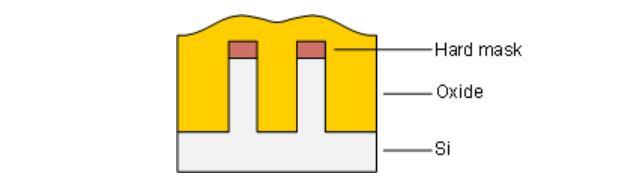

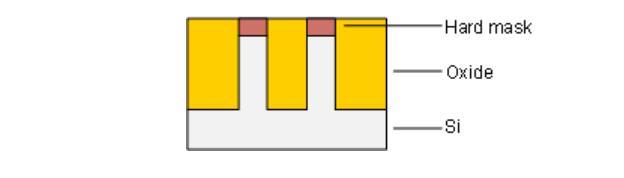

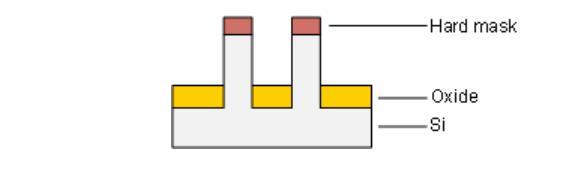

- Rust deposition . With the deposition, the aim is to isolate the aletras from each other.

- Planarization . There comes a time when the rust flattens out and the hard mask acts as a layer itself.

- Hollow engraving . Another etching process is required to reduce the oxide film and thus achieve a lateral insulation of the fins.

- Door installation . A layer of polysilicon is deposited on the fins and up to 3 gates are wrapped around the channel.

Each transistor has two fins and two control gates. Here, the flow channel has a lot of control, but its problem is the space : if the gates are reduced, the space to add fins is less. These fins compose the source and drain to allow more volume in the area, compared to a traditional flat transistor.

The problem comes when we want a smaller lithographic process , an objective pursued by AMD to achieve more performance and more efficiency. Lithography establishes how many transistors go in per square millimeter. At the end of the day, a transistor turns on and off, but to achieve this it has dimensions in the gate that allow the passage of current to be opened or cut off.

The length of the gate is the key to this transistor: the shorter the length, the more precision in controlling the current and the more transistors per square meter. However, this should not be abused as performance may suffer.

Thus, the step of contact of the transistor ( pitch to shrink ) arrived, a solution devised by the manufacturers to improve the transistors. Intel carried out this solution with its latest processors, which resulted in the famous 14 nm ++ process. According to TSMC, the minimum length is 25 nm: if we lower that figure, the performance of the transistor worsens.

FinFET technology is based on Moore’s Law , which allows semiconductor manufacturers to create smaller processors and memory modules, with better performance and consuming less power. It is a technology used mainly in the manufacture of processors, RAM memories and SSDs hard drives.

The future does not go hand in hand with FinFET

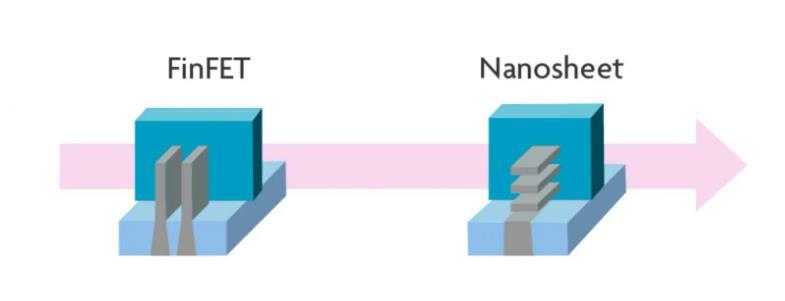

Keep in mind that everything is progressing, and FinFET technology is beginning to become obsolete because it has certain limitations. Thus, Nanosheet appears, a technology in which transistors have their fins stacked vertically , instead of horizontally. Hence the name “nano sheets”, coined by its arrangement similar to that of the sheets of a book.

This transistor would have layers of silicon and SIGe arranged vertically and would be the gate for the standardization of the 5 nm process. Like all new technology, it has initial barriers: its design is complex, requiring an internal spacer to control voltage and drain.

This transistor technology may remain an anecdote, a better one emerging. Similarly, vertical stacking is the way, as we have seen in the HBM2e memory .