The era of wafer dipping and etching is officially over, and while Intel is still somewhat behind when it comes to the technologies used in EUV, their roadmap includes them very clearly. Samsung and TSMC are already working with EUV patterns, but the industry is really worried, as there are challenges to reach 3 nm and especially to lower nodes. How will you create the newest CPU and GPU-perfect lithographic processes? With EUV High-NA .

Is it possible and feasible today to reduce the size of the transistors below the mentioned 3 nm? The industry opens several fronts with ASML at the forefront, while many others are wondering how we are going to create masks for such small wavelengths. What are the problems?

New scanners, new resistor processes and masks with EUV High-NA

There are three main pillars of wafer engraving today and for years to come: the scanners provided by the aforementioned ASML, the resistors for the masks, and the masks themselves.

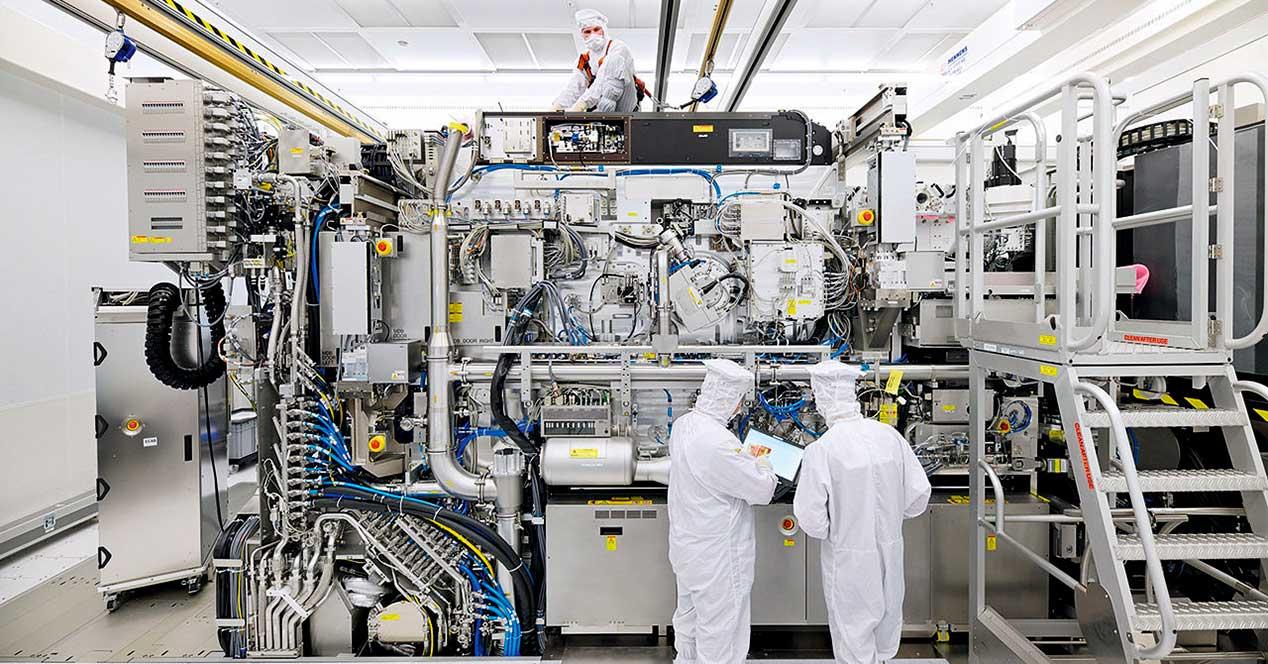

Why are scanners a problem? Mainly because reducing the wavelength of 193 nm is really complicated, since you need a 0.33 numerical aperture (NA) lens with resolutions of 13 nm and with the highest possible performance per wafer.

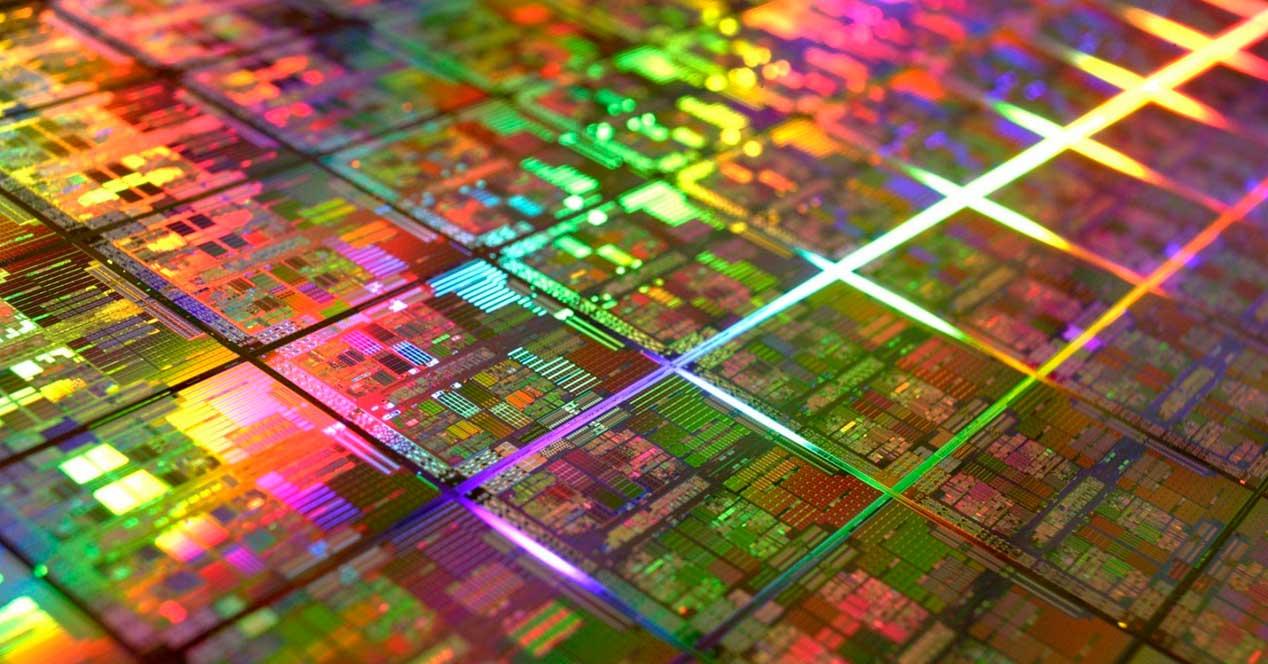

EUV is a technology that works with laser pulses that hit small droplets of tin at a very high speed, which generates photons and these bounce off various mirrors inside the scanner to end up reflected on the mask and then on the wafer, shaping the transistors.

The problem is that the photons do not end up on the wafer, but remain in the mask, or are directly lost around the edges. The solution would be to use films that protect the wafer, but the technology is not ready so, pushed by the competition, everyone has been shot to record at 193 nm without them, which is feasible at 7 nm and future 5 nm.

And this is so because a simple and not multiple pattern is used, since it can have a pitch gate of 32 nm or 30 nm, but reducing it implies changing scanners to reach 3 nm or less. The answer will come back to ASML with a 0.55 NA scanner capable of recording at 8 nm resolutions, a gigantic advance.

These scanners will be colloquially called High-NA and will allow a return to the unique design pattern, reducing costs and progressively increasing wafers per hour. The problem is that for them to work, two masks are required and not one, which have to be sewn together for a wafer due to their complexity.

This will skyrocket the cost, which is already prohibitive today, since, for example, a current EUV scanner is over 153 million dollars , while the High-NA will be over 318 million . Does that mean that the processors will increase in price, as well as the GPUs? It is quite likely if they do not find a solution.

The resistors for the wafers are also at a dead end

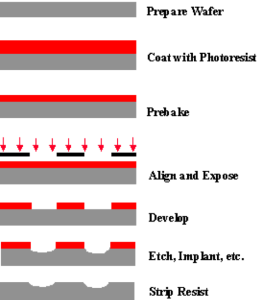

Before creating a pattern for a wafer, it is inserted into a system called a coater, after which photoresist materials are poured into the wafer, which rotates to leave a uniform layer to protect it.

After that the engraving will arrive in the lithography scanner, so it is a very important preliminary process. Currently there are two systems to do this in EUV: chemically amplified or CAR and those based on the so-called metal oxide.

The problem with CARs is that they suffer from blurring of the scanner lens, which does not allow such high resolutions in these, not to mention those that come with NA. Metal oxide resistors are more suitable for these failures, but they are less stable, therefore there is no system that is 100% reliable and above all profitable.

However, a system called dry photoresist is being worked on, a system to remove moisture and improve resolution and stability by coating it in a dry processing chamber prior to exposure to photons. This will be valid for EUV and EUV NA, but it will take a few years to arrive.

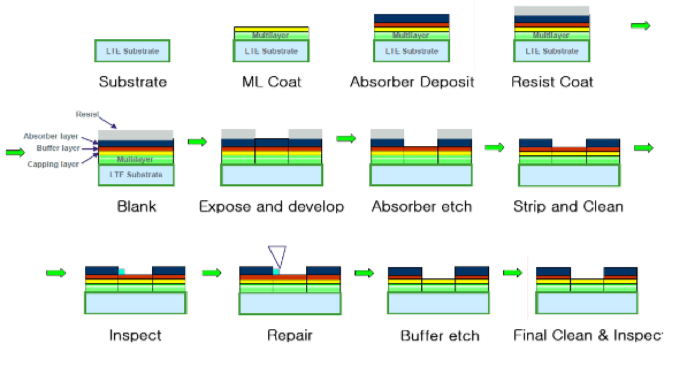

Photomasks are not spared either and have to improve

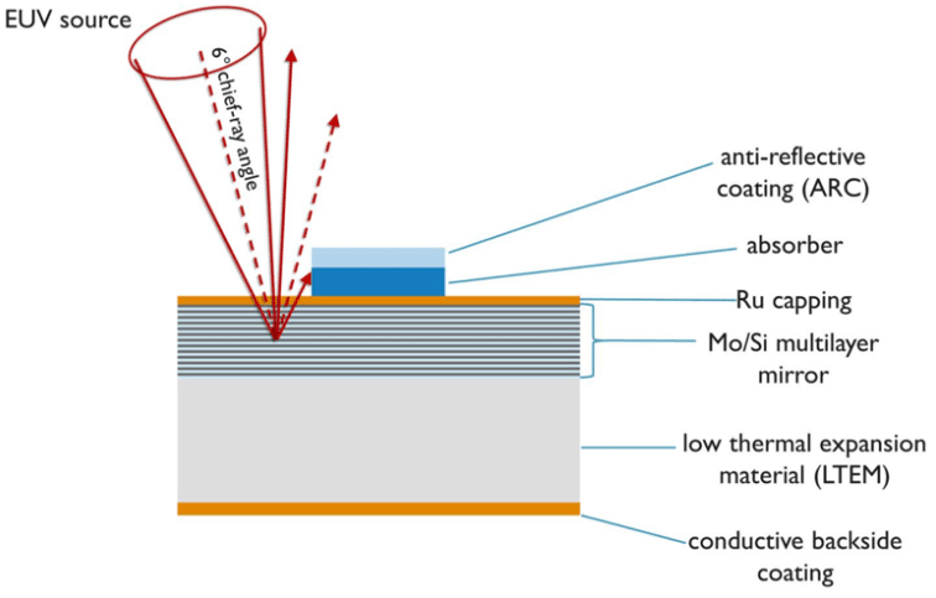

A current EUV mask consists of between 40 and 50 thin layers of silicon and molybdenum on a substrate, giving a total thickness that is usually between 250 nm and 350 nm. Each mask has a component called “absorber” which prevents light bouncing off the wafer and helps a more perfect etching.

The problem is that in an EUV system the light reaches the mask at an angle of 6º , which enhances the fact that it is reflected and the absorbent cannot do all the work, causing possible changes of location in the patterns, with the consequent deterioration of the wafer.

How to solve this? With finer absorbents. The current ones are 60nm and the best and most expensive 50nm, but they are not able to fix this and less at smaller and higher wavelengths. For this reason, researchers are creating two new types of masks for future lithographic processes in EUV: the so – called High-K and the Phase-Shift.

The latter are the simplest, because it only requires changing the absorbent material for one with Low-N properties, leaving aside tantalum. What is sought is to block the light and prevent it from being reflected, achieving dark areas and therefore improving the precision of the images with more basic contrast.

Very little is known about the High-K, but it seems that they can be repaired with a laser, lowering the final manufacturing costs, since the masks are extremely expensive and one is needed for each pattern.

In summary, the 7 nm and 5 nm are guaranteed, but going down to 3 nm is not going to be so easy despite the fact that both Samsung and TSMC and Intel claim to have them ready by 2025 in the worst case.