Obwohl wir zuvor über bestimmte Probleme gesprochen haben, die bestehen bleiben werden Intel und AMD Schlaflos seit Jahren, es ist auch wahr, dass wir es ganz allgemein getan haben, wenn wir uns auf Nanometer selbst bezogen haben. In dieser Hinsicht, und obwohl AMD ein Zuschauer ist, konzentriert sich alles auf den Kampf zwischen Intel und TSMC, die wesentliche Änderungen in der Verbindung vornehmen müssen, wenn sie Nanometer fallen lassen wollen. Welche Probleme haben sie derzeit?

Alles scheint einfach und wunderbar zu sein, der technologische Fortschritt, neue Produkte kommen schneller zum gleichen Preis oder etwas darüber und wir alle freuen uns über Kämpfe zwischen Unternehmen, um zu sehen, wer unser Geld bekommt.

Aber von der hinter den Kulissen Es gibt Hunderte von Ingenieuren für jedes Unternehmen, die ihr Bestes geben, um diese Branche am Leben zu erhalten, denn denken Sie daran, wenn Sie es nicht schaffen, Nanometer zu verlieren, würde die Leistung in einigen Jahren stagnieren und sowohl AMD als auch Intel NVIDIA müsste all ihre Bemühungen auf Techniken wie vertikales Stapeln konzentrieren.

Trotzdem würde das Limit sehr schnell erreicht und wir würden zum ursprünglichen Problem zurückkehren. Daher wird die Branche vom besten Knoten und der besten Architektur dominiert. Das Problem ist, dass sich die Paradigmen in den Wafern von nun an ändern müssen.

Die Verbindung zwischen Wafern, ein neuer Engpass schwieriger Lösung

Wie wir wissen, sind die Schichten der Wafer zusammen mit ihren Masken ein Problem, das die gesamte Branche zu lösen versucht, insbesondere EUV als neue Form der Gravur. Aber wenn die Transistoren immer kleiner werden, wenn die Chips größer werden und vor allem mehr Informationen pro Sekunde verarbeitet werden, beginnt die Art und Weise, dieselben Chips zu erzeugen, an ihre Grenzen zu stoßen.

Das 7-nm-Prä-EUV wird das letzte sein, das die typische anfängliche Materialstruktur für TSMC beibehält. In Intel wird es durch 14 nm ++ und in dargestellt Samsung Es werden auch seine 7 nm ohne EUV sein, die die Spielregeln intakt halten.

Die Verbindungsschichten der Wafer leiden unter ernsthaften Problemen bei den folgenden lithografischen Prozessen, insbesondere zwischen den sogenannten M0 und M1 . Das Reduzieren des Nanometerbereichs impliziert von nun an Beschichtungen zwischen dünneren Schichten, dünneren Barrieren und Metallen mit niedrigeren Widerständen, um die Struktur dieser Wafer zu gewährleisten.

Gegenwärtige Wafer verwenden hochreines Kupfer für solche Verbindungen, aber obwohl Kupfer seit mehr als 10 Jahren bei uns ist (130 nm), ist es gegenüber den zuvor diskutierten Nanometern nicht stabil und Ingenieure suchen nach einem Ersatz, der seine Eigenschaften hat und ihre Defekte minimiert.

Der erste Tab, der verschoben wurde, war Intel, dessen 10-nm-Tab in seinem enthalten ist erste zwei Schichten (das empfindlichste in Bezug auf Struktur und Verbindungen) ein Material, das auch als Kobalt bekannt ist, wobei dieses Material in Beschichtungen und Bindungen verwendet wird. Seltsamerweise verwenden die übrigen Schichten aufgrund ihrer geringeren Kosten und Stabilität, insbesondere in höheren Schichten, wieder Kupfer.

Warum ist Kupfer eine Lösung für ein Problem geworden?

Aufgrund der Eigenschaften des Materials selbst wirkt sich Kupfer mit fortschreitender Nanometerreduzierung kontraproduktiv auf die Verbindungen der Wafer aus: Es diffundiert mit den umgebenden Materialien.

Um diesen Effekt zu vermeiden, wurde es mit einer Schicht als Barriere bedeckt, die aufgrund der genannten Reduktionen so dünn geworden ist, dass sie nicht mehr lebensfähig ist. Es handelt sich dabei um 1 oder 2 nm rubens Lagen Für dieses Material, das das Kupferproblem nicht löst, es nur lindert, und wenn ein Hersteller einer neuen Reduzierung gegenübersteht, ist Perfektion gleichbedeutend mit Lebensfähigkeit für diesen Knoten.

Ein Mangel an nur wenigen Atomen und die Wirkung der Barrieren verschwinden und schädigen die Struktur und Leistung des Wafers, weshalb die Präzision, wie wir sehen, so hoch ist, dass sie keine Methode mehr ist, der wir folgen müssen muss nach anderen Wegen suchen, sie erfordern keine so großen Kosten und es hat so wenig Zukunft. Dazu müssen wir Wärmezyklen hinzufügen, Kupfer ist stark von ihnen abhängig und die Elektromigration fordert ihren Tribut.

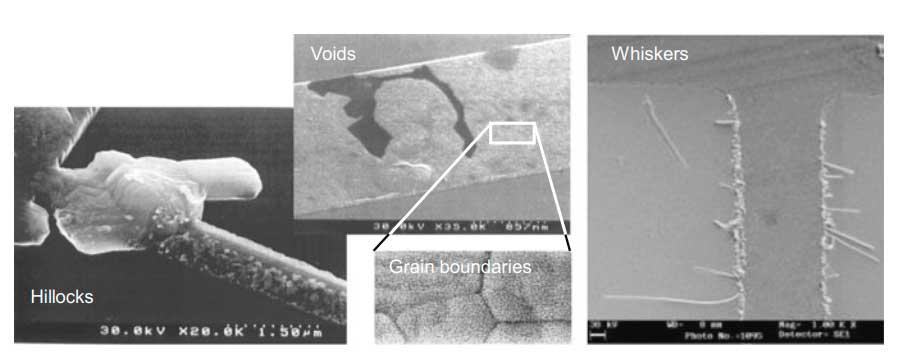

Elektromigration, ein grundlegender Effekt zur Beseitigung von Defekten

Die neuen Materialien, die derzeit entwickelt werden, sollen nicht nur Kupfer als solches ersetzen, sondern auch die Migration von Atomen verbessern. Die Einschränkung in diesem Abschnitt ist entscheidend, da sie verhindern, dass ein Wafer zwischen den Schichten kontaminiert.

Zwei schlecht isolierte Schichten können zweifellos nicht nur den betroffenen Wafer, sondern auch Tausende oder Millionen verderben, da sich der Effekt in jedem einzelnen von ihnen wiederholt. Daher wird der Prozess der Erstellung der Struktur immer komplexer und perfekter.

Aus diesem Grund werden bei der Entwicklung von lithografischen Prozessen zwei Materialien verwendet, wie beispielsweise die 5 nm von Intel oder die 3 nm von TSMC / AMD: Kobalt und Ruthenium. Die Hauptstärken dieser beiden sind, dass sie jede Art von Migration begrenzen, bei der sie als Barriere oder als Leiter wirken können.

Kobalt ist in der Branche als solches nicht neu, aber Ruthenium ist nicht die größte Herausforderung für Ingenieure. Das Problem ist, dass die Hersteller als solche sehr zurückhaltend sind und wir sie fast als konservativ bezeichnen könnten, wenn es um Änderungen geht, was dazu führt, dass die Branche beim Preis von Wafern immer weniger profitabel wird.

Der Kampf wird sich zwischen der Notwendigkeit und dem Konservatismus drehen, der die lithografischen Prozesse der Zukunft definieren kann. Daher benötigt die Industrie im Allgemeinen ein Material, das keine Beschichtungen benötigt und alles erfüllen kann, was Kupfer getan hat, dh alle seine Vorzüge und keine Mängel aufweist.

Kosten sind und bleiben ein Problem, es könnte eine Segmentierung in den Wafern geben

Die Branche, die Änderungen nur ungern umsetzt, die bei früheren Investitionen Milliarden verschlungen haben, wird nicht aufhören, über die endgültigen Kosten nachzudenken, zu denen Sie einen Wafer verkaufen können. Daher und obwohl sie nachgeben müssen, um den Fortschritt aufrechtzuerhalten, wird spekuliert, dass es der Fall sein könnte, dass zwei oder mehr Arten von Wafern demselben Knoten zugeordnet wurden.

Der erste und billigste würde versuchen, derjenige zu sein, der gemeinsame Materialien und Muster verwendet und weniger Innovation aufweist. Die zweite könnte diejenige sein, die mit einem höheren Preis die besten Materialien und die neuesten Verbindungstechniken implementiert und es sogar schafft, Nanometer noch mehr als sein Schwesterwafer zu reduzieren.

Wir sehen heute so etwas bei Samsung und seinen 7 nm bzw. 8 nm, wo Koreaner dank bestimmter Verbindungen und verschiedener kleinerer Optimierungen die Dichte verbessern können. Logischerweise bieten sie zwei unterschiedliche Preise für jeden Wafertyp, so dass wir in Zukunft nicht nur LP, LPP mit unterschiedlichen Transistortypen sehen können, sondern auch Wafer mit unterschiedlichen Dichten, die auf die gleiche Weise mit geringem Unterschied hergestellt werden, Segmentierung, wie sie es nennen .

Transistoren schrumpfen, aber Patchkabel werden langsamer. Wann sind sie ein Problem?

Die sogenannten "Verbindungskabel" werden auch ein anderes Problem haben und sind nur ihre Größe. Transistoren schrumpfen, aber Transistoren bleiben mehr oder weniger stabil und stellen in nicht allzu langer Zeit ein Problem dar.

Die bisher am weitesten fortgeschrittenen offenbar und nach verschiedenen Studien, die veröffentlicht werden, gibt es 12 nm mit dem Tonikum 18 nm für jeden von ihnen. Dies multipliziert mit Millionen von Kabeln stellt eine Gesamtfläche dar, die für 3-nm-Lithografieprozesse zu groß ist.

Die Dichte und damit der Platz für mehr Transistoren pro mm2 kann behindert werden, wenn die Größe und der Maßstab der Verbindungskabel nicht ähnlich wie bei diesen verbessert werden. Obwohl diesbezüglich einige bedeutende Fortschritte zu verzeichnen sind, gibt es keinen Konsens und keine definierenden Beweise, die eine echte Verbesserung in diesem Abschnitt belegen.

Daher ist es ein weiterer Aspekt, den die Industrie gleichzeitig mit den Materialien lösen muss. Hoffen wir nur, dass der Preis pro Wafer nicht steigt und wenn möglich sinkt, damit die Endpreise zumindest nicht steigen.