If you have ever wondered what is the process followed by a processor and the RAM that it has assigned to obtain the data and the instructions that it has to execute then you are in luck, because in this article we are going to explain what this process of communication between what are the two most important elements of a PC communicate with each other.

In this article we are not going to explain what type of RAM is better or the specifications of each one , but a processor communicates with it to be able to execute the programs.

The reason why we use external memory is because the amount of transistors necessary to store the information would not fit in the space of a processor , that is why it is necessary to use RAM memories external to the processor to store the instructions and data that they are going to run.

Why does a processor need communication with RAM?

The stage in which the CPU takes the next instruction to execute from RAM is called “Fetch” and is one of the three stages that make up an instruction cycle: Fetch-Decode-Execute, which we will only talk about in this article of the first one, while the other two will be left for another time since the RAM memory does not intervene in them, except to write the result back.

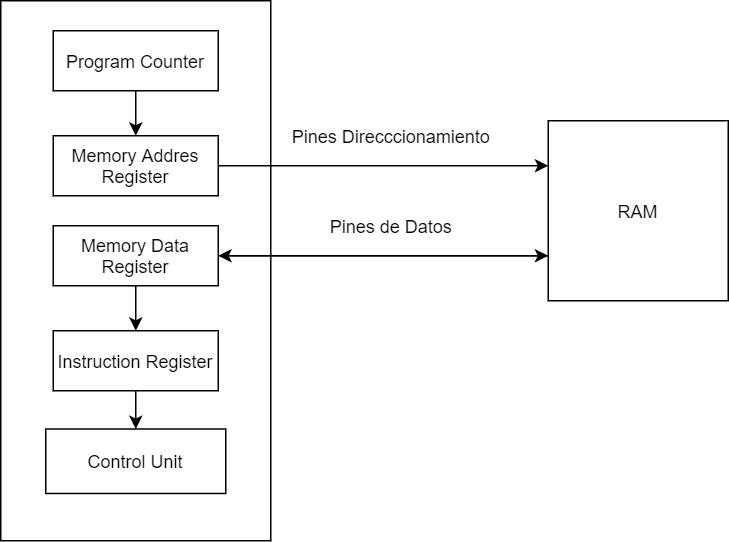

Every processor has a series of registers connected to each other that serve to capture the following instruction, they are the following:

- Program Counter: The PC points to the next memory line where the next processor instruction is located. Its value is incremented by 1 each time a complete instruction cycle is completed or when a jump instruction changes the value of the program counter.

- Memory Address Register: The MAR copies the content of the PC and sends it to the RAM through the address pins of the CPU, which are wired with the address pins of the RAM.

- Memory Data Register : If the instruction is read, then the RAM will transmit through its data bus the content of the memory address to which the MAR was pointing.

- Instruction Register: The instruction is copied to the instruction register, from where the control unit will decrypt it to know how to execute the instruction.

What is DRAM memory?

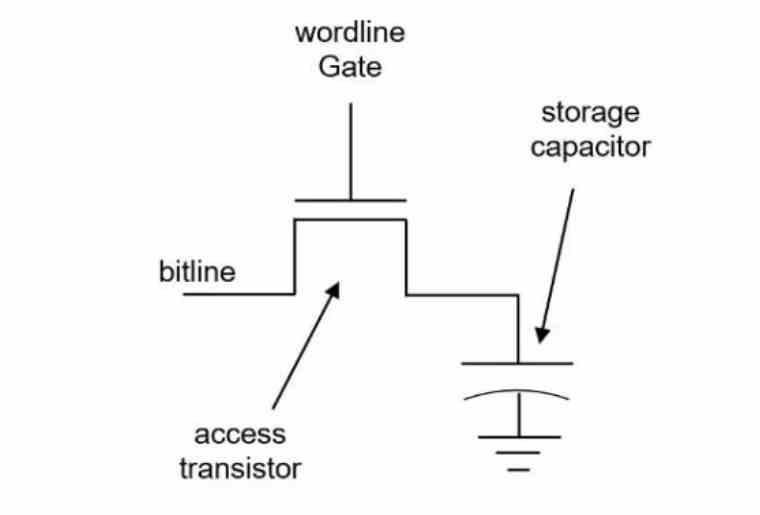

The type of memory used for RAM , both as system RAM and video RAM or VRAM, is DRAM or 1T-DRAM memory . In this type of memory each bit is stored in the combination of a capacitor and a transistor , instead of in several transistors like SRAM, hence the name 1T-DRAM.

All RAM memories currently used in the PC: DDR4, GDDR6, HBM2e, LPDDR4, etc. They are memories of the DRAM type, while the internal memories of the processors, register caches and scratchpads, are of the SRAM type.

Said combination of a capacitor and a transistor is called a bitcell , when the bitcell’s capacitor is charged then it is interpreted that the information contained in that bit cell is a 1, when it is not charged then it is interpreted to be a 0.

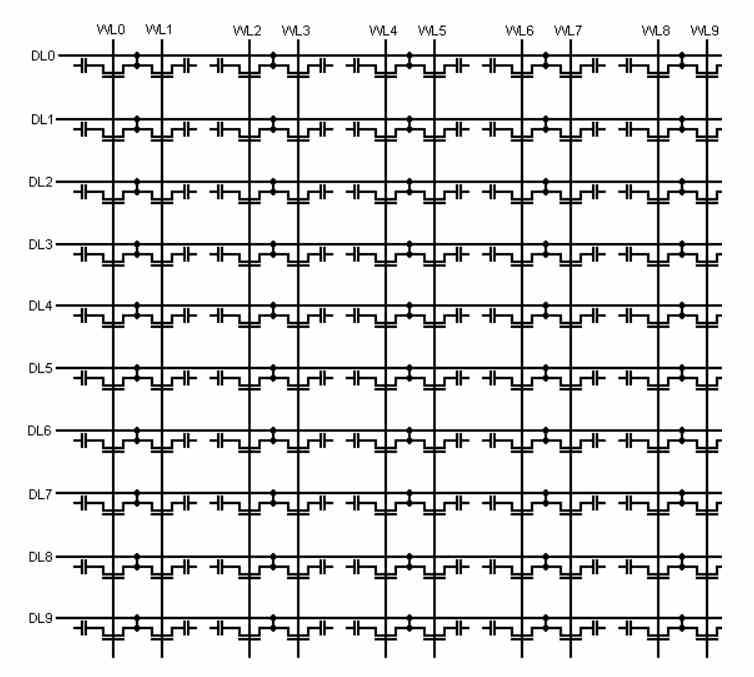

The bitcells are organized in a matrix where the addressing pins are used to access them as follows:

- The first half of the bits select the row we want to access

- The second half of the addressing bits contain the column we want to access,

For this, there is a binary decoder between the matrix of bitcells and the addressing bus that allows selecting the appropriate bitcell.

The contact pins for communication with the RAM

To access the RAM, the CPU uses a series of pins that allow it to access the contents of the RAM and even modify it . To do this, you first need to locate where the data is or where we want to manipulate it, and then transmit it in a specific direction. Two different types of pins are used for this.

- Addressing pins : Normally marked from A0 to AN, where N is the number of pins and equals the number of addressing bits, which is always 2 ^ N.

- Data pins : It is where data is transmitted to and from RAM.

- Write Enable: If the pin is active, the data transfer is made towards the memory, writing, on the other hand, if it is not active, it is done towards the processor, reading.

If our system has several RAM memory chips then the first bits of the addressing are used to select which of the memory chips we want to access within the DIMM memory module. There have also been cases where the address and data pins are the same. This is due to the fact that the addressing and access to the data is not done simultaneously.

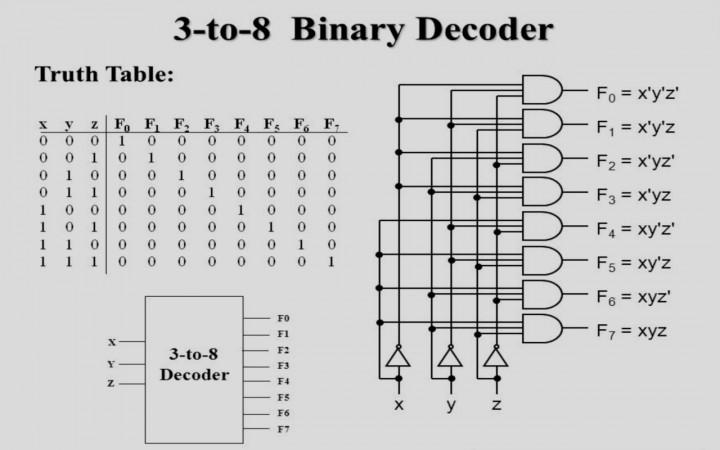

But to understand how addressing works more precisely then we have to review a basic piece of electronics, the binary decoder.

The binary decoder and its role in communication with RAM

The binary decoder is a very common piece of electronics, they consist in that from an input of n bits an input is selected from 2 ^ n different possibilities. It is built by placing n NOT gates to 2 ^ n AND gates.

The binary decoder is a very common piece of electronics, they consist in that from an input of n bits an input is selected from 2 ^ n different possibilities. It is built by placing n NOT gates to 2 ^ n AND gates.

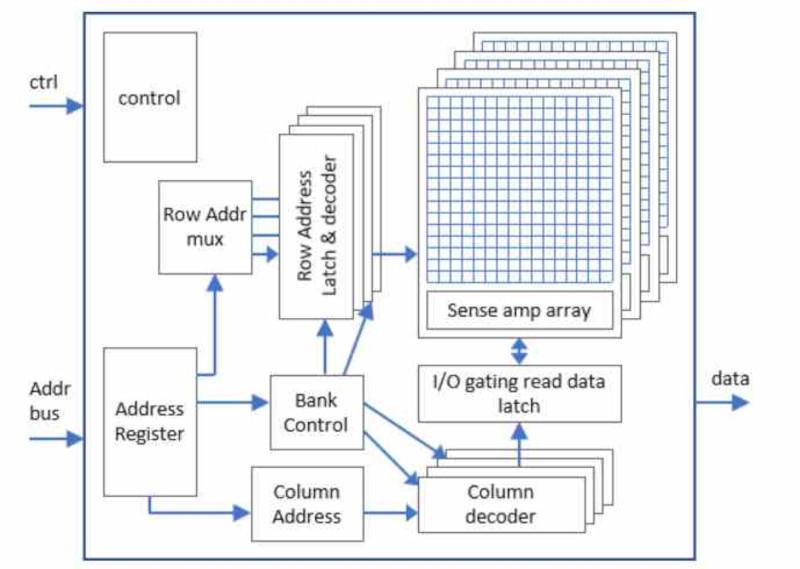

In RAM memory, addressing is transmitted in two cycles: first the row to be accessed is sent and then the column, instead of simultaneously.

The reason for this has a very simple explanation: imagine that you have a processor with 16 addressing bits connected to a single RAM memory chip. If the binary decoder were 16 bits then 16 NOT gates and 65536 AND gates would be needed. In contrast, an 8-bit binary decoder has 8 NOT gates and 256 AND gates, much easier to implement.

This is the reason why addressing to RAM is done in two stages.

Memory Banks

The data in RAM is not stored successively , but in different banks within the same chip, each of the banks contains an array of bitcells , but if we want to transmit for example n bits of data we will need n arrays of bitcells where each one of them is connected to a pin of the data bus.

The use of multiple banks , in the same memory chip, allows to select several bits at the same time with a single access to the memory , since all the banks share the addressing . So if we have 8 memory banks, selecting a specific bitcell will end up causing the data to be transmitted to and from the 8 memory banks at the same time.

The standard size of banks in RAM memories is 8 bits, hence the maximum memory in addressing is always counted as 2 ^ n bytes. Actually the 16, 32, 64 bit buses, etc. What they do is transmit the data of several successive memory addresses starting from the first.

Communication between RAM and CPU

Communication between the CPU and the RAM depends on it being done correctly, that is, the correct data is sent, in the correct direction and in the correct memory bank. Therefore, all RAM memory has a window of opportunity, which is the time in which the different operations can be carried out, these have to be carried out at specific times and following this process:

- Select column (Addressing)

- Select row (Addressing)

- Data transmission.

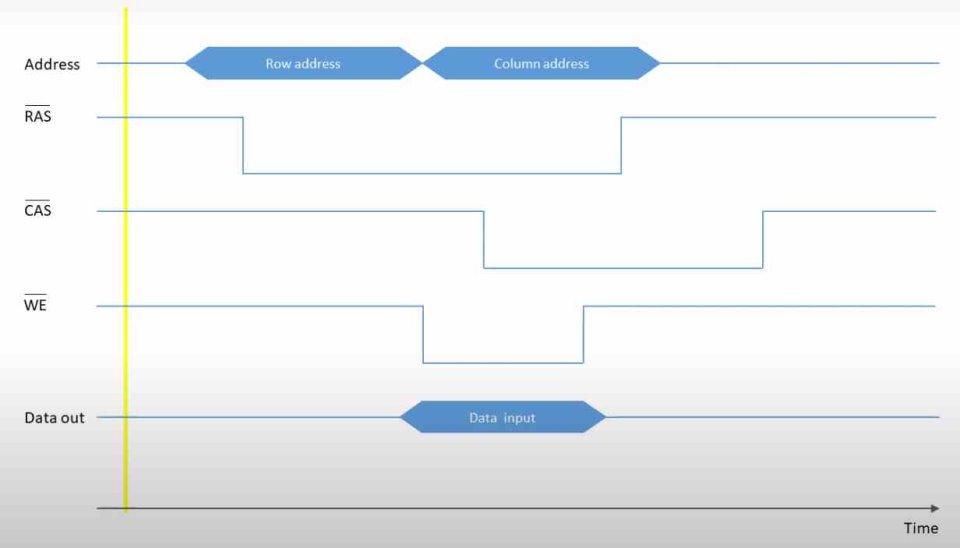

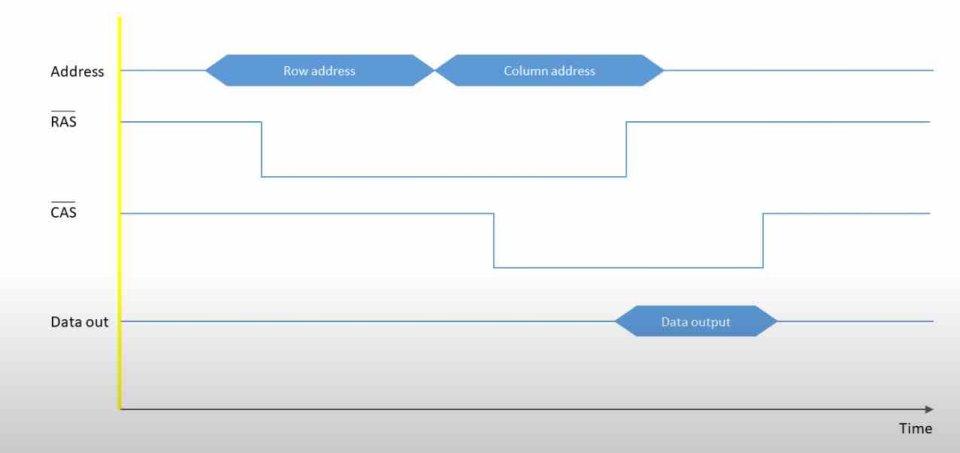

For this, a series of special pins are used, one of them we have already seen and it is Write Enable but the other two are the following:

- Column Access Strobe: This pin is activated when we indicate to the RAM memory that we are indicating the column we want to access.

- Row Access Strobe:: This pin is activated when we indicate to the RAM memory that we are indicating the row we want to access.

Both operations can be summarized as follows:

- The reading operation is very simple, for this you must have the WE pin inactive, to indicate that the data goes from the RAM to the processor, indicate the row and and then the column so that the information flows towards the processor from the memory RAM.

- The write operation is somewhat different, for this the WE pin must be active, but the data is not transmitted after selecting the data column but once the row has been selected and simultaneously with the selection of the column where it is located the data.

With this you can already get an approximate idea of how the communication between a processor and its RAM works.