The future of any current processor is in question. We are reaching certain limits that are straining the expertise of transistor architecture engineers to achieve scalable advancement for the next few years on any type of chip. We usually talk about Intel, TSMC or Samsung and their evolutions, but IBM and CEA-Leti also have a lot to say, since, although they have taken different paths, their conception of the new transistors is interesting and will be based on two different concepts: AS -Late and GAA 7 Layer.

IBM has always had a reputation for being a leading technology company in the industry and although it is often put after Intel, the truth is that in many fields it is much more advanced than this. In transistors, a fundamental part of any chip in the world, his IBM Research team presented a new work on nanosheets called AS-Late.

Air pockets around a Gate (AS-Late), the definitive step to slow down the nm?

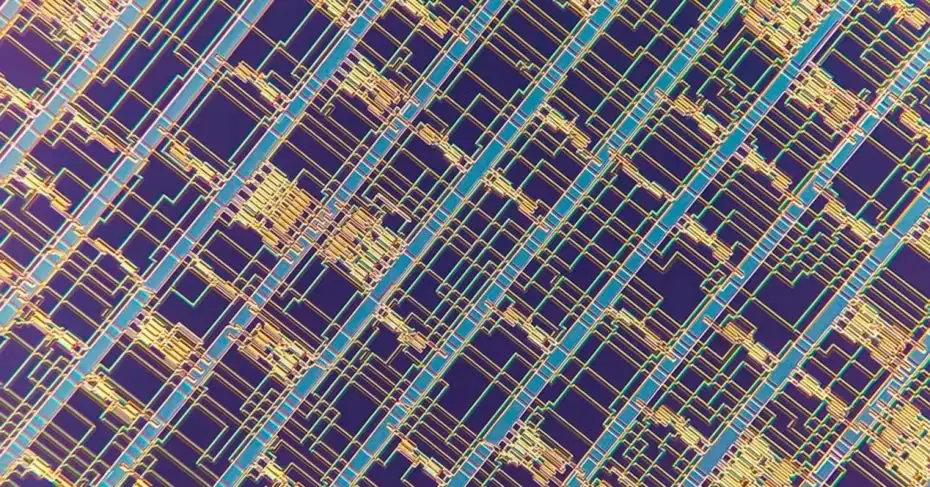

What was discovered by IBM was worked on based on a specialization of nanosheet technology, where they discovered that by creating a kind of bag around the gates, each transistor consumed less power and achieved better performance, which translated into higher final performance.

The company called this air spacers, because really that is their function, to add a physical space, where the best thing is that it is universal for any transistor architecture, with the consequent repercussions that this entails. The finding is of such caliber that IBM showed that it is better to apply this technique than to reduce its node from 7 nm to 5 nm, since it was possible to gain performance and consume less energy per transistor , so we can already get an idea of the importance that this could have in the industry.

The secret is in reducing the effective capacitance, a process that reduces the performance of the transistor from the point of view of efficiency and that with the air spacers it is possible to reduce it by 15% . The process to get there is quite simple from a conceptual point of view, but very complicated to do at the atomic level.

The spacer is a physical isolation between the gate and the contacts of each transistor, so that this space works like a switch. When the door is opened to favor the passage of current, electricity flows and the spacer ensures that the door itself controls the flow, while keeping the other adjacent parts of it isolated.

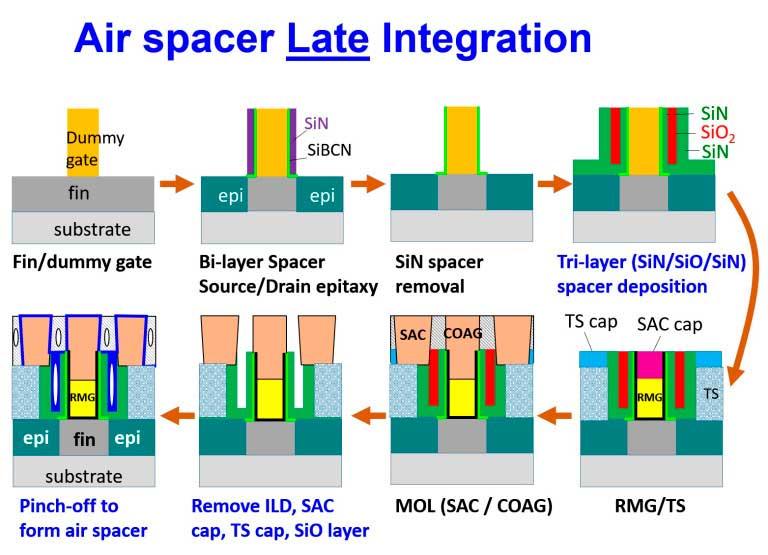

Due to its operation, the technique has taken the name air spacer early (AS-Early) and has an even more advanced version called AS-Late, where the formation of the spacer is carried out not at the beginning of the creation of the transistor, but at the end. so according to IBM it is more scalable.

GAA 7 Layer, CEA-Leti’s bet for nanosheets

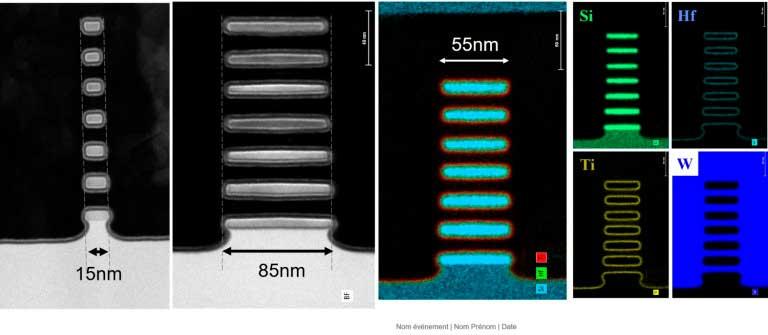

The company, unlike IBM, sees the transistor market as Intel and TSMC. For them FinFET is the past and now comes a new future with GAA. In their development of this technology by layers or also called sheets, their engineers managed to create transistors with seven levels of silicon stacked vertically.

This in itself is worth mentioning since it means doubling the number of sheets per transistor, but the most incredible thing is the widths achieved, since they range from 15 nm to 85 nm.

What CEA-Leti was looking for is to improve current carrying capacity and transistor drainage. Thus, they claim to have achieved figures of 3 mA / μm at VDD = 1V and a drain three times higher than current. This is possible by increasing the number of stacked channels.

A higher number implies a higher drive current and with this a much more effective performance is possible, to the point that they are currently at the forefront in this field, well ahead of Samsung and Intel. The future according to the company to modulate this fact, so that depending on the performance to be achieved, the width of the nanosheets can be changed, allowing more flexible designs, something that in FinFET is impossible.

As we can see, everyone is pressing for one side or the other. TSMC may have found a solution similar to AS-Late and thus follow in FinFET up to 3 nm , who knows. In any case, in no more than three years we will be with GAA in the market, because on this there is unanimity in the sector: FinFET is dead, long live GAA.