Apple has crashed the TSMC 5nm deliveries and seen the performance of the A14 and the future Kirin 9XXX, where in both cases the performance has barely taken off, consumption has barely been reduced and in general, the improvements seem less than expected. , about the air warps a question, Is the N5 a TSMC failure? What will AMD do if the high-performance version does not achieve the expected improvements?

TSMC could say that it has triumphed with 7 nm in all areas, since it is the star node of the moment in many sectors. But their N5s do not look so good, especially if we take into account the measurements of many SoCs such as Apple and Huawei, what is happening?

Very slight improvements in a process that is not high performance

The seen with the A14 made us wonder, what is happening with Apple? when the question really is, what’s going on with the TSMC N5s ? The improvements to the Apple chip, being its first exclusive ARM version with an equally exclusive node, left us cold. It is not that the chip is bad in itself, because it is not like that, but the improvements compared to the A13 after the architecture changes and the jump in nanometers made us think of a much higher performance in all areas.

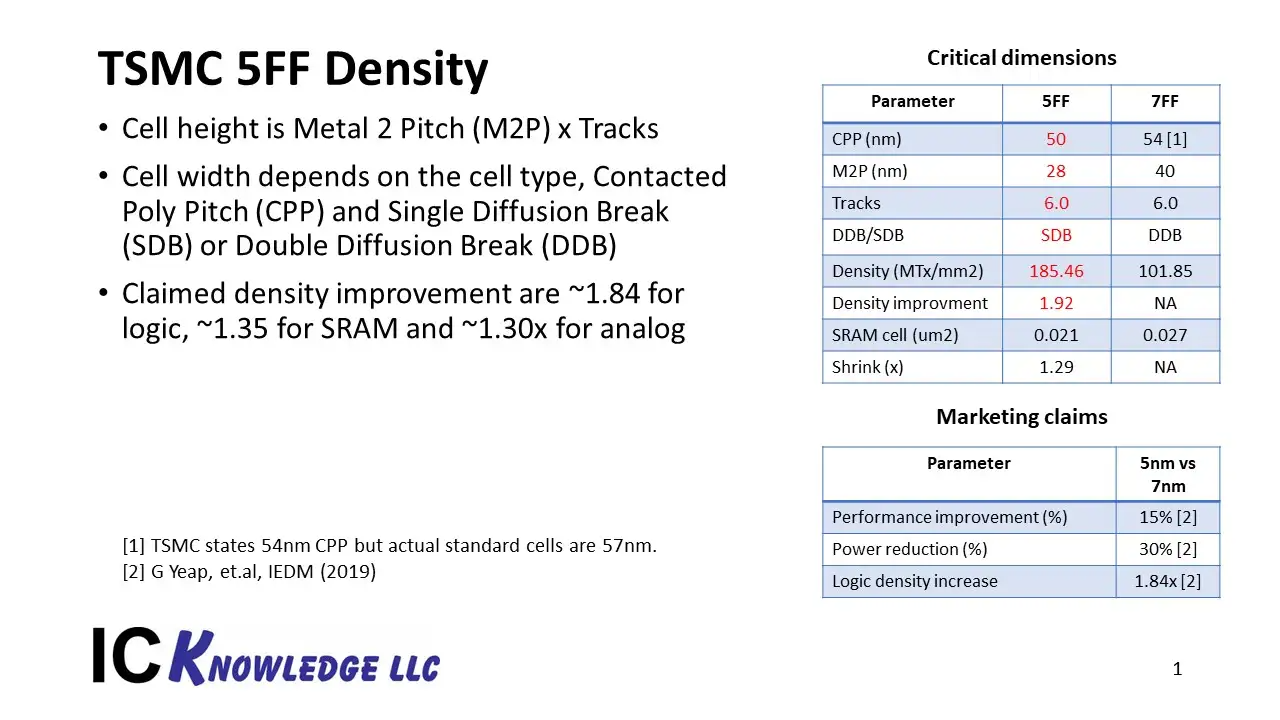

The problems seem to be derived from EUV, where the higher number of layers may be hindering what a priori did not seem like a problem and is nothing more than achieving greater efficiency and higher performance. Historically Apple has always boasted of reaching at least 90% of the theoretical density of the node in which it was working, but with the A14 there has not been a review about it until asked.

It turns out that, after some interview, the A14 at 5nm has only achieved 78% effective transistor density , which implies a serious total loss in the whole chip.

Are we facing an N5 node fiasco to continue in FinFET?

It’s not really clear, it may be the highest number of layers, it may be that FinFET is no longer as optimized under EUV and that much layer or it may just be that Apple has not adapted to the node. In any case, it must be remembered that the TSMC itself spoke of a reduction of 1.84X, but the A14 is well below with 1.49X.

Intel and Samsung are already working with GAA on nanosheet and TSMC is taking FinFET to the limit of its useful life with 3 nm. If 5nm is a transition node and the high-performance variant is going to suffer from the same problems, maybe AMD should rethink using this node if there are no significant changes versus 7nm.

It should be remembered that Intel is going strong with 10 nm SuperFin , that AMD has had to launch Zen 3 and RDNA 2 in 7 nm without + and that EUV could be the temporary solution in those 7 nm if they finally skip the 5 nm high performance.

And it is that not everything is density as we are seeing, the design of the cells, the height, the gates and an endless number of connections is as important or more than simply getting more transistors per square millimeter.