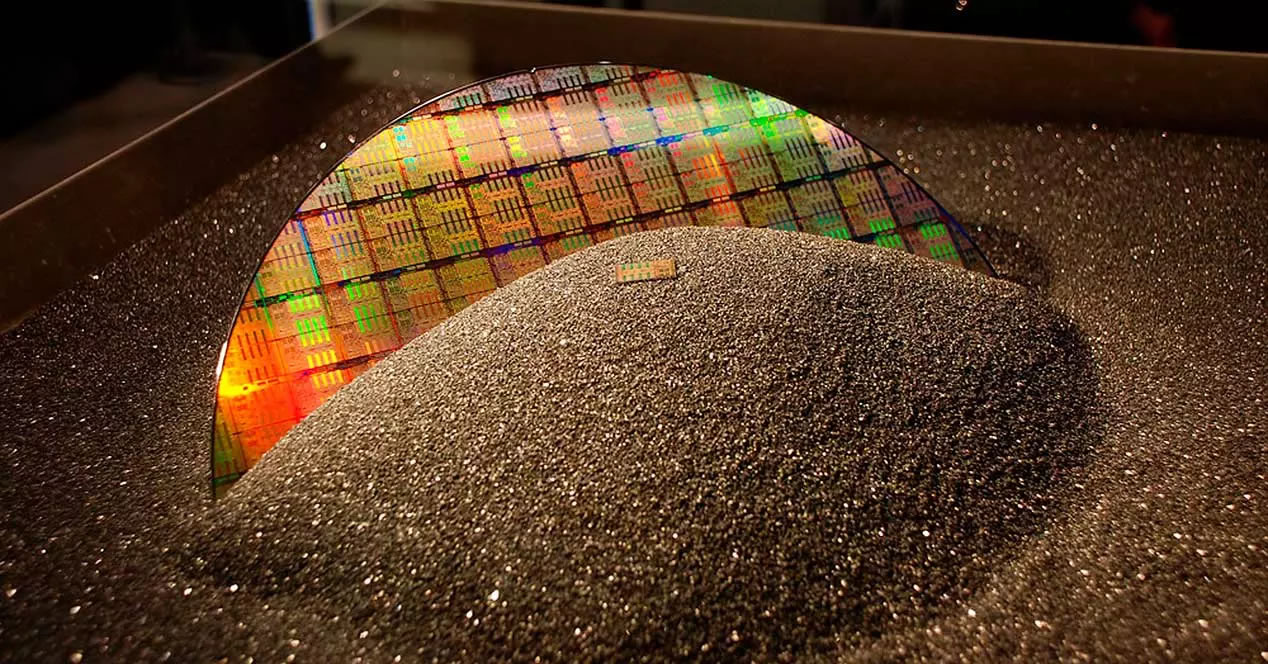

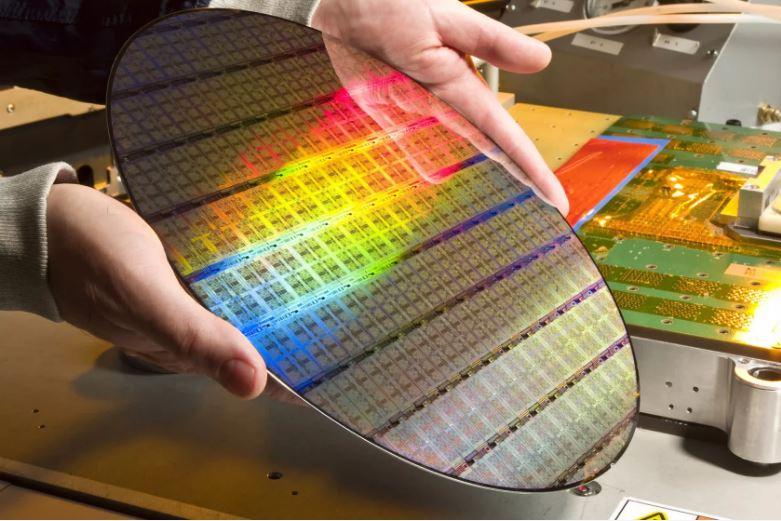

Vi tenderar att se framåt, men sällan ser vi tillbaka. Ibland är det mer än bekvämt att veta vart vi ska och vad vi har lärt oss, eller helt enkelt förstå varför saker är så här. I wafers värld, av deras sammankopplingar och paket, förändrade en generalistteknik allting, så att utvecklingen av den nu för tiden används för att skapa från högpresterande processorer till mobila SoC. Vi pratar om InFO, en teknik som utvecklats av TSMC .

För att utvecklingen av processorer och chips ska kunna ske krävs en grund för att bestämma prestanda och kapacitet för den nya tekniken som de kommer att vara värd för. Även om en ingenjör har i åtanke hur dessa bör hanteras i många år framöver, är sättet att göra det det riktigt komplicerade steget. Vi har sett hur industrin vänder sig mot chipletter, men även om de är en verklighet som gradvis tar över marknaden är en av de viktigaste teknologierna och begreppen lite känd. Hur kom vi hit?

InFO och dess två varianter PoP och oS är nyckeln till evolution

Innan vi dyker in i själva tekniken måste vi veta vad InFO är. Som sådan är InFO förkortningen för Integrerad Fan-Out , vad som i branschen ofta kallas för wafer-level-förpackningar, som översatt skulle komma som en teknikplattform för systemintegration.

Det vill säga en metod för att lägga till delsystem eller komponenter till chipsen som redan finns i själva skivan. Ett tydligt exempel är HBM inuti vilket chip som helst i vertikalt format (inte horisontellt som GPU: er som behöver ett substrat eller interposer, förväxla inte dem) även om någon typ av DRAM också skulle fungera, till exempel.

För att integrera ett delsystem eller en komponent på skivnivå kommer det att vara nödvändigt att använda hög densitet RDL (Re-Distribution Layer) och även TIV-teknik (Through InFO Via) att göra sammankopplingarna mellan båda lagren utan att förlora prestanda. Processen innefattar att skära flisen från en kiselskiva och sedan placera dem mycket exakt på en tunn "rekonstituerad" eller bärskiva som sedan formas. Omfördelningsskiktet skapas och sedan bildas lödkulor ovanpå, som i ett skivpaket på skivnivå. Därefter bakas den nya skivan som bildas av flis så att föreningen härdas och den skulle vara redo för produktion.

Varianter handlar om att kunna designa 2D- eller 3D-chips

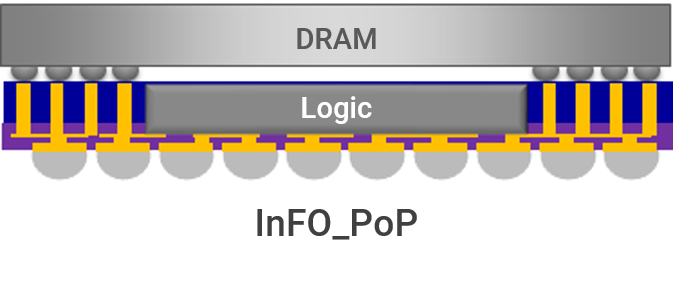

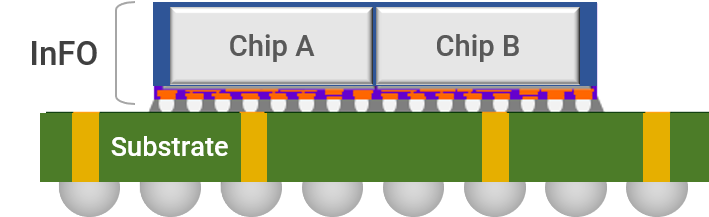

Som vi har diskuterat har InFO två varianter som, beroende på chipets design och dess komplexitet, kan användas för dess skapande på skivan. Vi pratar om PoP och oS, där var och en har sina särdrag och för tillfället och trots att de har använts sedan 16 nm, slutar ingen av dem påtvinga den andra som en tydlig dominator.

InFO_PoP är det första Fan-Out-paketet för branschen inom 3D wafer-konceptet. Det är det mest använda vid integrering av komponenter som matriser, DRAM eller mellanliggande substrat för fler lager. Det har särartet att använda finare svetsar, vilket ger en tunnare slutprofil och bättre elektrisk och termisk prestanda på grund av att det saknar ett organiskt substrat.

Å andra sidan behöver InFO_oS ett substrat för att kunna ta form, där den normala höjden kommer att vara cirka 2 mikrometer. Fördelen är att genom att inkludera substrat kan fler marker vara sammankopplade med det och det beror inte på något så individualiserat som PoP-metoden. Att ge I / O- eller ingångsmätningar är komplicerat, eftersom varje företag har sin egen och varje nod kräver en storleksändring av samma, men i alla fall pratar vi alltid om mikrometrar.

Det är denna teknik som har tillåtit Intel och TSMC att avskaffa Moores lag i ytterligare några år, om än genom att skala fler-wafersystem.

InFO-L / LSI, det ultimata inom systemets skalbarhet

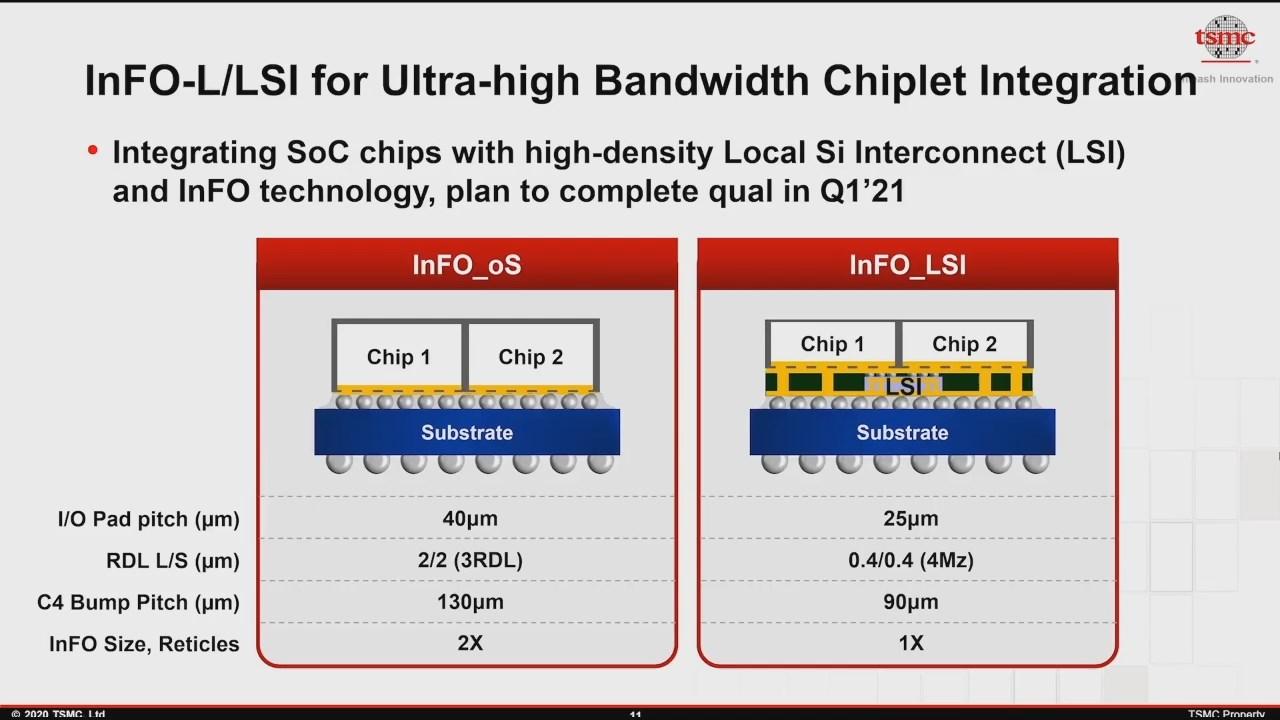

En ny teknik inom InFO borde närma sig slutförandet för att massproduceras redan 2022. Vi talar om InFO-L eller InFO_LSI , som du föredrar, där ett sammankopplande skikt av kisel är integrerat mellan substratet och chipsen som förbättrar aspekter som integriteten hos signalerna och till och med spänningarna eller temperaturen, eftersom de kräver lägre värden.

Problemet är att flisen måste vara utformad med en lägre tjocklek för att inte höja formens totala höjd, vilket termiskt begränsar spridningen mellan skikten. Detta är intressant när det gäller GPU or CPU kärnor plus HBM i någon av dess varianter.

Att lägga till höjd begränsar de maximalt acceptabla värdena, som vi såg till exempel i i9-9900K eller i Radeon VII, så det är inte något att verkligen förakta. Nya marker som kommer ut från fabriken måste göra detta, så det blir intressant att se hur mycket de stiger i förhållande till det ursprungliga substratet.