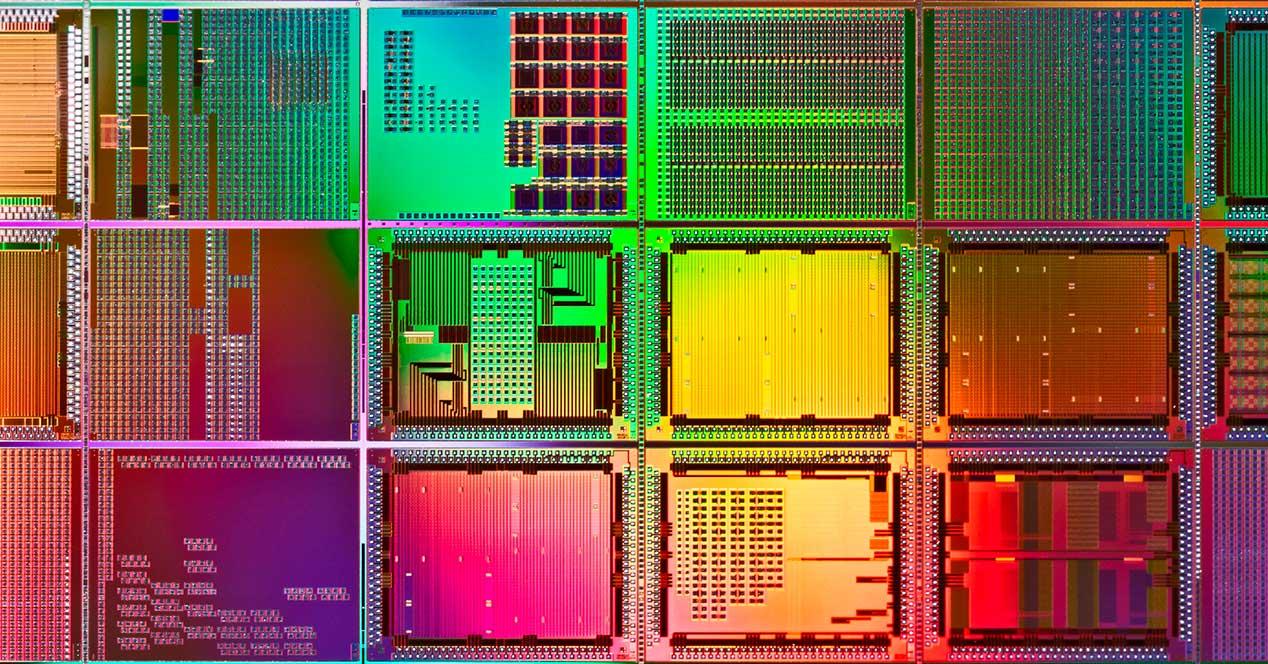

O mercado tem como alvo os chips, ou pelo menos é o que parece. AMD está com seu acordo baseado em MCM há alguns anos e Intel está prestes a dar o próximo passo com tecnologias como Foveros, mas isso é uma jogada imperdível? Já conhecemos suas vantagens e desvantagens? Hoje veremos o que há de bom e de ruim nos chips e por que a indústria não vê essa maneira de criar CPUs com tanta clareza.

Todos os principais, incluindo AMD, Intel, TSMC e Marvell estão trabalhando em diferentes abordagens para o mundo dos chiplets, diferentes alternativas tentando desenvolver projetos mais avançados. Embora nos artigos anteriores tenhamos lidado com esse tópico específico, há alguns pontos que deixamos para esta ocasião, já que o setor não tem tanta certeza de que os chiplets são o caminho a percorrer.

Falta de ecossistema, padrões, tempo e custos de desenvolvimento

Nem tudo o que reluz é ouro e, embora a AMD seja uma das poucas que estão lançando produtos reais no mercado baseados em chips, não é exatamente fácil fazê-lo. O problema é que não há ecossistema, não existem padrões fixos que a indústria possa seguir para reduzir o tempo de criação e os custos de desenvolvimento.

Cada empresa está enfrentando, mais ou menos, seus problemas individualmente, unitários, mas nenhum deles separadamente possui todas as peças para formar o quebra-cabeça. Em vez disso, e com curiosidade, todos eles enfrentam quase os mesmos problemas:

- Eles tentam oferecer chiplets ideais e com conexões melhores e mais rápidas que podem ser dimensionadas para diferentes produtos.

- Eles precisam de tecnologias de terceiros em maior ou menor grau.

- Falta de apoio nos desenhos dos esquemas de interconexão entre matrizes.

- Eles precisam de IPs corretos com recursos de fabricação.

Isso está fazendo, por exemplo, a Intel seguir seu caminho com base em monodie para suas CPUs, algo que veremos por alguns anos. A AMD foi pioneira, mas está pagando grandes custos porque depende de terceiros e, por sua vez, de empresas especializadas para determinadas técnicas que precisam ser desenvolvidas exclusivamente, aumentando os custos gerais.

As ferramentas de EDA são necessárias para unir todas essas peças, pois são diferentes arquiteturas e produtos, interfaces físicas e lógicas para unir e classificar informações de várias empresas para lançar um único produto. Além disso, alguns componentes principais podem não estar disponíveis, exacerbando o problema.

O setor precisa compartilhar IPs diferentes se quiser avançar com chiplets

![]()

Não há mais cego do que aquele que não quer ver. Um ditado que parece não gostar de certos setores da fabricação de PI para grandes empresas. O investimento é feito e o caminho deve ser compartilhar pelo menos uma série de interfaces padrão para a integração de chiplets, algo que os prejudicará seriamente economicamente.

O exemplo a seguir é simples: os NVDs, SSDs SATA ou a própria DRAM. Eles usam a mesma interface, para que as diferentes partes não precisem conhecer os detalhes das outras, pois elas sabem o que aderir e como devem ser o design dos PCBs, das conexões e dos chips.

Eles economizam custos, tempo, otimizam saldos financeiros, produzem muito mais e melhor, mas o mais importante é que todas as empresas competem nas mesmas condições, promovendo a competitividade do próprio setor.

Nesse sentido, e como poderia ser de outra maneira diante desse caos, as grandes empresas estão desenvolvendo a base desses padrões tão necessários, tecnologias de interconexão com interfaces abertas para que as empresas se unam à sua causa.

Tanto que atualmente a disputa será entre quatro candidatos ao título: AIB, BoW, OpenHBI e XRS onde, além disso, o ODSA está desenvolvendo por sua vez os chamados Chiplet Design Exchange ou CDX , um formato aberto para a troca segura de informações mantém a confidencialidade e mantém fluxos de trabalho e informações para protótipos.

Com ele em mente, tentamos organizar as diferentes interfaces para começar a criar um sistema confidencial heterogêneo que projeta gradualmente chiplets mais facilmente e com base no padrão que acaba sendo imposto. Pode ser que não haja um único vencedor, já que o setor precisa inovar de pelo menos duas maneiras, mas pelo menos seria o primeiro passo para ter um objetivo comum para todos.

A criação dos chips e suas interconexões também requer unificação de critérios

Se o quebra-cabeça já era difícil de resolver, lembre-se de que os desenhos das interconexões (também conhecidas como saliências ou microbombas) também não são definidos como padrão. Cada empresa cria seus solavancos e suas embalagens, portanto, como não há padronização nisso, são necessárias ferramentas específicas para a verificação, criação e supervisão das bolachas, tanto para os chips quanto para os interposers.

As etapas são quase todas automatizadas, onde as bolachas passam várias horas de testes, testes e monitoramento com conteúdo elétrico, físico e visual. Como esperado, interconecta usando microcolisões são muito maiores em tamanho físico em chiplets do que em matrizes monolíticas, onde podem atingir de 25 a 40 mícrons.

Para se ter uma idéia, e tomar uma bolacha típica de 300 mm, verificar cada conexão de microbombas é como localizar a cabeça de um alfinete em um campo de futebol, de acordo com o vice-presidente do FormFactor. A precisão é incrível e isso significa que, sem um padrão, os custos continuarão a crescer para todos, uma vez que a nova microbomba se aproxima 10 micrômetros , e os testes não pararão de subir de preço devido à imensa precisão necessária para os testes correspondentes.

Então, e em resumo, é uma vantagem ou uma desvantagem seguir o caminho dos chiplets? É muito bom ver o mar da costa e sermos impactados por cada lançamento ou tecnologia projetada pela Intel e pela AMD. Mas debaixo d'água o setor não é tão claro e, embora as etapas a seguir estejam sendo definidas, as de Swan, por exemplo, não deixarão as CPUs monolíticas de lado até que toda a indústria possa ter uma série de padrões a seguir.

A AMD terá que suportar o peso de tudo o que foi dito e nas mãos da TSMC, onde, como já comentamos mais de uma vez, os preços de seus processadores terão que subir mais cedo ou mais tarde para permanecer lucrativos e, acima de tudo, aumentar o margem de lucro. Não vai ser um Liso jornada para qualquer um dos dois gigantes, a Intel EMIB, Foveros, AIB e Co-EMIB , TSMC em desenvolvimento com Sistema em Chip Integrado (SoIC) e a AMD tenta combinar as novas arquiteturas com base em várias empresas que fornecem o necessário para esses chips.

Se alguém pensava que isso era costurar e cantar, estava muito errado. O futuro não é negro, mas exige acordos e perdas de longo prazo que todos terão de suportar.