De litografi på sjetongene som brukes i prosessorer, som vi kjenner dem, har lenge vært i en kamp for å redusere produksjonsprosessene, og vi ser at nanometer blir mindre og mindre. Imidlertid når det gjelder 3D NAND-minne , den har blitt "sittende fast" på 40nm i ganske lang tid nå, og trenden er at den skal forbli slik i det minste på mellomlang sikt. Hvorfor forbedrer de ikke litografien av minne? Vi vil fortelle deg alt nedenfor.

3D NAND-teknologi ble først introdusert i 2013, og Samsung gjorde en god jobb med å forbedre den i 2015; Men siden da har verken Samsung eller konkurrentene gjort ytterligere forbedringer av dette minnet utover å skape flere og flere lag for å øke tettheten. Så hvis 3D NAND-minnet er 40 nm, hvorfor ser vi ikke forbedringer med mindre noder som 32 nm, 20 nm osv.?

Svaret er at det er nesten umulig å redusere litografi på grunn av hvordan spesifikt kommunikasjonskanalene mellom lag blir produsert, og vi vil forklare det nedenfor.

Slik produseres 3D NAND-kanaler ved 40 nm

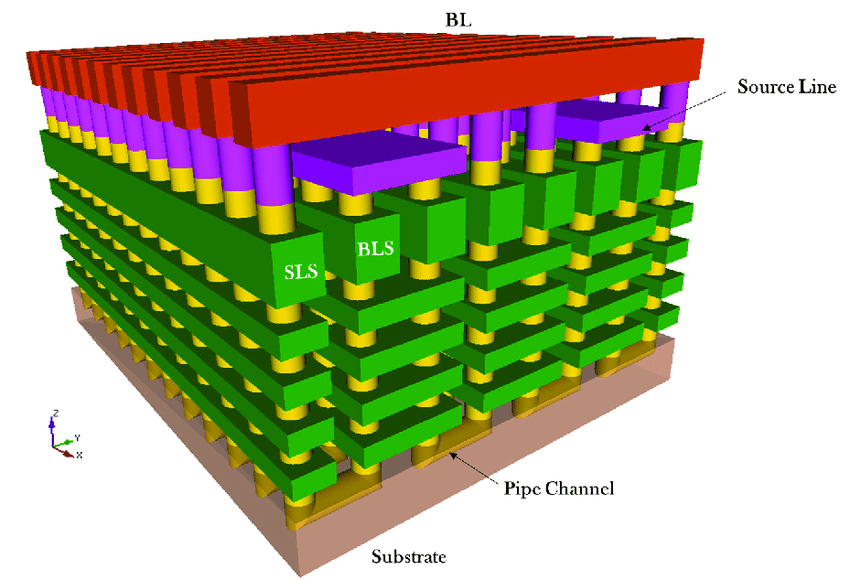

For å forklare hvorfor litografien til 3D NAND-minne ikke kan reduseres mye mer, vil vi bruke Toshibas BiCS-struktur (nå brukt av KIOXIA) som et eksempel.

- For det første lages det veldig smale hull i alle lag av 3D NAND. I dag har disse hullene et sideforhold på omtrent 60: 1, noe som er ganske bemerkelsesverdig. Tenk på at for dette litografiet vil et hull på 2.5 cm i diameter være 1.5 meter langt. Disse hullene er slik, med vegger nesten perfekt parallelle fra topp til bunn som går gjennom alle materiallagene og som tjener til å kommunisere med hverandre.

- Disse hullene blir deretter fylt med stor presisjon med 5 lag materiale:

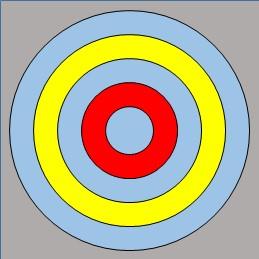

- Det opprinnelige laget er silisiumoksid (SiO2), noe som gjør hullet enda smalere. Dette vises i lyseblått i diagrammet som vi skal sette nedenfor.

- Deretter dekkes det med et annet tynt lag silisiumnitrid (Si3N4) også fra topp til bunn, noe som gjør hullet enda smalere. Dette er ladingfangstlaget og vises i gult.

- Det er et veldig tynt tredje lag av SiO2, noe som gjør hullet enda smalere.

- Det neste laget er ledende polysilisium. Dette laget vises i rødt og fungerer som dataoverføringskanal.

- Til slutt er den lille plassen som er igjen fylt med SiO2 (blå) igjen. Dette siste isolasjonsfyllstoffet hjelper til med å "tynne" kanalen slik at den fungerer bedre og er mer stabil.

Tykkelsen på lagene som fyller hullene bestemmer således deres minste diameter, og selv om vi her har vist det som "stort", er tykkelsen på hvert indre lag bare noen få atomer tykk, og det er praktisk talt umulig å lage dem mindre. .

Av denne grunn må 3D NAND-minne forbli på 40 nm i overskuelig fremtid, og det er derfor alle anstrengelser fra produsenter i nyere tid er å øke antall lag som passerer gjennom disse kommunikasjonshullene, logikken i matrisen og forbedrede trappoppsett, men ikke for å redusere litografi fordi det på dette tidspunktet er nesten fysisk umulig.