この人生のすべては、特に新製品の開発を視野に入れて、方法論に従います。 これは、最短の正確な時間で明確な結果に到達することを目的とした一連のプロトコルで構成されています。 CPUの設計はこれに異質ではないため、設計時に実行されるさまざまな段階について説明します。 CPU.

数年前のCPUを使用して、一見同じように見える新しいCPUを購入した場合、同じように見えますが、そうではありません。新しい設計が複雑になると、作業時間が大幅に長くなり、より多くの作業が必要になります。資格のあるスタッフ。 量。 確かに、新しい製造ノードごとに多くのトランジスタを配置できますが、これには多くの作業が必要であり、開発時間が許されないことを考えると、新しい設計の設計は一連の整然とした段階に従う必要があります。

それはすべて、製造ノードを選択することから始まります

最初の段階はエンジニアによって行われるのではなく、マネージャーによって実行されます。マネージャーは、さまざまなファウンドリと数百万ドルの契約を交渉し、生産レベルとコストに関してさまざまな予測を行います。

製造ノードの仕様とコストは、アーキテクトがチップを作成するために必要な領域、トランジスタ数の予算、および新しいCPU設計を作成するために必要な開発時間を決定します。

アウトラインの実現は以下のとおりです

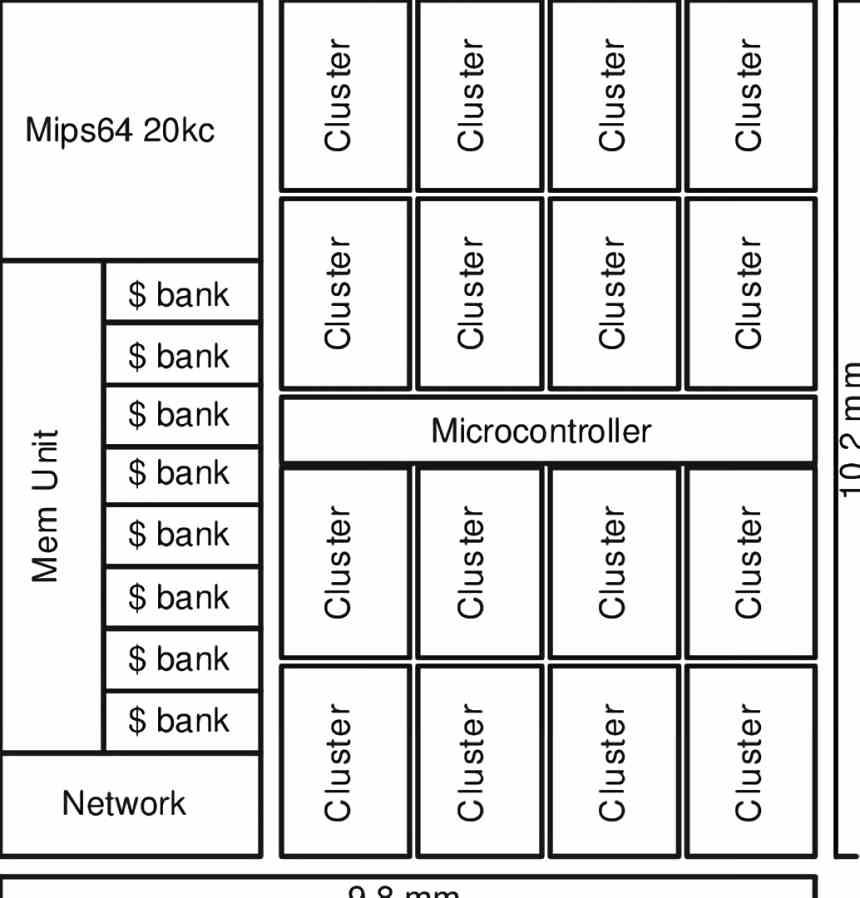

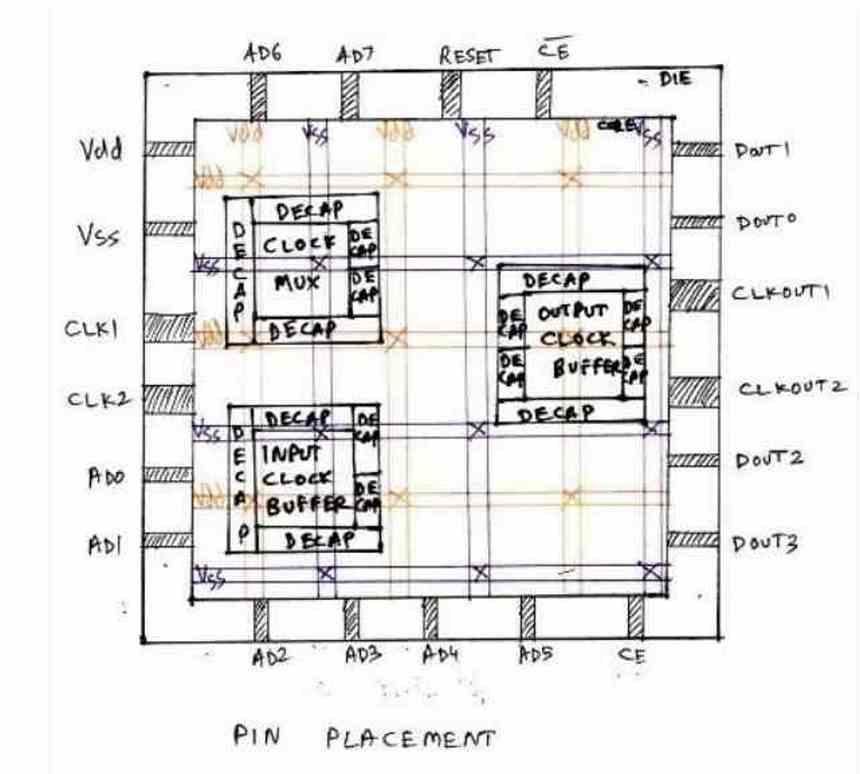

フロアプランは、CPUを構成する一般的な基本要素を示してスペース内でそれらを注文するスキームにすぎません。 一般的な要素については、ここにCPUコア、ここにキャッシュ、 GPU そこなど

ただし、これにより、マルチプレクサなどの組み合わせ回路、さまざまなタイプの論理ゲート、ALU、メモリバッファなど、はるかに基本的な要素を参照します。これは、ハードウェア記述言語では、さまざまな言語間の相互接続が必要であるためです。要素を指定するため、スキーム内のさまざまな要素を相互接続するために、鉛筆と紙、つまり巨大な紙を用意することが不可欠です。

作成される最初の図は最終的な図ではありませんが、CPUのさまざまなモジュールをXNUMXつのタイプのブロックに編成するために使用されます。

- 前者は固定ブロックと呼ばれ、その性質上許容されるため、設計上の変更がなく、面積に関して静的なままである要素が含まれています。

- 一方、用途の広いブロックは、特にチップの他の部分との相互作用がそれを必要とするため、または単に最終バージョンでどの設計が実装されるかをまだ知らないために、変更される部分です。

プロセッサのフロアプラン設計にいくつかの要素を改善するのに十分なスペースがある場合、並行して開発中であり、次のセクションで説明するこれらのパーツのより高度なソリューションを統合しようとします。

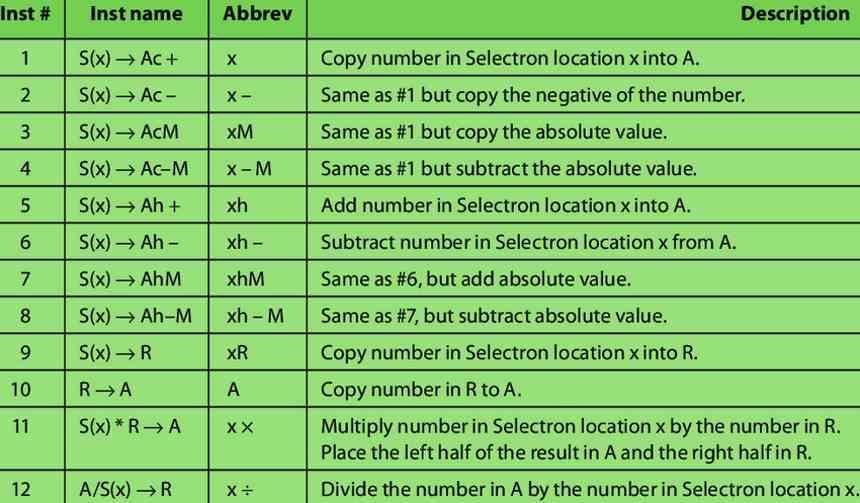

CPUの設計段階の3番目:ISAの定義

次の段階は、使用するレジスタと命令のセットの定義です。これらが世代から世代へと継承されるCPUの場合、実装は簡単に思えるかもしれませんが、新しい命令とレジスタを追加すると、再編成が行われます。それ自体で十分に複雑なものの。

GPUではそれは異なり、プログラムを実行せず、新しい世代ごとに、シェーダーユニットのISAの性質をより用途の広い方法で変更できることを意味します。 したがって、命令を削除する必要がある場合は実行できますが、CPUでは実行できません。命令またはレジスタを削除すると、ソフトウェアとの互換性が失われます。

あらゆるタイプのプロセッサの設計で通常は可変サイズであり、最終的にこの設計段階を通過するのは、データの処理を担当する部分です。 対照的に、固定機能要素はこれらの変更を受け取りません。

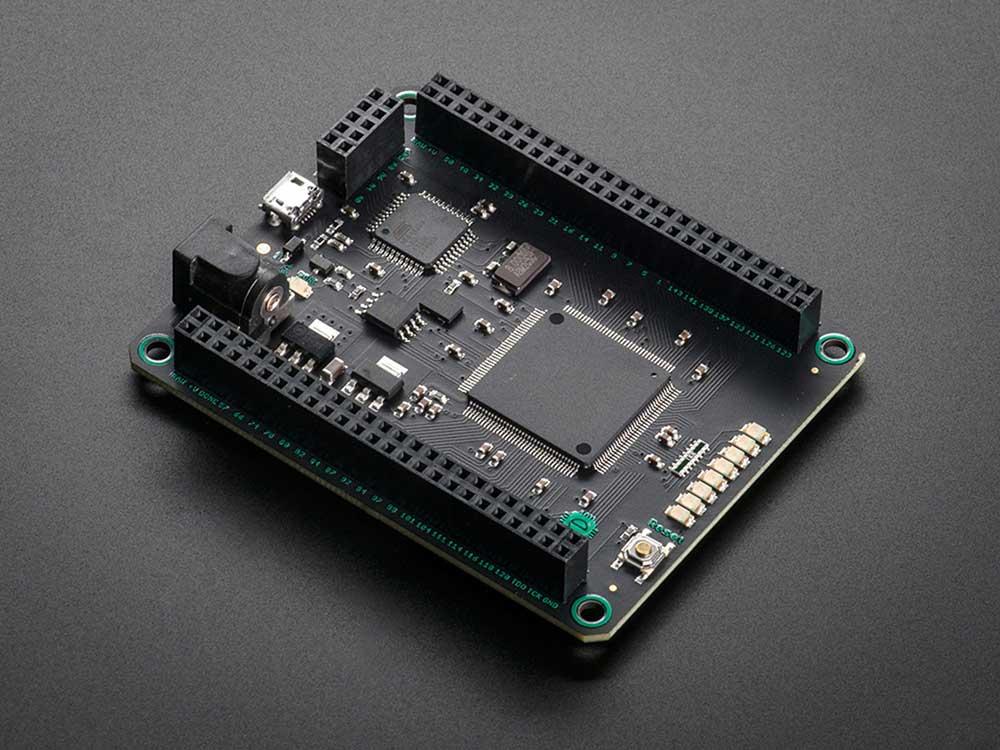

CPUの設計段階の4番目:FPGAでのテスト

いいえ、最終段階には達していませんが、デザインが機能していることを証明する必要があります。この目的のために、FPGAボードは通常巨大なマトリックスで相互に接続されています。 各FPGAは、設計しているCPUまたはGPUの全体的な設計の要素として動作するようにプログラムまたは構成されています。

ここでの考え方は、フルスピードを得るのではなく、スローモーションでデザインが機能していることを確認することです。 したがって、最終的なプロセッサよりもはるかに高いレイテンシとはるかに遅い速度が得られますが、私たちが関心を持っているのは、すべての要素が機能することです。

CPUの設計段階の5番目:I / O、電力、およびクロック

すでにチップの作成で構成されている第XNUMX段階は、最終的なチップを作成することですが、入力の問題は、一方では回路内のエネルギー分布を設計し、他方ではクロック信号のエネルギー分布を設計する必要があることに気付きます。 、そのうちのいくつかは細分化されるマスタークロックから派生し、他は独自のクロックを持ちます。

前のセクションで見た平面図を取り、四分円に分割された正方形または長方形で囲みます。 象限の外側では、特定のエネルギーまたはI / O関数が割り当てられています。 ここでチップの周囲が設計され、周辺機器やメモリとのさまざまな通信インターフェイスの配置がマークされます。

さまざまな要素の設計が達成されると期待されたクロック速度に到達できるかどうか、電気エネルギーの分布に関するすべての文書もチェックされるのはこの段階です。

プロセッサーの検証

設計後、同じものの検証が行われます。 完成した設計は、物理的なレベルで設計上の欠陥を探すまったく異なるチームによって検証されます。 検証チームの知識は、設計の知識とはまったく異なります。

この理由は、それらが非常に異なるブランチに接触し、検証チームがCPUの物理的な実装で発生するエラーの検出と修正に重点を置いており、そのアーキテクチャでは発生しないためです。 建設の世界に相当するのは、家や建物のプロトタイプを作成し、最終設計のパフォーマンスに影響を与え、シミュレーションには表示されないエラーを検出する労働者と請負業者のグループの世界です。