今後数年間で、アジア最大のファウンドリのN5ノードは、今後数年間で製造ノードの中で最も重要になるでしょう。 さて、上記の製造プロセスですでに製造されたチップのXNUMXつを分析したところ、次のことが発見されました。 TSMCの5nmノードの密度が予想よりも低い 。 これは悪いニュースですか、それともあなたの側の誠実さの欠如ですか?

TSMCの5nmノードとそのバリアントは、PC内で今後数年間で最も関連性の高いものになるでしょう。 それだけでなく AMD Ryzen 7000、EPYC Genoa、RX7000GPUなどの将来のチップに使用します。 また、TSMCがクライアントであり、 インテル、MeteorLakeと一部のPonteVecchio HPCグラフィックコンポーネントの統合グラフィックは、製造に使用されるためです。 したがって、何らかの形で、業界の主要なプレーヤーは、何らかの方法でこの製造ノードを利用します。 現時点では、この製造プロセスを使用しているチップは Apple

TSMCの5nmノード密度は宣伝されているよりも低い

この見出しは否定的に見えるかもしれませんが、これには説明があり、Angstronomicsから、TSMCが5nmノードの密度を間違っている理由を教えてくれる興味深い記事を作成したということです。 これは、面積あたりのトランジスタ数、つまりチップをどれだけ複雑に構築できるかを意味します。 台湾の鋳造所は、171平方ミリメートルあたりXNUMX億XNUMX万個のトランジスタであると公式に述べています 。 ただし、徹底的な分析により、この数値は低く、 137.6平方ミリメートルあたりXNUMX万トランジスタ .

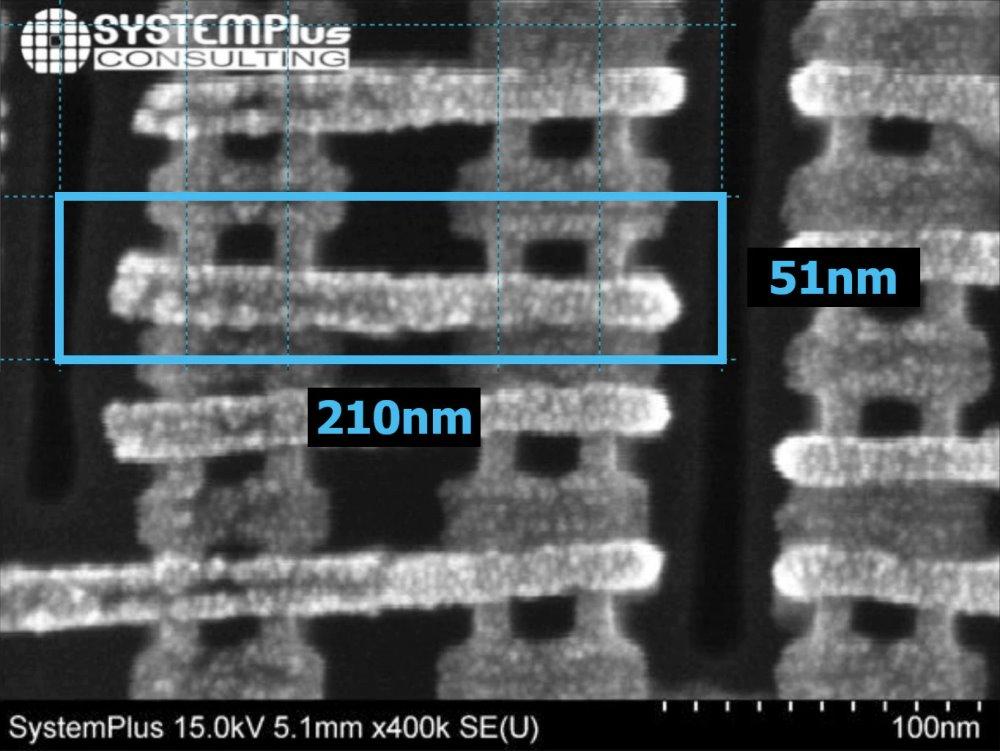

彼らは、最新世代のAppleA15プロセッサを構築するために使用されたトランジスタのサイズを電子顕微鏡で測定することによってこれを行いました iPhone. セルの高さで210nm、CPPで51nmの測定値 。 さて、両方の値は、前のノードに対するトランジスタのサイズを知るために比較方法で使用されます。 したがって、TSMCのN7ノードの値は次のようになります。 それぞれ240nmと57nm 、それに密度を与える 90.64平方ミリメートルあたりXNUMX万トランジスタ 。 最近Intel10と名付けられたIntelの7mmノードの場合、私たちは 100.33.

数字で目がくらむ場合でも、心配しないでください。 これは、同じスペースでチップ設計者が 51.8nmで構築されたチップの論理ゲートは5nmのチップより7%多い 。 これは、完全なノードジャンプではないことを意味します。 実際、トランジスタは5nmでもありません。 この測定基準はずっと前に現実に対応することをやめたので、それはより多くのマーケティングツールです。

TSMCは誤った数字を出しましたか?

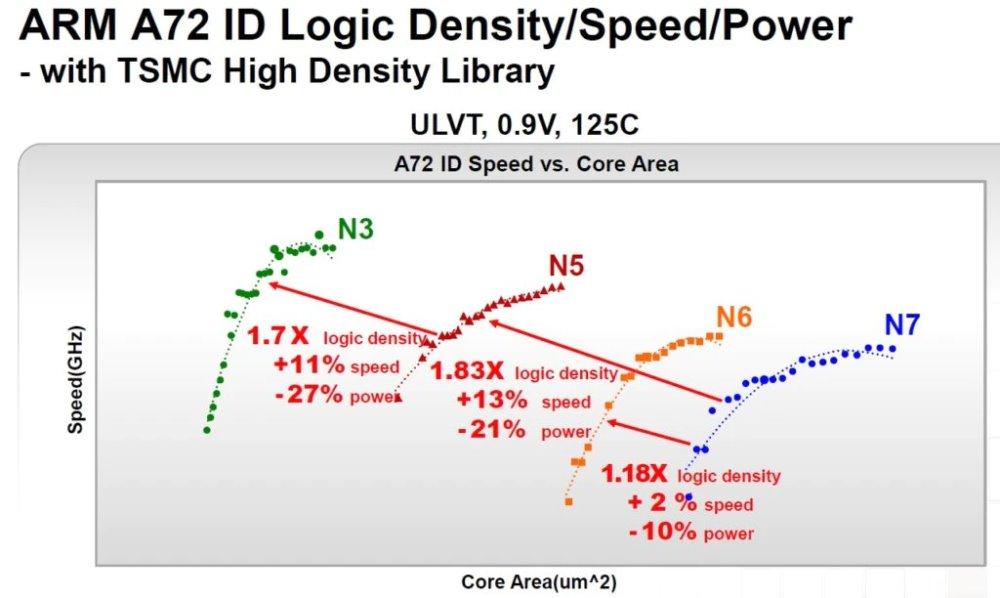

いいえ、そうではありません。これは、台湾のファウンドリが前のセクションで説明したメトリックを使用していないためです。 TSMCが通常行うことは、既知のチップを新しいノードに適合させて、そのメトリックを取得することです。 このために、彼らはもちろん、Cortex A72の設計を利用しています。これはファブレス設計であるため、異なるロジックの構築にXNUMXつのタイプのトランジスタまたは別のタイプのトランジスタを使用する場合、ファウンドリは世界中ですべての自由を持っています。チップを構成するゲート。

したがって、これらの線の上の画像でわかるように、 TSMCがどこから数字を取得するかを推測できます 。 そしてそれは論理の密度だけを参照しているということです。 そのため、たとえば、SRAMまたはチップのアナログ部分は除外されます。 ちなみに、現在のノードから将来のノードにジャンプしても、消費量が大幅に節約されたり、速度が大幅に向上したりすることはありません。 これは、次世代グラフィックスカードのハイエンドモデルの消費量の増加を部分的に説明しています。 NVIDIA とAMD。

いずれにせよ、これはファウンドリのパートナーやファウンドリで製造される将来のチップには影響しません。 それらの多くはすでに完成しており、大規模にウェーハに印刷されようとしています。