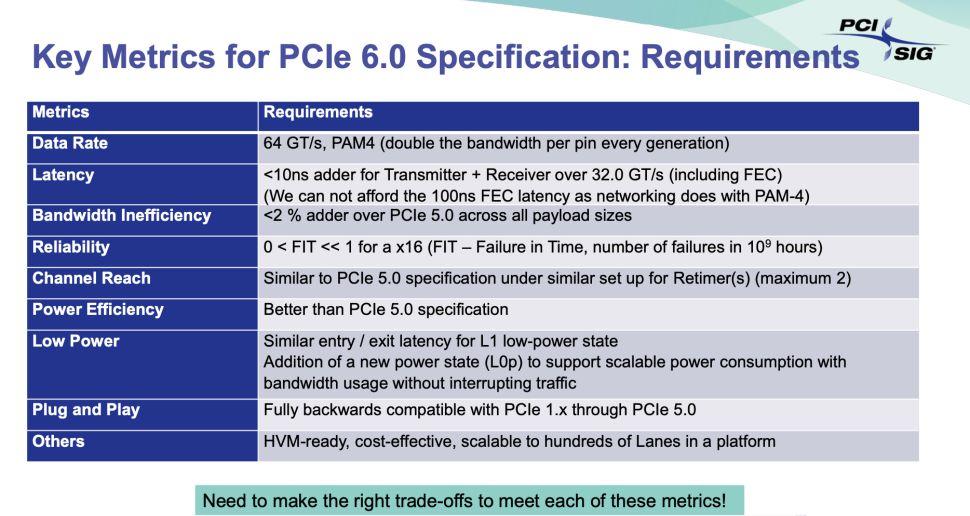

当学校区の PCIe 6.0 仕様は最初のドラフトですでに私たちの中にあり、そのため、この新しいバージョンのバスに関する記事ですでに取り上げた、かなりの数の新機能があります。 ただし、他の機能とは異なり、マザーボードの将来とバージョン5.0からこの新しい6.0への移行を示す機能が含まれている必要があります。後者は互換性がありますが、最初の機能は互換性がないためです。と呼ばれる機能のために 前方誤り訂正またはFEC .

なぜこの新しい標準を開発するのがそれほど難しいのですか? バージョン5.0以降、一般的に時間がかかり、時間がかからないのはなぜですか。 現在PCIe4.0を使用しており、同じ幅のx16ラインで速度を4倍にすることについて話しているので、改善は広範囲に及んでいます。 論理的には、PCI-SIGは、PAM XNUMXやFECなど、データ配信を保証する一連の改善を実装する必要がありましたが、後者は何であり、この特定のバスでどのように機能しますか?

PCIe 6.0に必要なテクノロジーである前方誤り訂正またはFEC

私たちが言うように、すでにPAM 4について話しましたが、FECはそれなしでは理解できません。 PAM 4は、数年前からネットワークエンジニアの一人であり、大規模なデータセンターでは、インフラストラクチャの保存や更新などのテクノロジーが聖杯でした。

しかし、それは波の変調の明らかな理由のために、そしてもちろん、利用可能な各Hzに対してより広い帯域幅を達成するためにPCIeバスに導入されているので、それだけではありません。 PCI-SIGには、その利点はあるものの、信号がより脆弱であるなどの欠点を軽減する必要があり、その実装の本当の理由として、いわゆる 前方誤り訂正またはFEC .

その名前が示すように、FECは、異なるリンクまたはホスト間の信号の送受信におけるエラーを訂正する手段にすぎません。FECは、エラー訂正を含むデータの一定のフローを提供することに成功しています。

これにより、データの整合性の観点から重要な信号から、エラーのない安定した信号になり、機器とそのコンポーネントの正しい動作が保証されます。

このテクノロジーの問題は、レイテンシーが高いことです。

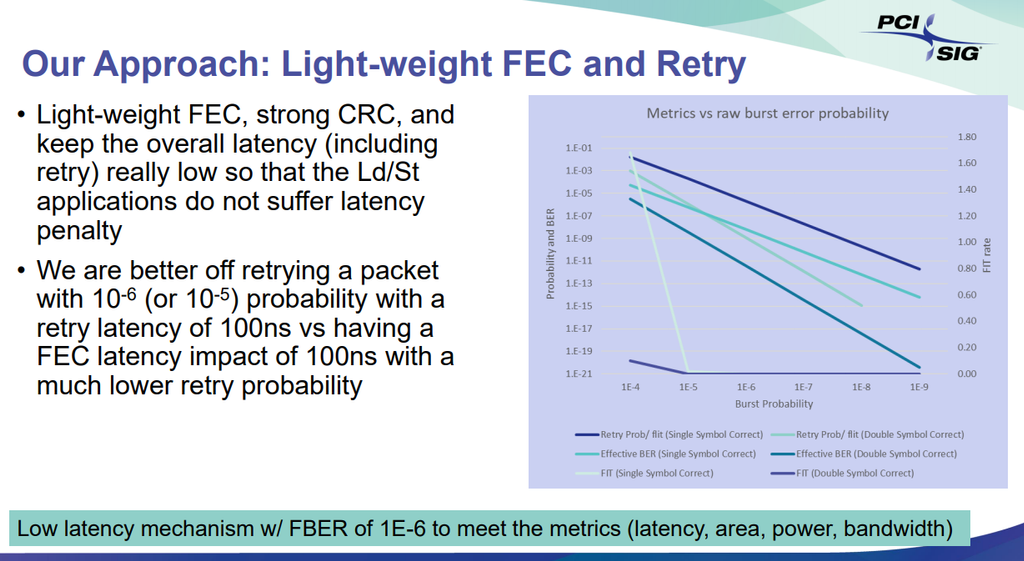

しかし、輝くものすべてが金であるわけではありません。 FEC自体、および最も純粋なCRCスタイルで見つかったエラーを修正するという性質上、PCIeのようなバスには適しておらず、バージョン6.0の128 Gb / s以下ではまったく適していません。

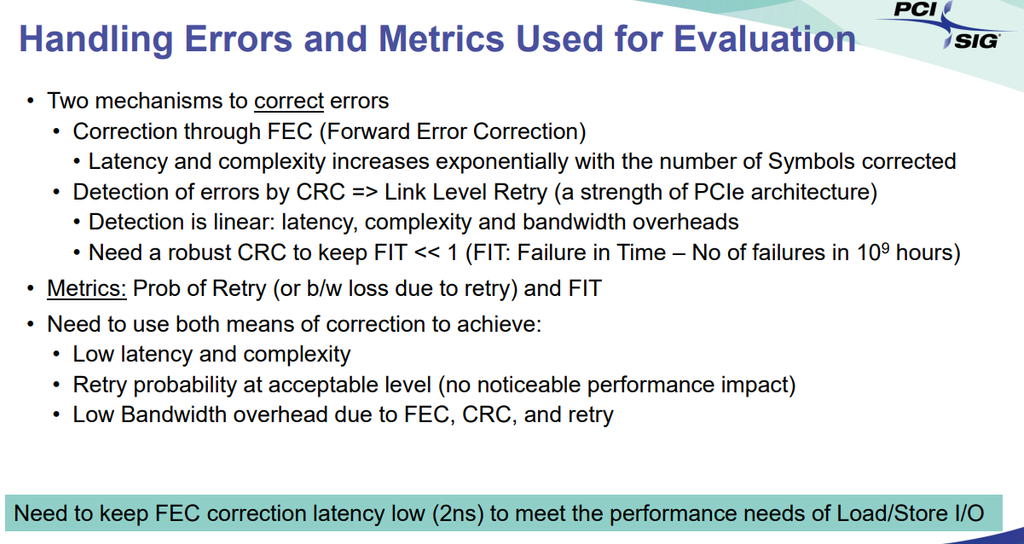

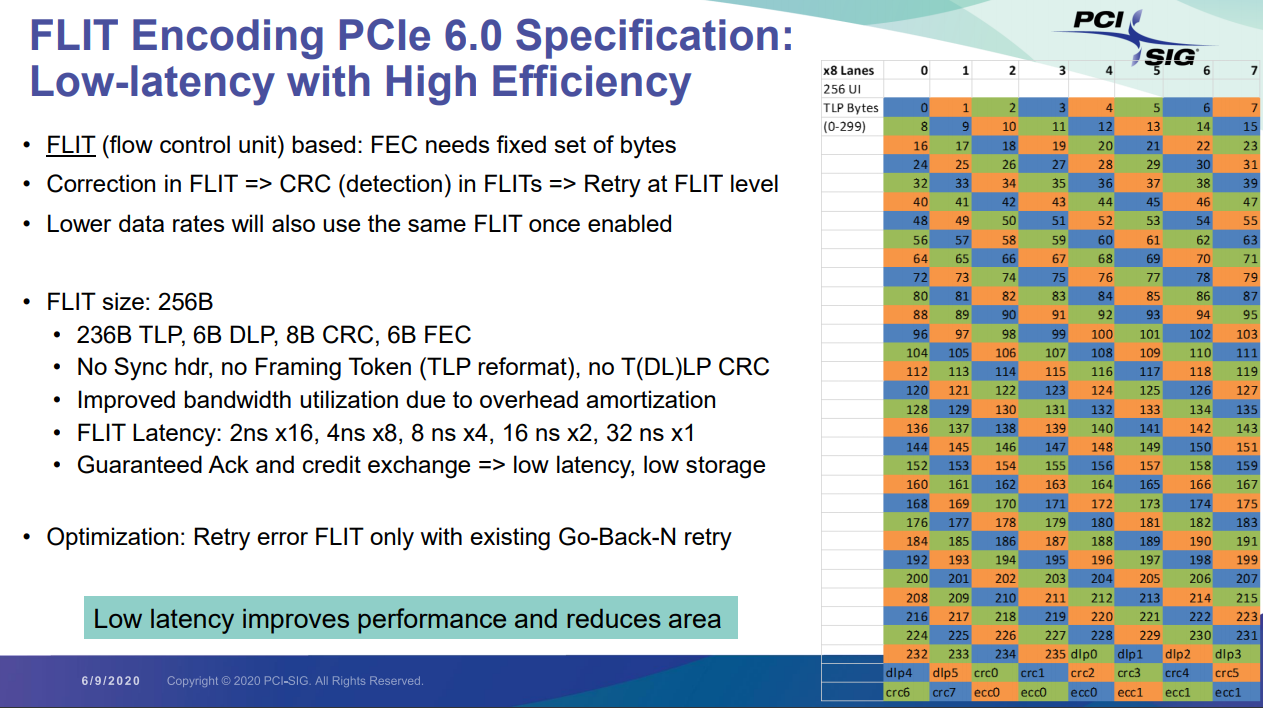

FECの問題は、バスに遅延が発生するため、パケット配信速度が低下し、不要な遅延が発生する可能性があることです。 そのため、PCIe 6.0テクノロジーは、独自の方法を使用して、最初のビットエラーレート(10でのFBER)の組み合わせにより低遅延を実現します。 -6) 軽量で低遅延のFECと組み合わせて、初期修正を完了します。

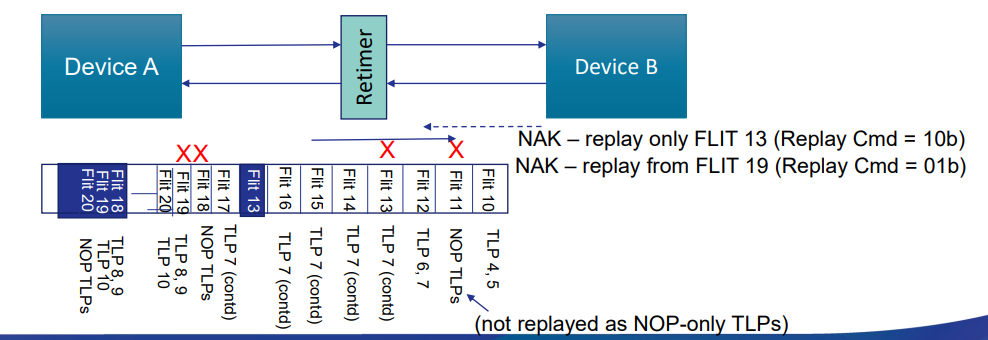

しかし、はい、FECはエラーを修正できますが、このためには、対応する選択を行うためにエラーの正確な場所と大きさを知っている必要があります。 どうして? 非常に簡単な目標は、ほぼゼロの遅延ペナルティを支払い(ゼロは不可能)、FECが修正できなかったエラーを処理するための高速リンクレベル再生と組み合わせた検出のための非常に堅牢なCRCに依存することでした(絶対的ではないため、CRCが必要です)。

一方、速度が 128 Gb /秒 PCIe 6.0では、FECをバイパスできる可能性があります。これにより、システムの遅延が少なくなります。

FECがエラーを修正できない場合はどうなりますか? さて、CRCがNAKの生成に入る時間ですが、最大100nsのデータをチェックするためのラウンドトリップの遅延がトリガーされます。

FECの使用が正当化されることは明らかであり、完全ではありませんが、エラー訂正を使用して可能な限り最小のレイテンシーを生成するための最良の方法です。 CPU、メモリと GPU.