One of the challenges that current technology faces is miniaturization , which consists of reducing the size of the transistors that are integrated in the chips such as PC processors to be able to incorporate a greater number of them in the same space, increasing thus notably the efficiency (yield per watt of energy consumed). However, it has long been difficult to comply with the famous Moore’s Law, and reaching and exceeding the 1 nm barrier seems to be the biggest turning point in the industry. Will it be possible to do it?

Reducing the size of the transistors is essential, but current technology is already at its limit and seems an impossible barrier to overcome, so future processors would be condemned to increase in size physically speaking to be able to incorporate a greater number of transistors inside. Is this the end of Moore’s Law? Is it no longer possible to overcome this barrier? ASML and imec believe that it is possible, and in fact they are so confident that they have already incorporated it into their roadmap for the next few years.

How to pass the 1 nm barrier and comply with Moore’s Law

It was during the 2020 “Imec Technology Forum” (ITF) Japan that imec CEO and President Luc Van den Hove delivered a keynote address to provide an overview of the company’s research process, which together with ASML (known for making wafer machines) literally state that “Moore’s Law is not going to stop.”

Van den Hove said that thanks to the new, next-generation, high-resolution EUV manufacturing process called High NA EUV, Moore’s Law will continue to be enforced and the process will continue to be refined beyond 1 nm.

Many semiconductor companies, including several Japanese ones, withdrew from the “process miniaturization race” one after another, saying that “Moore’s Law is over” or that “it is so expensive that it is not profitable”, but imec states that they are going to stand firm from beginning to end so that technology continues to advance, and in fact as you see in the image above they proclaim the extension of the useful life of Moore’s Law, which has become a law of truth regarding the investigation of component miniaturization.

With regard to the EUV exposure technology, considered indispensable for the so-called “ultra miniaturization”, imec has partnered with ASML to develop a technology that allows going beyond 1 nm in terms of miniaturization (however, they have not said if it will be 0.5 nm, 0.9 nm, or what).

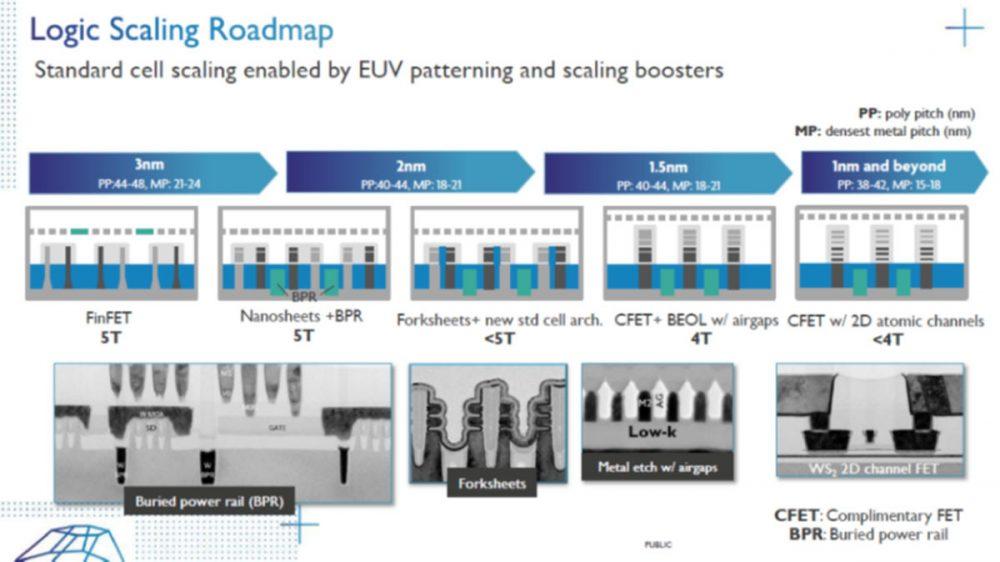

The roadmap of miniaturization processes

During the aforementioned conference imec provided its roadmap (future plans) regarding miniaturization, starting from the current FinFET process at 5 nm to beyond 1 nm (although yes, they have not indicated dates or even years in the expecting such technologies to be available).

If you look under the number of each of the nodes you will find a series of acronyms, and they all begin with PP, which is the step of the polysilicon wiring with its metrics (for example, at 3 nm it is 44-48) while MP is the thin metal wiring pitch (continuing with the 3nm example, it is 21-24). It should be noted that the technology node used to refer to the minimum machining dimensions and length of logic gates, but now it is a mere “label” that does not mean the actual physical length.

High NA EUV technology will allow a decrease of 1 nm

TSMC and Samsung Electronics have already introduced an EUV exposure device with NDA = 0.33 in some lithographic processes at 7 nm, and they already carry out tests with processes at 5 nm with this technology where they have increased in frequency. However, there they have stayed and have not given information beyond 2 nm for the moment. According to imec, it is necessary to perform high resolution and high NA (NA of 0.55 at least) on the exposure equipment to further reduce the size of the transistors.

ASML for its part has already completed the basic design of the NA EUV high exposure equipment such as the NXE: 5000 series, but they do not expect that they will be able to market it until at least 2022. This new generation machine has an additional disadvantage, and that is that it is much higher than the previous ones because it has a huge optical system, so it is possible that manufacturers have to adapt the height of the ceiling of their factories if they want to be able to put them inside.

In principle ASML has designed this machine in close collaboration with imec to go down 2nm, go down to 1nm and even exceed it, but regarding the development of the lithography process using High NA EUV equipment, Van den Hove said the following:

“The purpose of miniaturizing the logic device process is to reduce energy (consumption), improve performance, and reduce area in a process we commonly call PPAC. Cost reduction, sustainable, and with due consideration for the environment in addition to these four factors, when moving to miniaturization below 1 nm are our priorities, and it will take time to be able to carry it out successfully. “