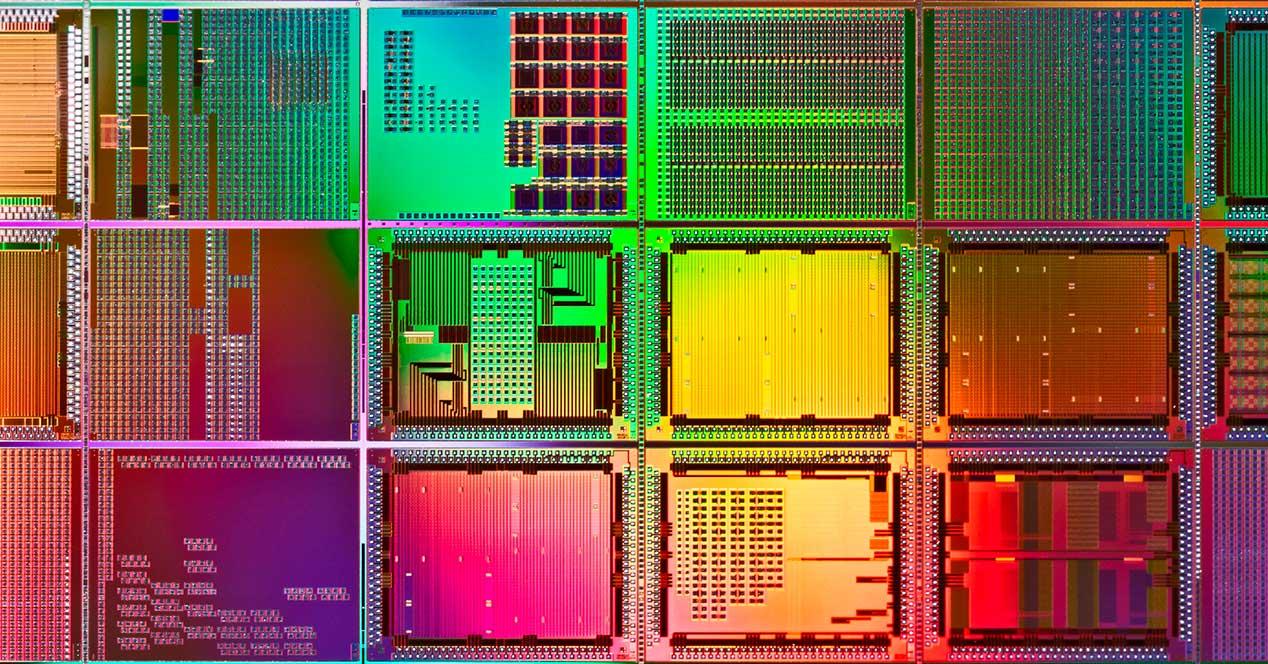

The market is targeting chiplets, or so it seems. AMD has been with its MCM-based arrangement for some years now and Intel is about to take the next step with technologies like Foveros, but is this a must-see move? We already know its advantages, and its disadvantages? Today we will see the good and bad of chiplets and why the industry does not see this way of creating CPUs so clearly.

All the major ones including AMD, Intel, TSMC and Marvell are working on different approaches to the world of chiplets, different alternatives trying to develop more advanced designs. Although in previous articles we dealt with this specific topic, there are certain points that we leave for this occasion, since the industry is not so sure that chiplets are the way to go.

Lack of ecosystem, standards, time and development costs

Not all that glitters is gold and although AMD is one of the few that are launching real products on the market based on chiplets, it is not exactly easy to do so. The problem is that there is no ecosystem, there are no fixed standards that the industry can follow in order to reduce creation times and development costs.

Each company is facing, more or less, their problems individually, unitary, but none of them separately has all the pieces to form the puzzle. Instead, and quite curiously, they all face almost the same problems:

- They try to offer optimal chiplets and with better and faster connections that can scale to different products.

- They need third-party technologies to a greater or lesser extent.

- Lack of support in the designs of the interconnection schemes between dies.

- They need correct IPs with manufacturing capabilities.

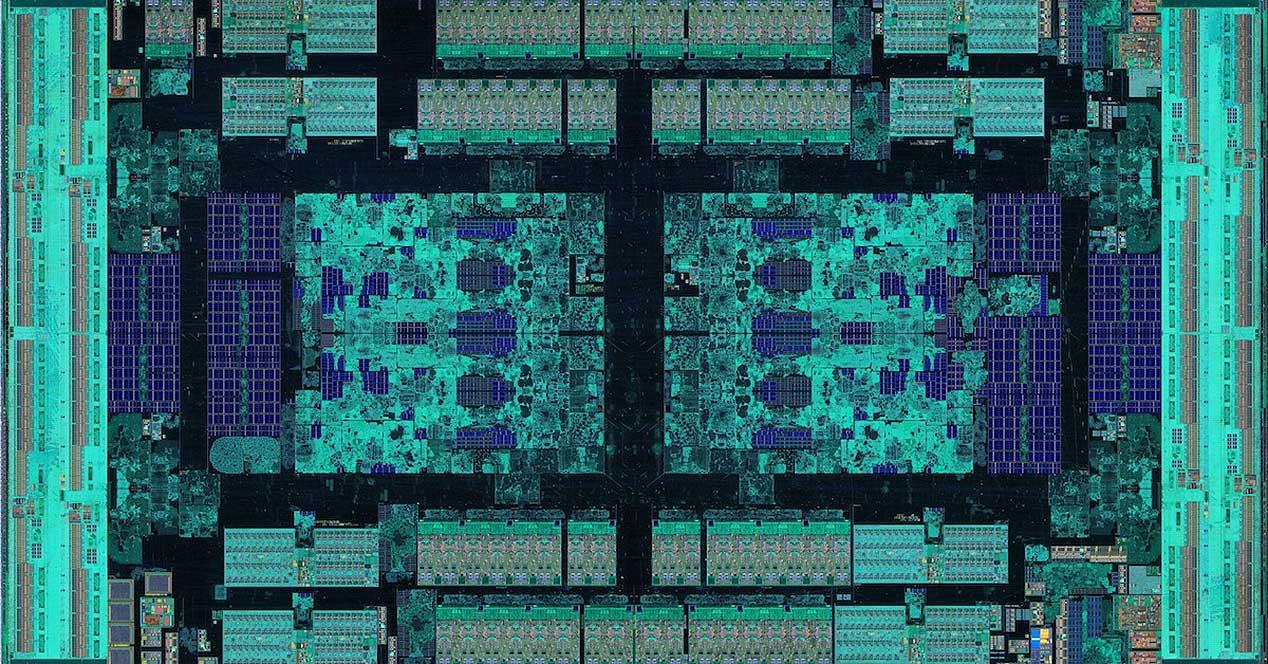

This is causing, for example, Intel to follow its path based on monodie for its CPUs, something that we will see for quite a few years. AMD has been a pioneer, but it is paying large costs because it depends on third parties and these, in turn, specialized companies for certain techniques that have to be developed exclusively, increasing overall costs.

EDA tools are needed to join all these pieces, since they are different architectures and products, physical and logical interfaces to join and classified information from various companies to launch a single product. Also, some key components may not be available as such, exacerbating the problem.

The industry has to share different IPs if it wants to move forward with chiplets

![]()

There is no more blind than he who does not want to see. A saying that seems to be disliking certain sectors of IP manufacturing for large companies. The investment is made and the way has to be to share at least a series of standard interfaces for chiplet integration, something that will seriously harm them economically.

The example to follow is simple, the NVMe, SATA SSDs or DRAM itself. They use the same interface, so that the different parts do not need to know the details of the others since they know what to adhere to and how the design of the PCBs, the connections and the chips must be.

They save costs, time, optimize financial balances, produce much more and better, but the most important thing is that all companies compete under the same conditions, promoting the sector’s own competitiveness.

In this regard, and how could it be otherwise in the face of such chaos, large companies are developing the basis of these much-needed standards, interconnection technologies with open interfaces for companies to join their cause.

So much so that currently the dispute will be between four contenders for the title: AIB, BoW, OpenHBI and XRS , where in addition, the ODSA is developing for its part the so-called Chiplet Design Exchange or CDX , an open format for the secure exchange of information maintain confidentiality and maintain workflows and information for prototypes.

With him in mind, we try to organize the different interfaces to start creating a heterogeneous confidential system that gradually designs chiplets more easily and based on the standard that ends up being imposed. It may be the case that there is not a single winner, since the industry needs to innovate in at least two ways, but at least it would be the first step to have a common goal for all.

The creation of the chips and their interconnections also requires unification of criteria

If the puzzle was already difficult to solve, keep in mind that the designs of the interconnections (aka protrusions or microbumps) are also not defined as standard. Each company creates its bumps and its packaging, so since there is no standardization in this, specific tools are required for the verification, creation and supervision of the wafers, both for the chips and for the interposers.

The steps are almost all automated, where the wafers pass several hours of testing, testing, and monitoring with electrical, physical, and visual content. As expected, interconnects using microbumps are much larger in physical size in chiplets than in monolithic die, where they can reach from 25 microns to 40 microns.

To get an idea, and taking a typical 300 mm wafer, checking each connection of microbumps is like locating the head of a pin on a soccer field, according to the vice president of FormFactor. The precision is incredible and this means that without a standard the costs will continue to grow for everyone, since the new microbumps approach 10 micrometers , and the tests will not stop rising in price due to the immense precision they need to its corresponding tests.

So and in summary, is it an advantage or a disadvantage to follow the path of chiplets? It is very good that we see the sea from the shore and we are impacted by each launch or technology designed by both Intel and AMD. But underwater the sector is not so clear and although the steps to follow are being defined, those of Swan for example will not leave monolithic CPUs aside until the entire industry can have a series of standards to follow.

AMD is going to have to bear the weight of everything said and in the hands of TSMC, where as we have already commented more than once, the prices of its processors will have to rise sooner or later to remain profitable and above all, increase the profit margin. It is not going to be a smooth journey for either of the two giants, Intel has EMIB, Foveros, AIB and Co-EMIB , TSMC in development with System on Integrated Chip (SoIC) and AMD tries to square the pieces for its new architectures based to various companies that supply what is necessary for these chiplets.

If anyone thought that this was sewing and singing, they were very wrong. The future is not black, but it requires long-term deals and losses that everyone will have to bear.