The semiconductor industry is currently operated exclusively by three companies: Intel, Samsung and TSMC. The fight is focused on the three of them and in the future there are no views of a new competitor, so whoever advances faster will take the cat to the water. What can we expect from this year? Who will dominate the market and will drag the largest number of manufacturers under their lap? Let’s review the organization chart and planning of the lithographic processes of the big three.

As we have already seen in other articles on this subject, the industry faces several challenges in the short and long term. The first of these is undoubtedly the nanometer drop to obtain higher density, higher frequencies and less or equal consumption, but after this there are others that are of equal or greater importance if possible.

Transistors transition, the first step to a new era

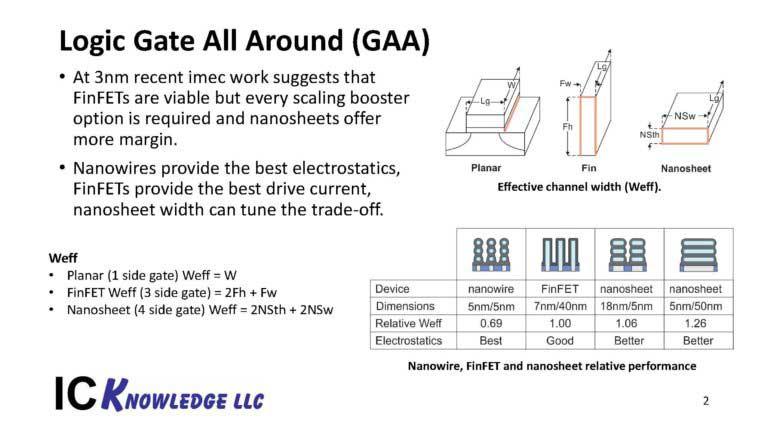

Something that we already talked about and that is key to understanding this article, so we will not go too far here. The FinFET era is coming to an end, mainly due to the way they are built with their three gates on three sides of the transistor. As much as they are 3D transistors, the reduction of nanometers and with it the space that can be between them forces the industry to abandon them in order to reach higher densities.

Its substitute already has a name and is in production: Gate All Around or GAA , also known as HNS for the implementation of the horizontal nanoblades that it integrates, the main novelty in this type of transistor.

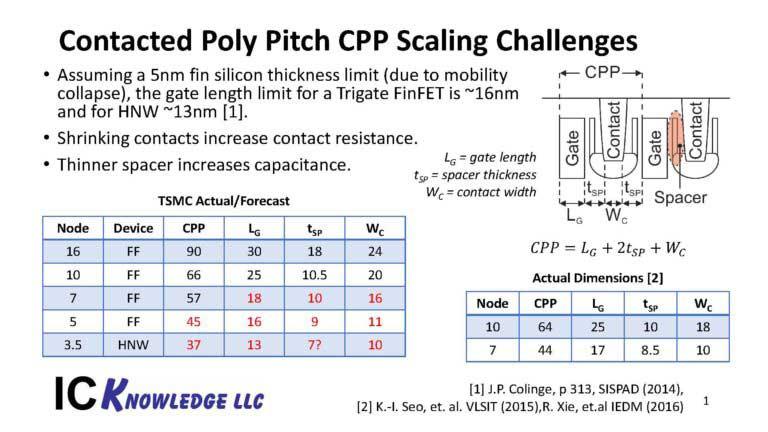

In this new version the nanolayers are very narrow, they improve the nanowires and the electrostatics, so the length of the gates is reduced from 16 nm in FinFET to 13 nm (or less) in GAA, which is directly dependent on the Contacted Poly Pitch (CPP) , that is, lower CPP is equal to higher density by pure logic.

In short, the problem here is that the three big companies are approaching this at different times: TSMC will not implement it until, at least, its 3 nm, Samsung will have it in production at 5 nm and Intel has not given information about it.

Reduction of the fins for each transistor to save space

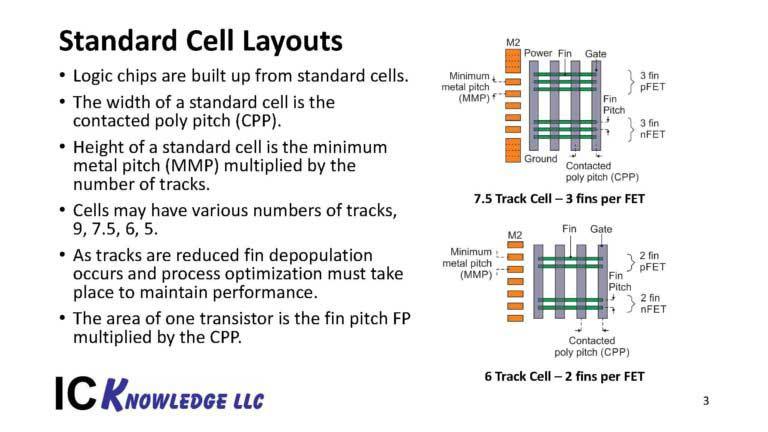

The stacking of the leaves and with it the gates will have another direct impact as the nanometers continue to be reduced, and is none other than the reduction of the fins or fins. This has direct implications for controlling the transmission current of a transistor, since engineers are left with less space and options to achieve constant currents and thereby minimize leakage.

All of this focuses on cells, which are a fundamental part of understanding how GAAs will work. These cells are based on tracks , which are reduced with each lithographic jump to improve density and with them the minimum metal pitch (MMP).

Smaller number of cells reduces both vertical and horizontal space, and because of this all the components they make up also have to be reduced, making it difficult to implement transistors.

Therefore, the next step to GAA (HNS) is the so-called CFET or Complementary FET . It is basically a step further in terms of density scalability as it features two vertically stacked FET types: nFET and pFET.

The difference with the Nanoblades in GAA is that they offer two different heights that as the cells are reduced, more CFETs can be added to compensate, where the Gates are now vertical and with this the Fin Pitch can be reduced more and more between each CFET .

Logically this has stability implications still to be studied, but they are already in process by the big three. We do not know what the implementation of each will ultimately be or how they plan to solve problems such as interconnections (exclusive article on this topic shortly), but the original improvements are of such caliber that we are sure that it is the way to go (from 1, 4X to 2X in the best designs).

Prospects for lithographic processes in 2020, 2021 and 2022

Although it seems that the industry has long-term future plans, the reality is that they are quite fair as far as time is concerned. For this reason and seeing all of the above and the articles that are to come, we have to think that the future is, today, three years at the most and with many questions that may influence some minor changes in the specifications that are have leaked.

What we are trying to say is that if this in itself almost runs over the industry in the post of the advance, we must understand that lithographic processes surely extend over time because the industry needs to work for a longer time to solve the following challenges to continue going down nanometers.

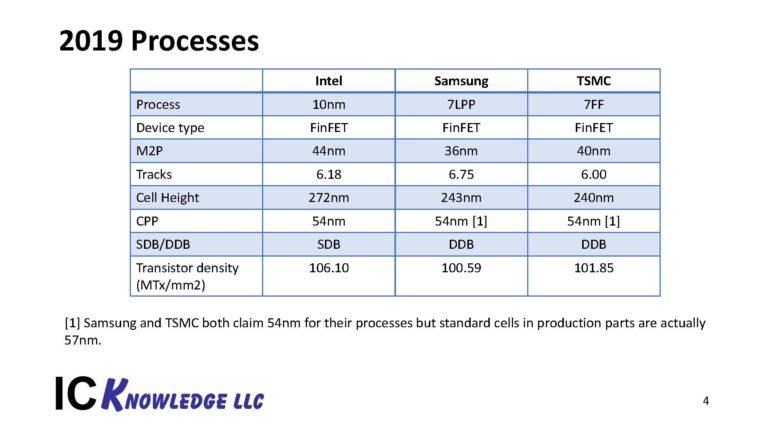

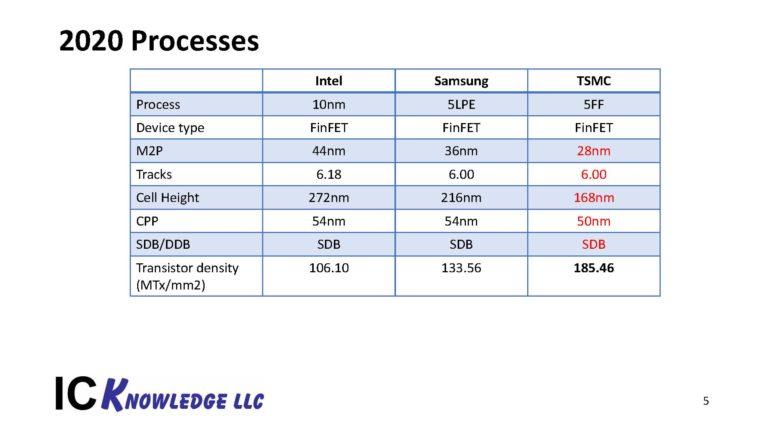

This trend will surely extend until 2030, where it is possible that we are skirting the atom and there we will face the following problem again. Meanwhile and looking back to have a clear starting point, in 2019 Intel released its 10nm, Samsung its 7nm LPP and TSMC its 7nm FF.

Here it must be clarified that although Intel had the lead with its lithographic process, this advantage was not real as such since the high-performance version was not available and therefore everything is a bit fictitious as such.

Although Intel with its 10 nm has greater density, this 2020 will not be the year in which it will debut as such, in any sector, since the company intends to make the jump to 10 nm ++ in 2021.

This year 2020 everything is going to change drastically and even if the 5nm TSMC are not imposed with a really incredible density of 185 million transistors per mm2, the reality is that they will not enter directly with high-performance products just as happened to Intel in 2019.

Samsung for its part will follow in the wake of TSMC with a less dense but surely more profitable process per wafer. Intel with no improvements on the horizon and with an eye on 2021.

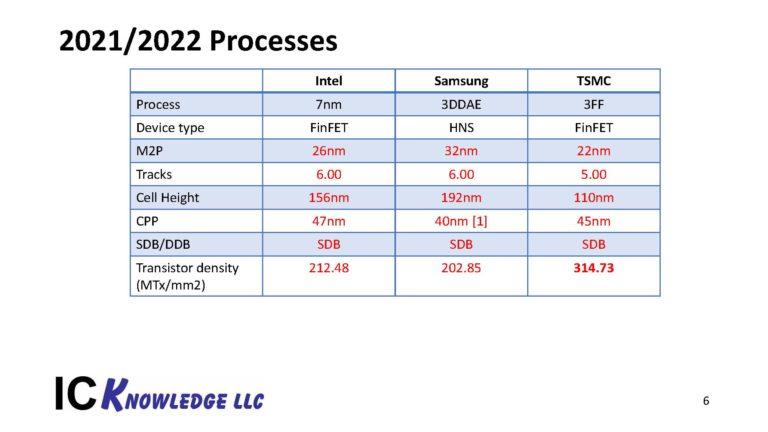

Being optimal at the time of speaking, it must be pointed out that although the companies affirm what is shown in the graph, the reality is that it will be really difficult to see products in said lithographic processes beyond that they are mass-produced. That is why 2022 is spoken of as a possible year of implementation.

Intel may have its 7nm ready by the end of 2021, but TSMC will almost certainly not have the 3FFs for that year, in any case looking to 2022, as they are facing problems they must solve first.

Instead, Samsung could have its 3nm HNS by the end of that year and with a view to final products in early 2022, where it could compete with Intel to a greater or lesser extent. In any case, this industry is very changing, where there are advances there may be delays, so we will be watching to see the changes in real time of the lithographic processes.