Một trong những điểm quan trọng nhất khi thiết kế một bộ xử lý mới, cho dù chức năng của nó là gì, là mức tiêu thụ năng lượng mà nó có và do đó nó được tổ chức như thế nào để tận dụng tối đa năng lượng cung cấp cho nó. Đây là nơi được gọi là Cung cấp điện mạng hoặc PDN xuất hiện. Nó là gì và tại sao nó lại quan trọng trong việc thiết kế một bộ xử lý mới?

Có một huyền thoại ăn sâu vào tâm trí của nhiều người rằng mức tiêu thụ điện năng của bộ vi xử lý là thứ mà các nhà sản xuất đột nhiên phát hiện ra khi nó chuyển từ giai đoạn thiết kế sang giai đoạn tiền sản xuất. Thực tế là hoàn toàn khác, xét cho cùng, một bộ xử lý không hơn gì một mạch điện ở quy mô rất, rất nhỏ. Vì vậy, chúng ta đang nói về cách các electron di chuyển qua mạch là rất quan trọng và là một phần của thiết kế bộ xử lý ban đầu ngay từ đầu.

Mức tiêu thụ điện năng của bất kỳ bộ xử lý nào được đo như thế nào?

Chúng ta không thể biết mức tiêu thụ năng lượng chính xác của một bộ xử lý là bao nhiêu, vì một loạt các hiện tượng vật lý có thể xảy ra làm thay đổi kết quả và chỉ được biết đến khi thiết kế đã được sản xuất và do đó nó đi từ khái niệm đến thực tế. Vì vậy, một phép tính gần đúng đã được thực hiện, giúp các kỹ sư có được ý tưởng gần đúng về mức tiêu thụ năng lượng.

Công thức chung như sau:

Công suất (watt) = số cổng logic * điện dung * tần số đồng hồ * bình phương điện áp.

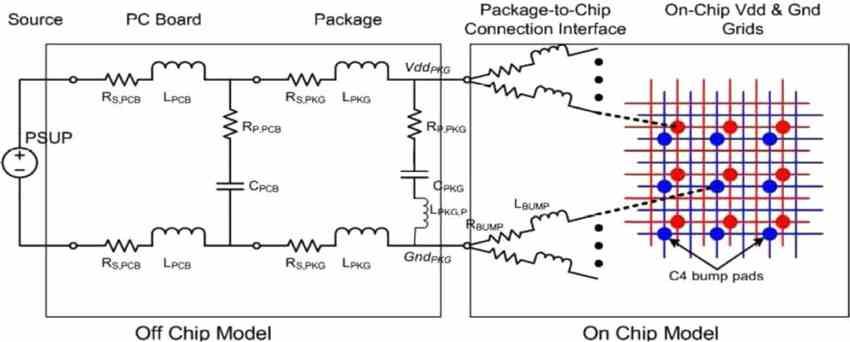

Nhưng điều này là một ước tính rất chung chung , trong cùng một bộ xử lý, các nhà thiết kế có thể sử dụng các loại cổng logic khác nhau ngay cả trong cùng một loại và với các mức tiêu thụ khác nhau. Nhưng đặc biệt là nó phụ thuộc vào cách mà các cổng logic khác nhau tạo nên các phần tử khác nhau của bộ xử lý được kết nối với nhau. Đây là nơi chúng tôi nhập Mạng phân phối điện hoặc PDN. Đó là một phần của thiết kế của mỗi bộ xử lý và đề cập đến cách phân phối điện năng giữa các cổng logic khác nhau.

Mạng lưới cung cấp điện là gì?

Trong quá trình thiết kế một bộ xử lý, cần đạt đến điểm cần tổ chức các khối khác nhau tạo nên nó và kết nối chúng với nhau để giao tiếp. Nhưng mỗi phần tử yêu cầu một dòng điện để hoạt động. Đối với những gì xảy ra khi một tòa nhà được xây dựng trong đó việc phân phối mạng điện phải được thiết kế, điều tương tự cũng xảy ra khi một bộ xử lý được thiết kế.

Trong một CPU, những gì tiêu thụ nhiều nhất là các kết nối, ngày nay giữa kết nối bên trong và bên ngoài trong nội thất, 3/4 mức tiêu thụ nội bộ của cùng một loại bỏ đi và đó là một trong những thách thức lớn nhất đối với các kỹ sư ngày nay. Điều gì khiến nó trở thành một thách thức khi tạo ra các bộ vi xử lý mới với ngày càng nhiều lõi, không chỉ giao diện giao tiếp mà còn khi cung cấp các khối khác nhau của bộ xử lý.

Không thành vấn đề nếu chúng ta đang đứng trước bộ xử lý 1 W của điện thoại thông minh, 45 W của máy tính xách tay chơi game cao cấp hay 200 W của bộ xử lý máy chủ. Tất cả chúng đã được thiết kế với một Mạng lưới cung cấp điện cụ thể. Điều này ngụ ý rằng mỗi cái trong số hàng trăm triệu, nhưng hàng tỷ, phải hoạt động ở điện áp thích hợp. Ví dụ, nếu điện áp quá thấp, dữ liệu có thể thay đổi và bộ xử lý không chỉ hoạt động với dữ liệu không chính xác mà còn có thể ảnh hưởng đến sự ổn định của bộ xử lý.

Những thách thức hiện tại khi thiết kế PDN là gì?

Khi thời gian trôi qua, điện áp mà cả bộ xử lý và bộ nhớ hoạt động đã giảm xuống. Ban đầu, các thiết kế của một máy tính hoàn chỉnh được thực hiện bằng cách sử dụng một số chip được kết nối với nhau theo giao diện TTL, logic transistor-to-transistor, với điện áp 5 V. Hiện tại với việc sử dụng các bóng bán dẫn FinFet ở bước sóng 7 nm, chúng ta di chuyển xung quanh 0.5 V và 1 V. Điều này dẫn đến một thách thức cho các nhà thiết kế hệ thống.

Trong bộ xử lý kỹ thuật số, tín hiệu được xử lý theo cách nhị phân và do đó điện áp dao động giữa hai giá trị điện áp, một giá trị đang hoạt động và một khi bộ xử lý tắt. Nhờ đó, các giá trị được tách biệt đủ để các thăng trầm giống nhau không kết thúc gây ra sự nhầm lẫn tín hiệu được gửi đi. Tuy nhiên, với điện áp ngày càng thấp thì đây là một vấn đề và đó là để cung cấp đủ năng lượng cho các bộ vi xử lý mạnh nhất thì chúng ta phải tăng số lượng ampe cung cấp cho nó. Vì mức tiêu thụ của bất kỳ mạch điện tử nào cũng tỷ lệ với bình phương điện áp của nó, nên hầu hết các nhà thiết kế đã cố gắng giữ cho nó càng thấp càng tốt trong thông số kỹ thuật.

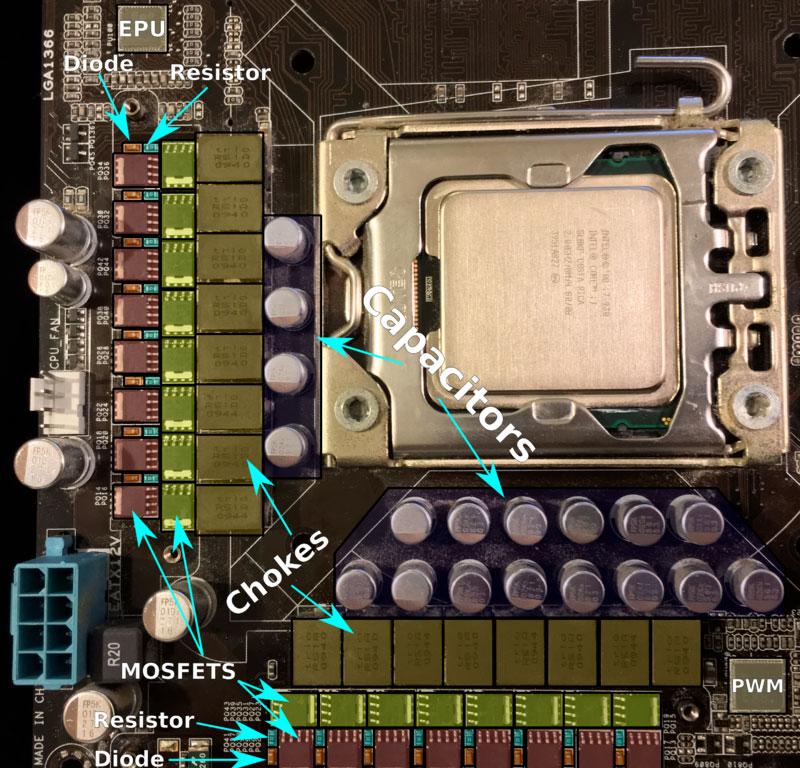

Mô hình điện áp thấp, cường độ dòng điện cao là một thách thức vì cần nhiều cáp hơn để mang lượng dòng điện lớn hơn cần thiết. Làm cho Mạng phân phối điện phức tạp hơn mức bình thường, không chỉ trong bản thân bộ xử lý mà còn cả bên ngoài. Nơi tổ chức VRM trên bo mạch chủ hoặc thẻ mở rộng là quan trọng trong hệ thống điện phức tạp.

Mạng lưới cung cấp điện ngày nay và trong tương lai

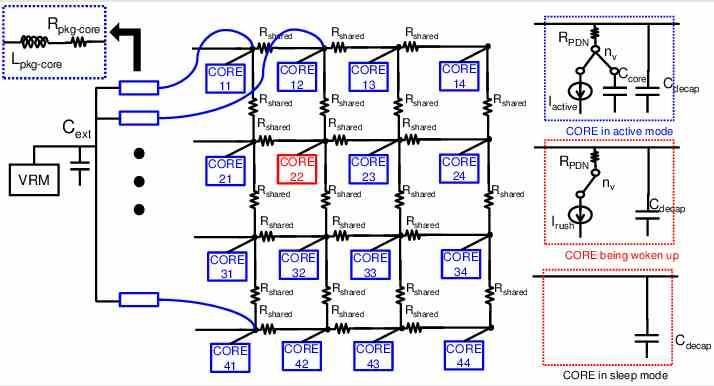

Trong những năm gần đây đã có những biện pháp nhằm tiết kiệm năng lượng và tăng hiệu suất trong các bộ vi xử lý. Chúng bao gồm việc sử dụng Mạng phân phối điện được xây dựng theo cách mô-đun. Được thiết kế để các bộ phận của bộ xử lý tắt hoàn toàn khi chúng không được sử dụng để sử dụng ít năng lượng hơn. Chúng ta cũng không thể quên các cơ chế cho phép điện áp của một bộ xử lý thay đổi một cách linh hoạt để thay đổi tốc độ xung nhịp và mức tiêu thụ năng lượng.

Một bộ xử lý hoạt động ở tốc độ 1 GHz với điện áp 1.2 V sẽ hoạt động tương tự như bộ xử lý 0.6 V ở cùng tốc độ xung nhịp, nhưng nó sẽ tiêu thụ nhiều hơn 4 lần cho cùng một công việc. Đó là lý do tại sao nhiều CPU và GPU hiện đại có Mạng phân phối nguồn được thiết kế để giảm điện áp xuống mức tối thiểu cần thiết khi tốc độ xung nhịp thấp. Điều này làm tăng mức độ phức tạp của bộ xử lý, vì cần phải thiết kế bộ xử lý để nó có thể hoạt động với các điện áp khác nhau trong thiết kế của nó.

Các bộ xử lý ngày nay được tạo thành từ hàng tỷ bóng bán dẫn tạo thành hàng trăm triệu cổng logic và cùng với chúng là hàng chục triệu hệ thống tổ hợp và tuần tự. Do đó, thiết kế của PDN trở nên cực kỳ phức tạp hơn theo thời gian và nếu chúng tôi thêm những gì chúng tôi đã đề cập vài dòng trước, do đó nó sẽ trở thành một trong những phần quan trọng nhất trong thiết kế của bất kỳ bộ xử lý nào.

Mọi thứ trở nên phức tạp với chiplets

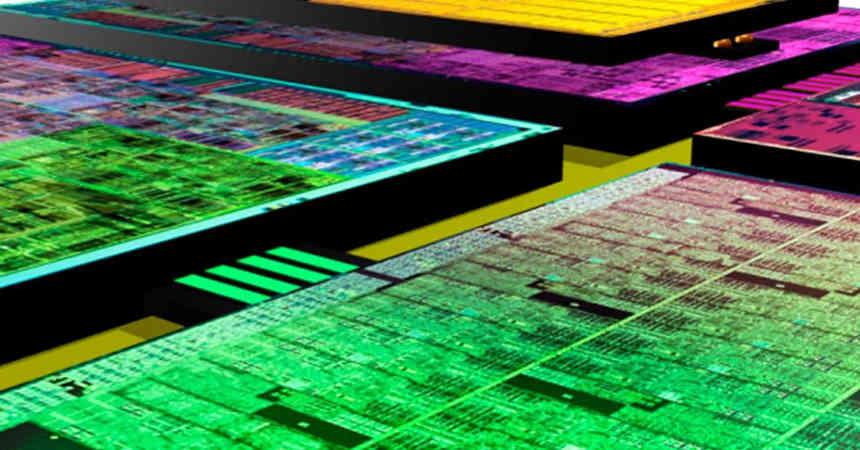

Việc áp dụng chiplet có nghĩa là Mạng lưới phân phối điện không chỉ được tích hợp trong mỗi chiplet, mà còn trong interposer kết nối chúng với nhau. Tính đến việc liên lạc nội bộ là tiêu thụ nhiều năng lượng nhất trong một bộ xử lý nguyên khối và hệ thống dây dẫn trong hệ thống chiplet làm tăng độ dài của nó giữa các chiplet khác nhau, thì thách thức lớn nhất là trong việc phân phối điện năng trong các cấu hình này.

Giải pháp? Nó xuất hiện thông qua việc sử dụng các kết nối dọc, ngắn hơn nhiều và số lượng lớn hơn. Loại thứ hai cho phép chúng hoạt động ở tốc độ đồng hồ thấp hơn và do đó ở điện áp thấp hơn. Một cái gì đó rất quan trọng để di chuyển lượng dữ liệu khổng lồ mà các ứng dụng như trí tuệ nhân tạo hoặc kết xuất đồ họa yêu cầu. Nhưng đồng thời điều này cũng đặt ra một loạt vấn đề trong việc thiết kế interposers, điều mà các bộ phận marketing thường không nói trước công chúng, nhưng đối với các kỹ sư lại trở thành một vấn đề rất đau đầu.

Trong mọi trường hợp, trong khái niệm chiplet, mặc dù thực tế là chúng ta có sự khác biệt về mặt vật lý chip, nhưng thực tế PDN của nó được thiết kế như thể nó là một bộ xử lý đơn lẻ.