การดำเนินการตาม อินฟินิตี้แคช ใน GPU ที่มีสถาปัตยกรรม RDNA 2 เป็นหนึ่งในความแปลกใหม่ของใหม่ เอเอ็มดี GPU สถาปัตยกรรม แต่คำถามที่อยู่ในใจคือมันเป็นสิ่งพิเศษเฉพาะสำหรับ AMD GPUs หรือเราจะไปดูโปรเซสเซอร์ Ryzen ทั้งในซีพียูและ SoCs?

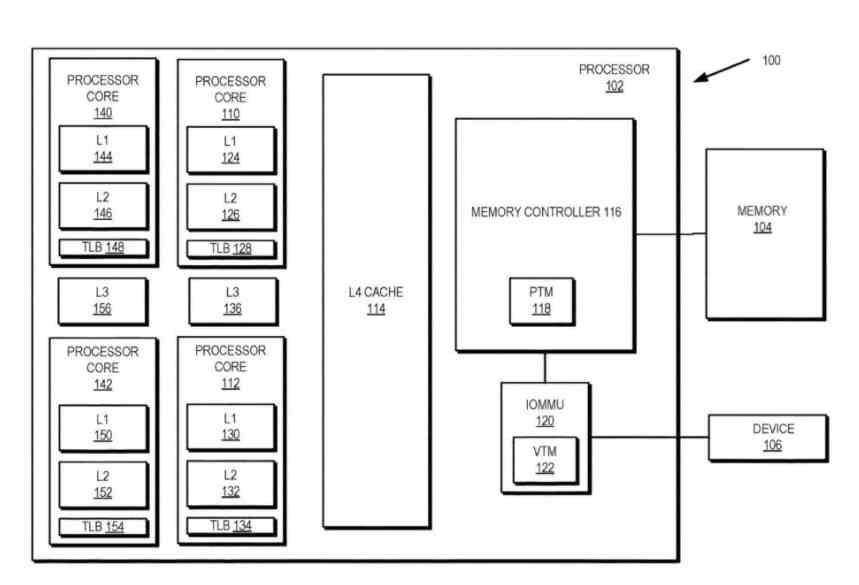

ไม่กี่เดือนที่ผ่านมาไดอะแกรมของสิทธิบัตร AMD รั่วไหลซึ่งสอดคล้องกับโปรเซสเซอร์ของตระกูล AMD Ryzen หรืออย่างนั้นเราคิดว่า แต่ด้วยความพิเศษของการแสดงแคชระดับที่สี่ในไดอะแกรมซึ่งเป็นสิ่งที่ไม่เคยมีมาก่อนในโปรเซสเซอร์ AMD ตามสถาปัตยกรรมดังกล่าว

ในเวลาเดียวกันการปรากฏตัวของ Infinity Cache ใน AMD GPUs ทำให้เกิดคำถามสองข้อ: เราจะได้เห็น Infinity Cache ที่ใช้ในโปรเซสเซอร์ AMD Ryzen ของ AMD หรือไม่จะใช้เป็นแคช L4 หรือในทางอื่น ๆ ได้หรือไม่?

ความขัดแย้งของยูทิลิตี้ของ Infinity Cache และ L3 Cache ของ Zen cores

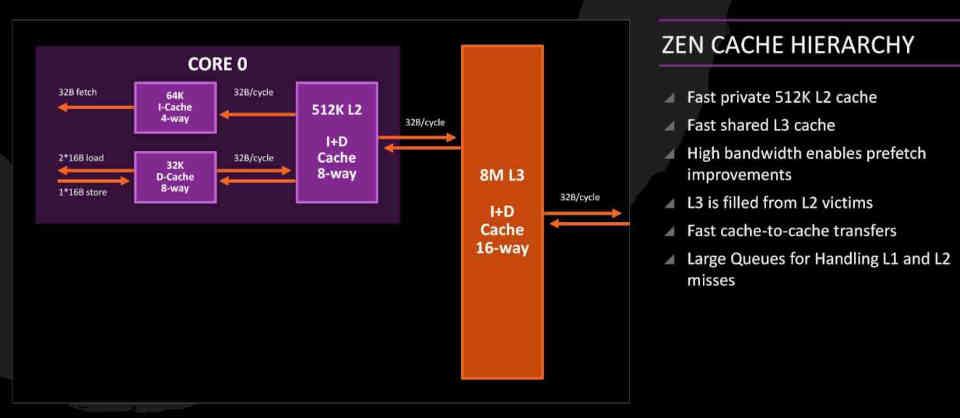

ทั้ง L3 cache ของ Zen cores และ Infinity Cache ของสถาปัตยกรรม RDNA 2 ทำหน้าที่เหมือนกันเนื่องจากทั้งสองเป็น Victim Caches จึงมีฟังก์ชันการทำงานเหมือนกัน ซึ่งหมายความว่าเมื่อต้องรวบรวมข้อมูลและคำแนะนำสำหรับโปรเซสเซอร์ที่เกี่ยวข้องแต่ละตัวจะมีหน้าที่รวบรวมบรรทัดแคชที่ถูกทิ้งโดยระดับแคชก่อนหน้านี้

อะไรคือปัญหา? เพื่อให้เข้าใจว่าเราต้องพิจารณาว่า Infinity Cache จะไปที่ใดหากมีการใช้งานทั้งใน SoC และ AMD ซีพียูก่อนตัวควบคุมหน่วยความจำและดังนั้นใน Northbridge เนื่องจากเป็นแคช L4 ที่ควรจะเป็น

ความขัดแย้งคืออะไร? ไม่มีเหตุผลที่จะมี Victim Cache ของ Victim Cache อื่นเนื่องจากในกรณีนี้ Infinity Cache จะเชื่อมต่อกับแคช L3 ของแกน Zen ซึ่งทำให้เกิดความขัดแย้งของฟังก์ชันระหว่างทั้งสองฝ่าย

การเชื่อมต่อ Infinity Cache ขัดแย้งกับแกน Zen

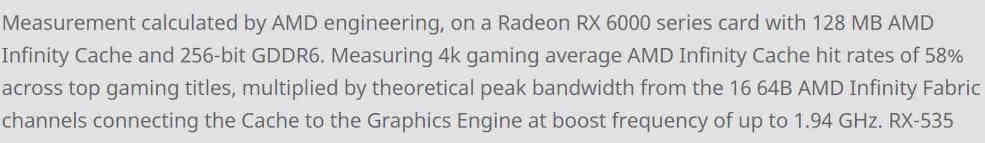

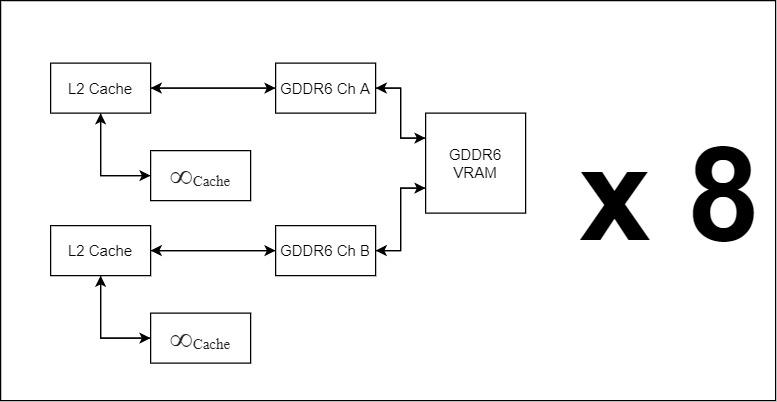

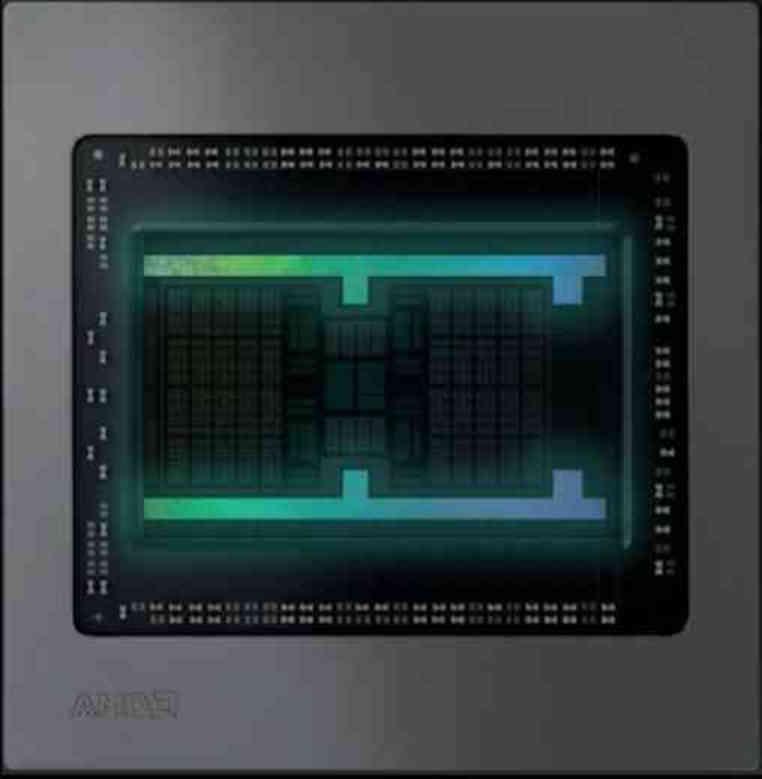

หากเราดู Infinity Cache ของ Navi 21 GPU เราจะพบว่ามีพาร์ติชั่นทั้งหมด 16 พาร์ติชั่นเชื่อมต่อที่ปลายด้านหนึ่งกับพาร์ติชันแคช L16 2 พาร์ติชันภายใต้บัส 64 ไบต์ / รอบสำหรับแต่ละพาร์ติชันและที่ปลายอีกด้านถึง 16 ช่อง GDDR6

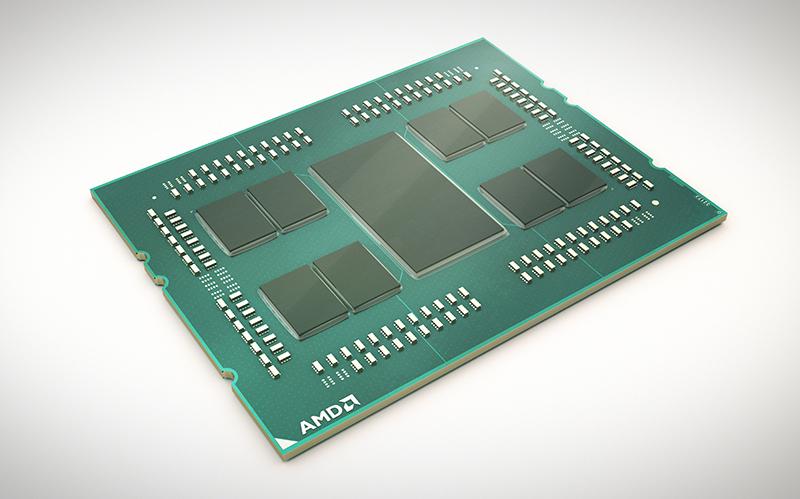

แกน Zen ของโปรเซสเซอร์ Ryzen ถูกจัดกลุ่มเป็น CCX แบบ 4 คอร์ (Zen และ Zen 2) หรือ 8 คอร์ (Zen 3) แต่ CCX ใช้อินเทอร์เฟซ Infinity Fabric เดียวดังนั้น Infinity Cache ที่ควรจะเป็นบนโปรเซสเซอร์ Zen เดียว มันจะประกอบด้วยพาร์ติชั่นจำนวนหนึ่งเท่ากับจำนวน CCX เป็นอย่างน้อย

ดังนั้นในการกำหนดค่าด้วย CCD คุณจะมีพาร์ติชั่นเพียงหนึ่งพาร์ติชั่นโดยหนึ่งพาร์ติชันมี 2 พาร์ติชัน 8 CCDs และในกรณีที่รุนแรงจะเป็นเช่น AMD Epyc ที่มี 8 CCD ที่มี XNUMX พาร์ติชัน ตามกฎทั่วไปแคชจะมีขนาดเพิ่มขึ้นตามระดับเพิ่มเติมแต่ละระดับและจะเป็นสองเท่าของผลรวมของระดับแคชก่อนหน้านี้เสมอ

Zen 3 CCD ตัวเดียวมีความจุ 32 MB ของ L3 Cache พาร์ติชันเดียวของ Infinity Cache คือ 8 MB ซึ่งเป็นตัวเลขที่ต่ำกว่าที่ต้องใช้ในการทำงานเป็น L4 Cache ของโปรเซสเซอร์ Zen ดังนั้นในการเชื่อมต่อจึงเป็น พิสูจน์แล้วว่า Infinity Cache ไม่สามารถทำงานเป็นแคช L4 ของโปรเซสเซอร์ที่มี Zen CPU ได้

แล้ว GPU ในตัวล่ะ?

เนื่องจากเราได้เห็นแล้วว่า Infinity Cache ไม่สามารถใช้เป็นแคชเพิ่มเติมของ Zen cores ได้อย่างไรคำตอบเดียวที่ยังคงอยู่คือ Infinity Cache ของ RDNA 2 cores ที่รวมอยู่ใน SoC ในขณะนี้ AMD ยังไม่ได้เปิดตัว SoC ใด ๆ ด้วย GPU สถาปัตยกรรม RDNA ในตัวเนื่องจากเวลาเปิดตัวเราไม่คิดว่าจะได้เห็น RDNA รุ่นแรก

ในกรณีของ iGPU นั้นสมเหตุสมผลที่จะรวม Infinity Cache ที่อยู่ระหว่างตัวควบคุมหน่วยความจำและตัวประมวลผลกราฟิก แต่จะมีไว้สำหรับการใช้งานกราฟิกโปรเซสเซอร์ภายใน SoC โดยเฉพาะ