แน่นอนคุณเคยได้ยิน (หรืออ่าน) พูดคุยเกี่ยวกับ รหัสแก้ไขข้อผิดพลาด ECC ในส่วนประกอบฮาร์ดแวร์จำนวนมากทั้งหมดเกี่ยวข้องกับหน่วยความจำ (เช่น แรม หรือที่เก็บข้อมูล) แม้ว่าจะมีน้อยมากที่เข้าใจถึงความสำคัญ ด้วยเหตุนี้ในบทความนี้เราจะอธิบายวิธีการทำงานของ ECC ในไฟล์ SSD ตัวควบคุม และวิธีขอบคุณมันเป็นไปได้ที่จะเพิ่มอายุยืนและสร้างความแตกต่างใหญ่ใน อายุการใช้งานของ SSD .

อุปกรณ์ทุกชิ้นที่ใช้หน่วยความจำแฟลช NAND จะต้องมีรหัสแก้ไขข้อผิดพลาดแบบสุ่ม (เรียกว่าข้อผิดพลาด“ อ่อน”) นี่เป็นเพราะมาก เสียงไฟฟ้า ผลิตภายในชิป NAND และระดับสัญญาณของบิตที่ผ่านห่วงโซ่ของชิป NAND นั้นอ่อนมาก

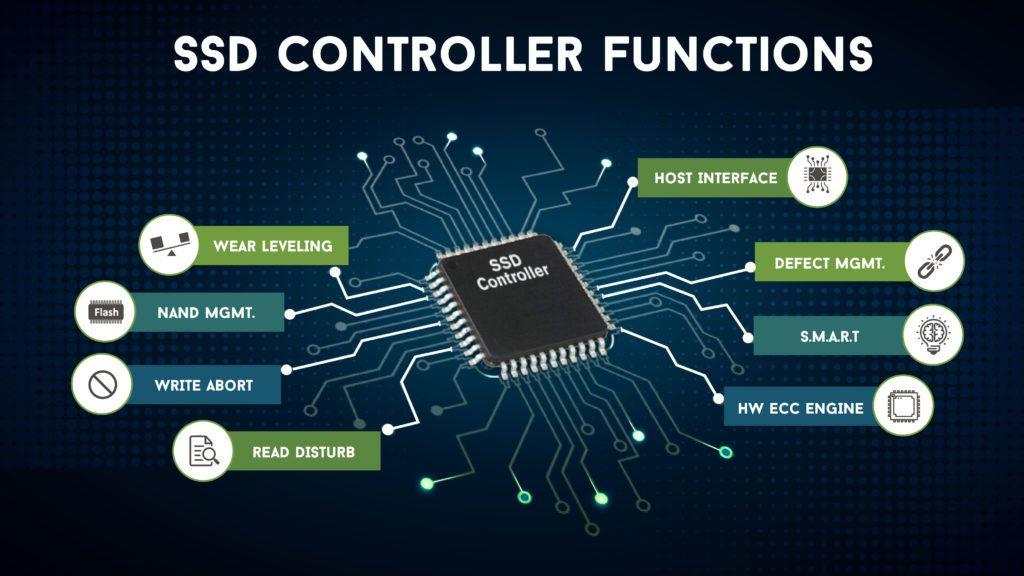

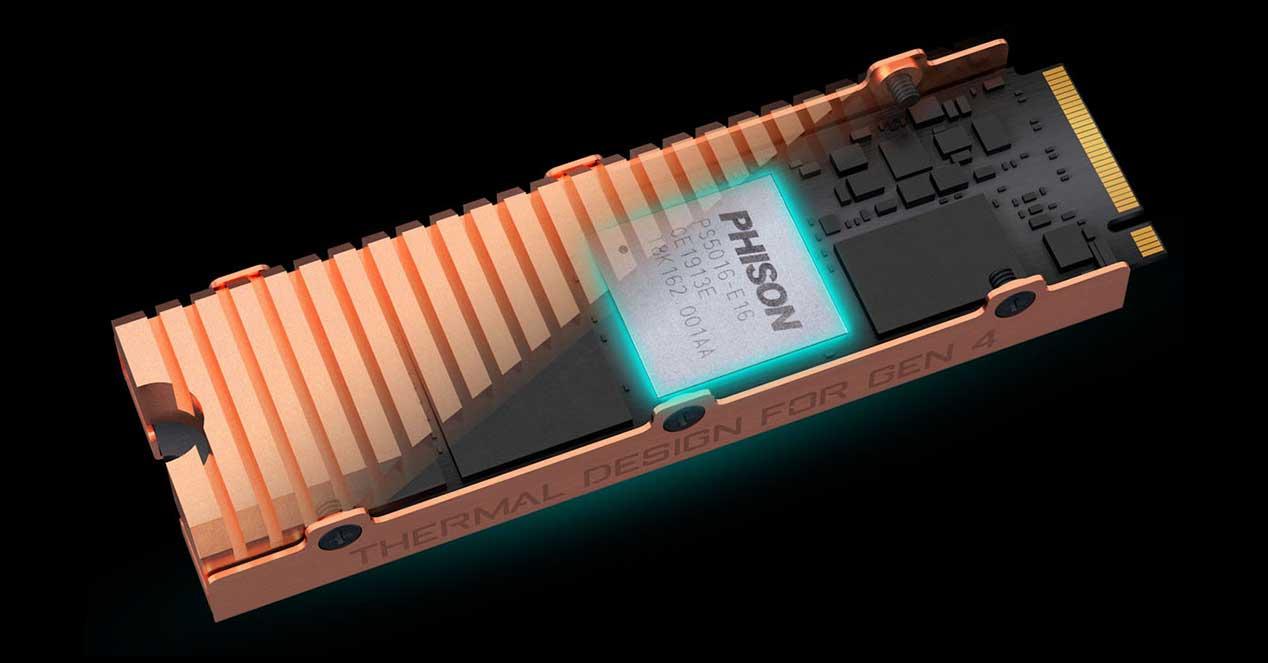

หนึ่งในวิธีที่ หน่วยความจำ NAND ได้กลายเป็น ถูกที่สุด ของทั้งหมดเป็นเพราะต้องการการแก้ไขข้อผิดพลาดที่จะดำเนินการจากองค์ประกอบนอกชิป NAND เอง; ในกรณีของ SSD ECC ดำเนินการกับคอนโทรลเลอร์ .

วิธีการทำงานของ ECC บนคอนโทรลเลอร์ SSD

การแก้ไขข้อผิดพลาดเดียวกันนี้ยังช่วยแก้ไขข้อผิดพลาดบิตเนื่องจาก สวมใส่บน หน่วยความจำ เซลล์ตัวเอง . การขัดสีอาจทำให้บิต“ ติดขัด” ในสถานะหนึ่งหรืออีกสถานะหนึ่ง (เรียกว่าข้อผิดพลาด“ ยาก” หรือข้อผิดพลาดอย่างหนัก) และสามารถเพิ่มความถี่ของข้อผิดพลาด“ อ่อน”

แม้ว่าจะไม่ใช่แนวคิดที่กว้างเกินไป แต่ความต้านทานของหน่วยความจำแฟลชเป็นการวัดจำนวนรอบการลบ / เขียนที่บล็อกแฟลชสามารถทนได้ก่อนที่ข้อผิดพลาด“ ยาก” จะเริ่มปรากฏขึ้น บ่อยครั้งที่ความล้มเหลวเหล่านี้เกิดขึ้นในแต่ละบิตเท่านั้นและหายากมากที่การบล็อกทั้งหมดล้มเหลว ด้วยจำนวนการลบ / เขียนที่สูงพออัตราความผิดพลาด“ อ่อน” จะเพิ่มขึ้นเนื่องจากกลไกอื่น ๆ ใน SSD เอง

If ECC เป็นไปได้ มือสอง เพื่อแก้ไขข้อผิดพลาด "ยาก" เหล่านี้และข้อผิดพลาด "อ่อน" จะไม่เพิ่มขึ้นดังนั้นอายุการใช้งานของบล็อกทั้งหมดจึงยาวขึ้นอย่างมากเกินกว่าความต้านทานที่ระบุโดยผู้ผลิต

ลองมาตัวอย่าง: สมมติว่าชิป NAND ที่ไม่ได้ใช้มีข้อผิดพลาด“ อ่อน” เพียงพอที่จะต้องใช้ ECC 8 บิตนั่นคือแต่ละการอ่านหน้าสามารถมีได้ถึง 8 บิตที่มีการสุ่มแบบสุ่ม (โดยทั่วไปเกิดจากสัญญาณรบกวนทางไฟฟ้า กำลังพูดถึง) ในตอนแรก). ECC ที่ใช้ในชิปนี้สามารถแก้ไขข้อผิดพลาด 12 บิตได้ ECC ไม่สามารถแก้ไขปัญหานี้ได้ เราควรพบข้อผิดพลาด 8“ อ่อน” เกี่ยวกับเสียงไฟฟ้าและอีก 5“ อ่อน” เนื่องจากการสึกหรอ

ตอนนี้ผู้ผลิตหน่วยความจำแฟลชรับประกันว่า 5 ข้อผิดพลาดแรกนั้นจะเกิดขึ้นหลังจากข้อมูลจำเพาะความแข็งแกร่งของ SSD ซึ่งหมายความว่าจะไม่มีบิตล้มเหลวเนื่องจากการสึกหรอจนกว่าวงจรการลบ / เขียนที่ระบุโดยผู้ผลิตจะเกิน พึงระลึกไว้ว่าสเป็คไม่แม่นยำพอที่จะคาดการณ์ว่าบิตถัดไปจะล้มเหลวและจริง ๆ แล้วอาจต้องใช้เวลาหลายพันลบ / เขียนรอบด้านบนสเป็คเพื่อให้สิ่งนี้เกิดขึ้น; โปรดจำไว้ว่าผู้ผลิตรับประกันว่ามันจะไม่เกิดขึ้นก่อน X รอบ แต่ไม่เมื่อมันจะเกิดขึ้นเมื่อพวกเขาเกิน

ซึ่งหมายความว่าอาจใช้เวลานานก่อน บล็อกเสียหายมาก ต้องลบออกจากบริการ (และสำหรับ SSD นี้มักจะมีบล็อก“ พิเศษ” เพื่อแทนที่วัตถุที่เสียหาย) ซึ่งหมายความว่า ความต้านทานของ ข้อผิดพลาดการแก้ไข ปิดกั้น อาจใหญ่กว่าความต้านทานที่ระบุหลายเท่าหลายครั้งทั้งนี้ขึ้นอยู่กับจำนวนข้อผิดพลาดส่วนเกินที่ ECC ออกแบบมาเพื่อแก้ไข

รหัสการแก้ไขข้อผิดพลาดมีผลกระทบอะไรกับ SSD

อย่างที่เราได้อธิบายไปก่อนหน้านี้หน่วยความจำแฟลชราคาถูกมากเพราะมันไม่ได้รวม ECC ไว้ในชิปเอง แต่ถูกรวมเข้ากับฮาร์ดแวร์ภายนอกอื่น ๆ และพวกคุณคิดว่ามันมีราคา ECC ที่มีความซับซ้อนมากขึ้นนั้นต้องการพลังการประมวลผลบนคอนโทรลเลอร์และอาจช้าลงหากอัลกอริทึมไม่ทันสมัย นอกจากนี้จำนวนข้อผิดพลาดที่สามารถแก้ไขได้จะขึ้นอยู่กับว่าภาคส่วนของหน่วยความจำขนาดใหญ่จะถูกแก้ไขดังนั้นตัวควบคุม SSD ที่มีอัลกอริทึม ECC ที่ซับซ้อนน่าจะใช้ทรัพยากรจำนวนมาก ลด SSD โดยรวม การปฏิบัติ . การปรับปรุงเหล่านี้ยังทำ คอนโทรลเลอร์มีราคาแพงกว่า .

อัลกอริทึม ECC มีสถานะทางคณิตศาสตร์ของตัวเองขึ้นอยู่กับตัวควบคุม (ในคำอื่น ๆ ไม่มีมาตรฐาน) และแม้แต่การเข้ารหัส ECC ขั้นพื้นฐานที่สุด (Reed-Solomon และ LDPC) ค่อนข้างซับซ้อนที่จะเข้าใจ เมื่อมีคนพูดถึงข้อ จำกัด ของแชนนอน (จำนวนบิตสูงสุดที่สามารถแก้ไขได้) มันเป็นปริมาณที่คุณไม่ทราบจากผู้ผลิตในข้อกำหนดทางเทคนิคนั้นเป็นเรื่องยากมากที่จะคำนวณ

เพิ่งติดกับมัน: บิตการแก้ไขเพิ่มเติมนำไปสู่อายุการใช้งานที่ยาวนานขึ้นสำหรับ SSD แต่ก็มีผลกระทบต่อประสิทธิภาพการทำงานหรือราคาผลิตภัณฑ์โดยต้องการคอนโทรลเลอร์ที่ทรงพลังกว่า