Från HBM-minnen Genom 3D NAND-marker , det finns många marker på hårdvarumarknaden som är byggda med hjälp av det som kallas TSV, akronymer som betyder "Through Silicon Vias" och översätts som via kisel genom att de korsar marken vertikalt och tillåter vertikal interkommunikation mellan dem. I den här artikeln kommer vi att berätta vad de är, hur de fungerar och vad de är för.

I hårdvaruvärlden talas det ofta om i termer som har att göra med hastighetshastigheter, vare sig det är ett minnes bandbredd, en processors klockcykler, hur många gånger en processor gör en typ av beräkning per sekund etc. , men väldigt sällan frågar vi oss hur chipsen kommunicerar med varandra och om detta betyder något.

![]()

I den här artikeln ska vi prata om en teknik som heter TSV, som används för att kommunicera marker, oavsett vad de är.

Vad är kisel- eller TSV-vägar?

Om vi tittar på de flesta moderkort kan vi se två saker: det första är att de flesta anslutningar mellan chips är horisontella, vilket innebär att banorna på kortet som skickar signalen mellan chips kommunicerar horisontellt.

Sedan har vi fallet med processorer, som placeras ovanpå en interposer som vi kallar ett uttag och där processorerna är anslutna vertikalt på dem.

Men i allmänhet observerar vi 99% av tiden att det vanligtvis inte finns några chips vertikalt kopplade till varandra, och trots att designen av chips och processorer utvecklas i den riktningen och det redan finns några exempel på denna typ på marknaden . Men hur gör vi det för att kommunicera två eller flera marker vertikalt?

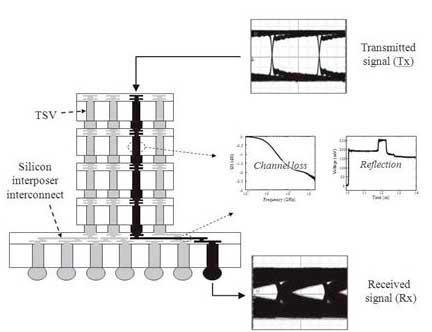

Tja, just detta görs med vad som kallas vägar genom kisel, som vertikalt korsar de olika chipsen eller lagren av samma chip som utgör stapeln, det är därför de kallas "genom" kisel eftersom de bokstavligen passerar igenom.

Tillämpningarna och fördelarna med att använda TSV: er

En av tillämpningarna av TSV är att det möjliggör separering av komplexa processorer som består av olika delar på flera olika chips med den extra fördelen att vertikal anslutning möjliggör ett större antal anslutningar, vilket hjälper till att uppnå högre bandbredd utan behov av en mycket hög klockfrekvens som ökar strömförbrukningen under dataöverföring.

Till exempel kommer vi i framtiden att se processorer och grafikprocessorer där deras sista nivå cache kommer att vara utanför chipet, med samma bandbredd men med en lagringskapacitet flera gånger större, vilket avsevärt kommer att öka prestandan. Vi har också exemplet på Intel Foveros som använder TSV för att kommunicera de två delarna av Lakefield SoC, Compute Chiplet med Base Die där systemets I / O är.

Anledningen till att dela upp en processor i olika delar är i det faktum att när ett chip blir större är chanserna för ett fel i kretsarna växande mer och mer, och därför är antalet bra chips utan fel som de kan användas mindre och de som gör det bra måste betala kostnaden för de som har misslyckats; Detta innebär att att minska storleken på marker teoretiskt sänker den totala kostnaden, men senare kommer vi att se att detta inte är helt fallet.

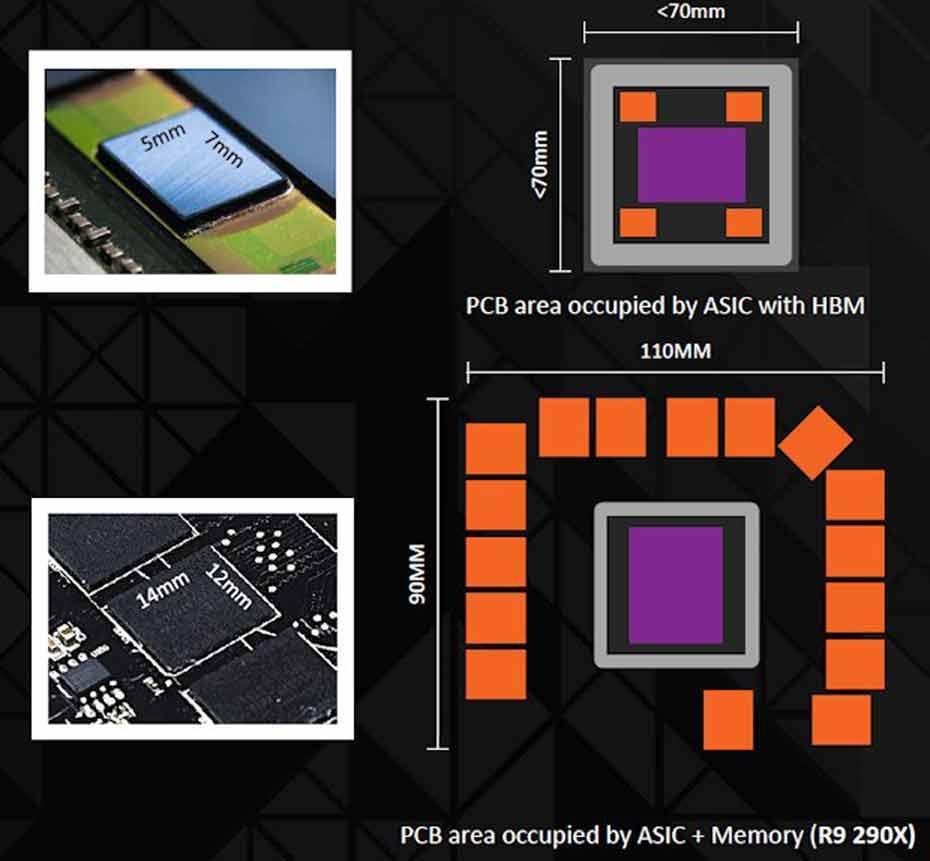

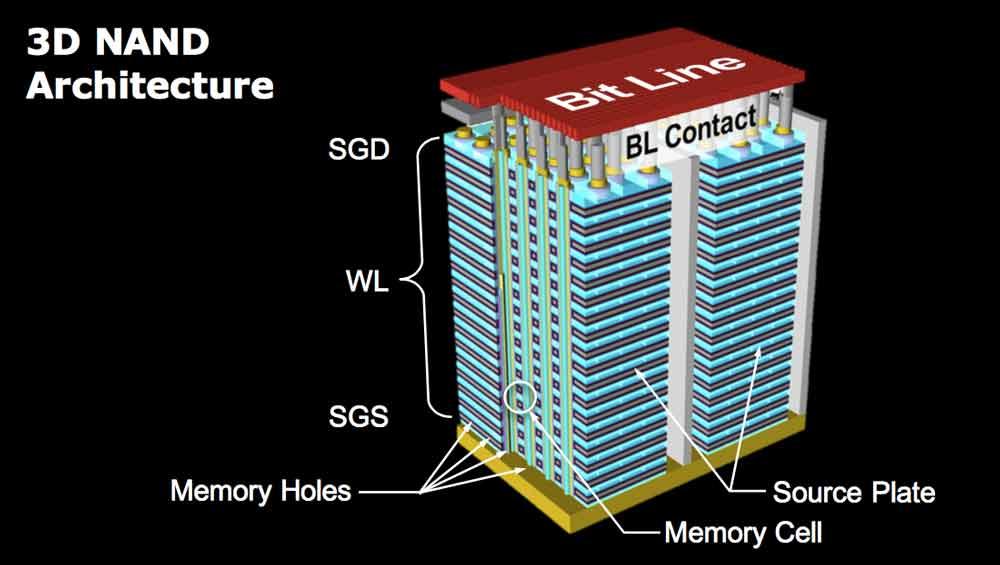

Den andra applikationen har att göra med det ockuperade utrymmet; faktumet att kunna stapla flera marker vertikalt minskar avsevärt det område de upptar, eftersom de inte är utspridda om kortet, det mest kända exemplet på detta är HBM-minnet som används som VRAM för vissa grafikprocessorer, men vi har andra exempel som som Samsungs V-NAND-minne, som staplar flera NAND Flash-minneschips ovanpå varandra.

Andra mindre kända alternativ är kombinationen av logik och minne, där minnet placeras ovanpå en processor, det mest kända exemplet är Wide I / O-minne, en typ av minne som visades i smartphones för några år sedan och bestod av ett minne ovanpå SoC sammankopplat genom kisel.

Varför är antagandet av kiselvägar så långsamt?

TSV har flera inneboende problem, vilket har inneburit att trots att det varit en mycket lovande teknik på papper i årtionden, har det inte riktigt tagit fart och har varit ett sätt att tillverka chips för mycket små marknader men med höga marginaler.

- Deras första problem är att det är en extremt dyr teknik att implementera som kräver djupa förändringar i tillverkningslinjerna för många företag, som har tillverkat chips utan TSV i flera år och för många applikationer har den konventionella tillverkningsprocessen visat sig vara tillräckligt bra. .

- Det andra problemet är att om en del av det som utgör den vertikala strukturen misslyckas helt, så måste hela strukturen kastas bort, och detta gör system sammankopplade via TSV mycket dyrare att tillverka. Exemplet med HBM-minne är viktigt i detta, dess kostnad är så hög att det inte är lönsamt som ett minne för konsumentmarknaden.

- Det tredje problemet är termisk kvävning, chipsen når klockhastigheterna de når under vissa temperaturförhållanden, vilket påverkas om det finns ett annat chip i närheten som också avger värme. Vi kan till exempel ha två processorer som separat når 1 GHz vardera men tillsammans placeras vertikalt i en TSV-struktur når endast 0.8 GHz vardera på grund av temperaturproblem.

Den tredje punkten är den som mest oroar ingenjörerna idag och kylmekanismer utvecklas för att hålla chipsen som utgör stacken så kalla som möjligt för att undvika problem med termisk drunkning.