Igår pratade vi om fördelarna med det Intel hade över AMD, där en av avsnitten just var innovation. Bevis på detta är vad som presenterades av Intel för sin 3D-staplingsteknik, som naturligtvis kommer att bilda framtidens högpresterande marker, inte utan problem. Företaget verkar ha hittat lösningen på nästan alla problem som denna teknik medför genom vad det har kallat Intel ODI.

Innan vi går in på frågan om att förklara vad denna teknik består av, måste vi förstå vad som har varit orsakerna som har lett till att Intel utvecklade den, vilka har varit problemen och var var begränsningarna.

Endast på detta sätt kan vi förstå komplexiteten i hela denna fråga och hur företaget har lyckats lösa dessa problem på ett mycket intelligent sätt.

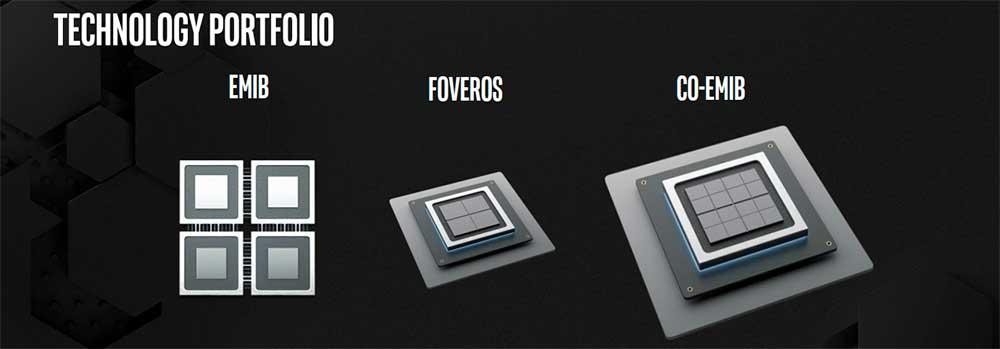

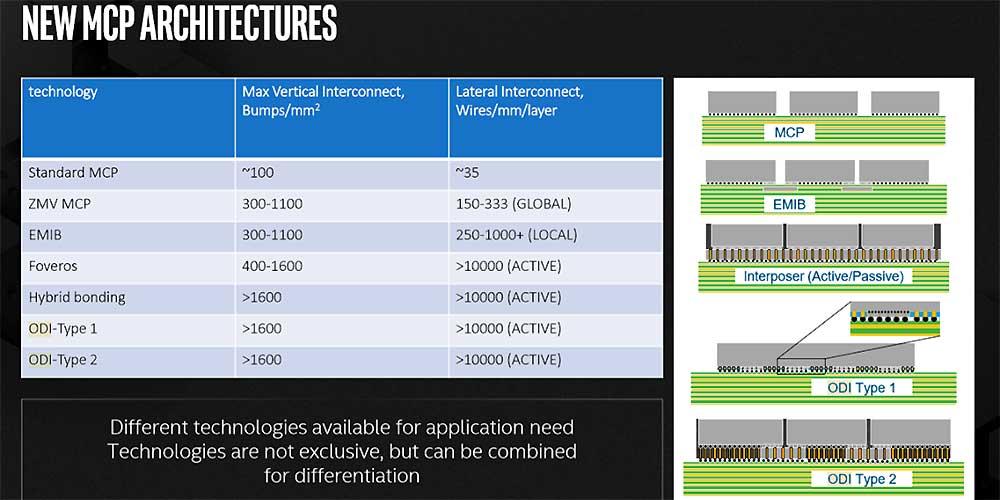

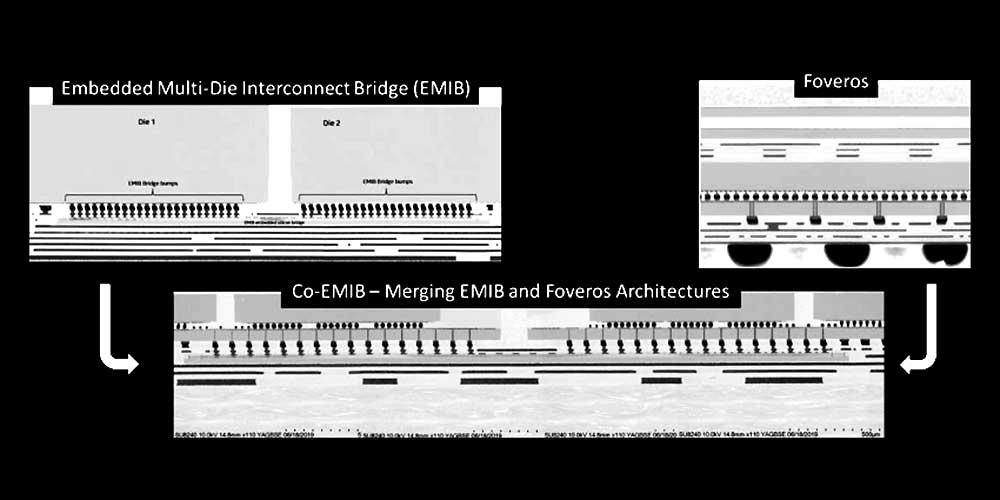

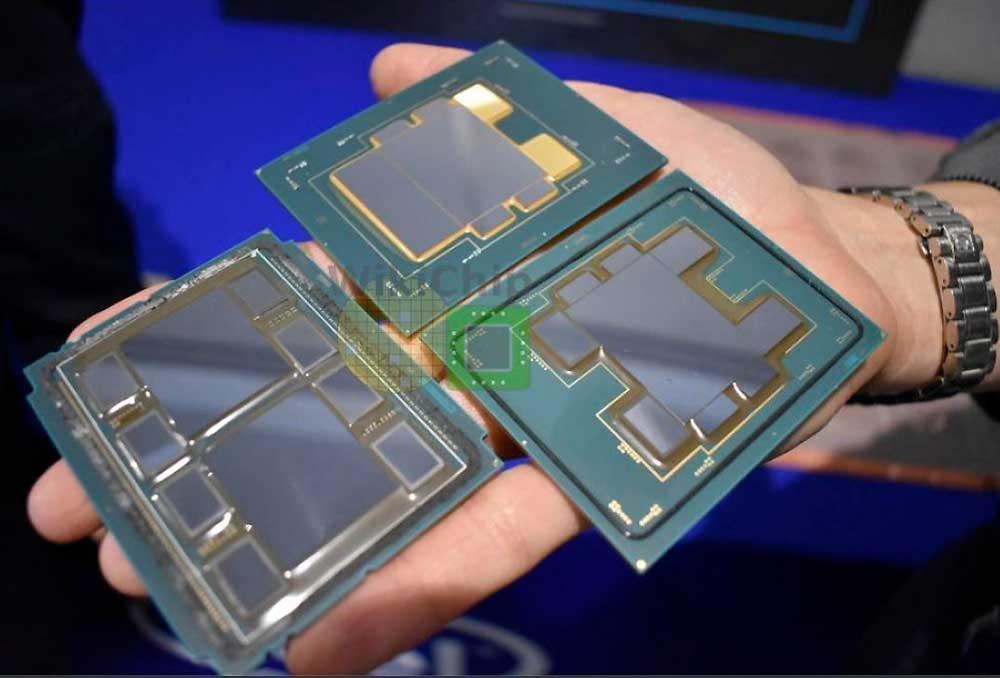

Först av allt, och för att skapa ett mentalt schema, arbetar Intel för närvarande med tre olika staplingstekniker som sträcker sig från minst till mest komplexa: EMIB, Foveros och CO-EMIB.

Den första är den så kallade 2.5D-tekniken, den andra är den första riktiga 3D-generationen, medan den senare kombinerar båda för att erbjuda mycket mer komplexa produkter. Även om vi redan har sett dem separat, kommer vi att göra en snabb genomgång av dem alla för att placera oss igen.

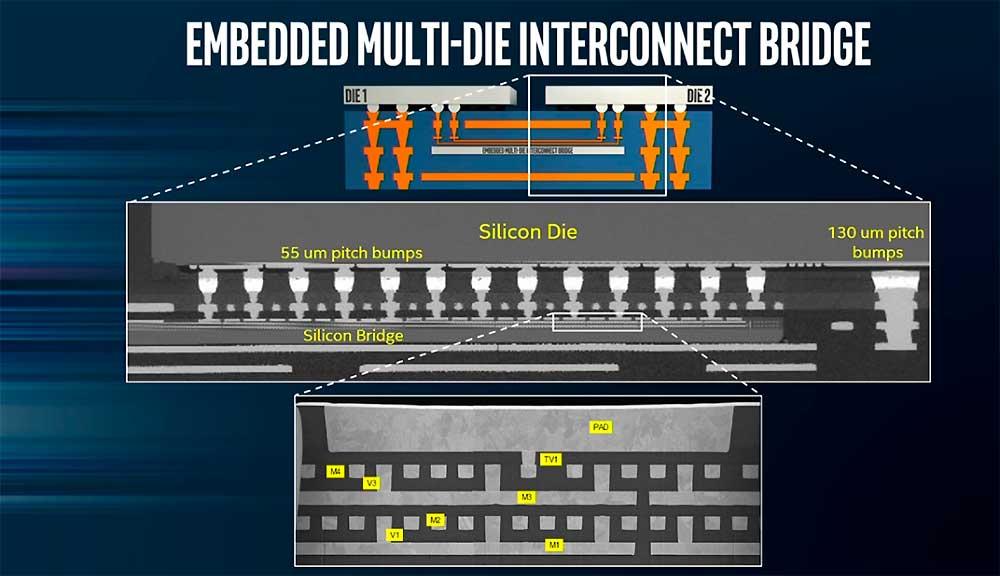

Intel EMIB

Förkortning för Embedded MultiInterconnect Bridge, det är ett 2.5D-system som vi redan känner till eftersom det debuterade med Kaby Lake G och inkluderade en Intel-matris med motsvarande kärnor, cache, register etc ..., en munstycke som tillhör AMD via en RX Vega M och en 4 GB HBM2-stack, allt i en enda interposer som löddes till bärbara moderkort.

EMIB är därför en medelstor interconnect-teknik som låter dig extrahera hela prestandan för varje chip som ingår i interposern.

Intel Foveros

Det är det första steget i revolutionen som vi kommer att se, riktig 3D-stapling. Detta är inget annat än att sammanföra olika matriser vertikalt, det ena ovanpå det andra, i stället för horisontellt som det har gjorts tills nu.

Det är vad Intel kallar Ansikte mot ansikte och representerar en serie ganska intressanta och samtidigt något logiska problem. Det första är ett elektriskt problem, eftersom det är nödvändigt att föra tillräckligt med energi till den övre matrisen och för att göra detta, är det nödvändigt att gå igenom den mellanliggande / de. Detta löstes delvis med TSV-samtal, men dessa är motvilliga att tillhandahålla stora mängder spänning och även om man lägger till mer detta kan lösas, finns det problemet att det dyraste av ett 3D-chip för närvarande exakt är att lägga till TSV av kvalitet och volym.

Slutligen står Intel inför ett temperaturproblem. Det övre munstycket kan kylas, men samtidigt representerar det en termisk motstånd för de nedre, eftersom den övre på varje vertikal munstycke hindrar värmeöverföringen och genererar ett kedjeproblem.

Intel CO-EMIB

Det är i grund och botten en sammanslagning, att kalla det på något kolloktiskt sätt, mellan EMIB och Foveros. Det är en 3D-stapling där den horisontella längden används och lindrar därför på något sätt båda problem, men löser inte dem.

Så Intel måste komma med en ny teknik som var kompatibel med alla sina tre förpackningsmodeller och samtidigt upphör med alla problem vi har pratat om, och det är just där ODI kommer in.

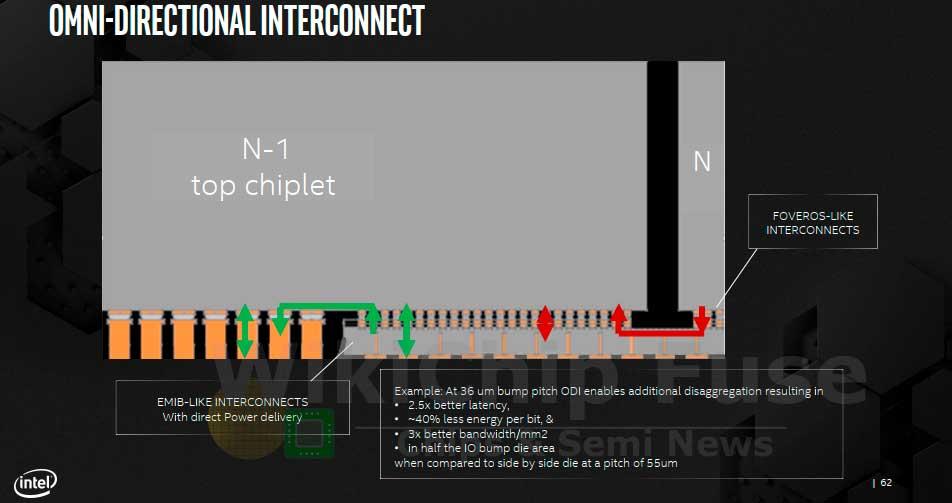

Intel ODI

ODI är förkortningen för Omni-Directional Interconnect och det är inte en teknik i sig, utan en grupp av dem, det vill säga, ODI omfattar en serie specifika lösningar som kan öka över tid eller utvecklas som sådana.

Dess huvudfunktion är baserad på kraftleverans och syftar till att avbryta problemen med EMIB och Foveros, eftersom det som standard slutar problemen med CO-EMIB.

Allt är baserat på vad Intel kallar 3D-förpackningar Flöden , som inte är annat än interna samtrafikvägar för att förbättra ankomsten av energi och samtidigt förbättra värmeavledningen med en enda typ av teknik.

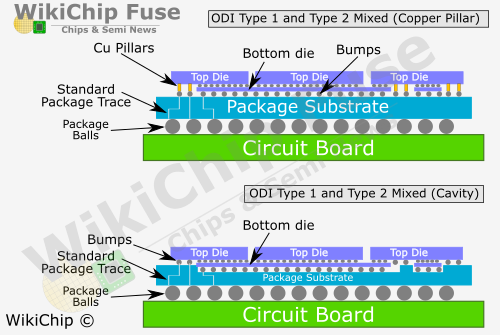

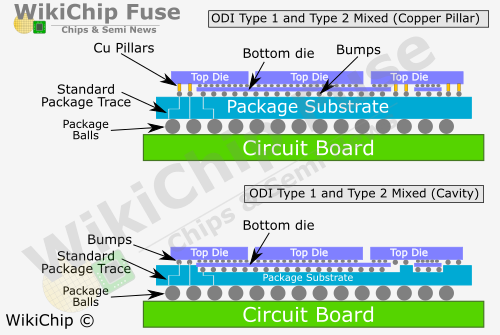

Just nu är Intel ODI uppdelad i två allmänna typer och dessa förvandlas till två kompletterande tekniker, vilket gör totalt fyra varianter. Typ 1-varianten fokuserar på problem mellan den nedre och den övre matrisen, medan Type 2 gör det mellan de nedre munstyckena som, vertikalt sett, helt under en övre dyna.

Det vill säga ett Foveros-paket och ett CO-EMIB-paket, där Intel EMIB logiskt kommer in. Förklarade detta går vi med de olika typerna mer i djupet.

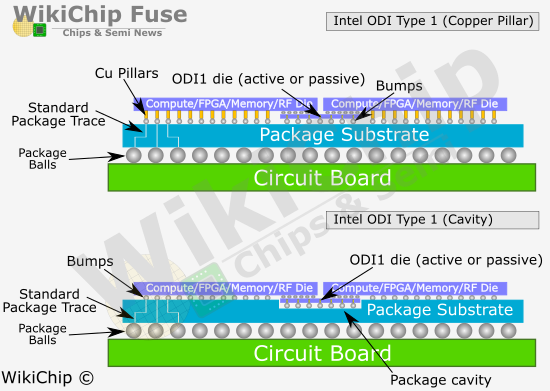

Intel ODI typ 1

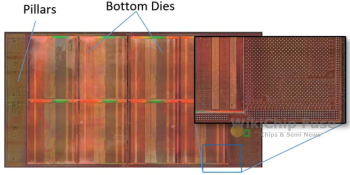

Det första vi måste föreställa oss är att matrisen vi ska prata om är av olika storlekar, vilket är viktigt eftersom sättet att sammankoppla dem varierar beroende på deras dimensioner. Med detta i åtanke måste vi föreställa oss ett större munstycke som ligger under två mindre övre dynor, eller i det mest extrema fallet är det ett större munstycke som ligger under ett annat mindre munstycke som logiskt sett inte täcker hela det nedre området.

För att ge en mer eller mindre enkel likhet är det en pyramideffekt: den nedre basen har alltid ett större område än den övre, med skillnaden att det här bara finns en matris och på toppen kan den ha en mindre eller flera, men de når aldrig så stora som den nedre.

Fördelen med detta är att Intel har utformat systemet så att bottenformningen endast täcker den del av toppstycket där bindning mellan dem krävs. Anledningen till detta har sin logik: du eliminerar nackdelarna med TSV: er och behåller alla Foveros. Eftersom endast den del av föreningen mellan matrisen används kan Intel göra en aktiv eller passiv ODI av typ 1.

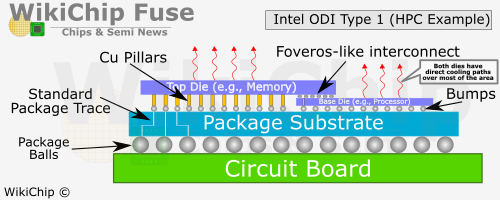

Detta innebär att om det är passivt är det bara begränsat till föreningen mellan båda stansarna, men om den är aktiv fungerar den som en sammankopplingsdatasändare, vilket är mycket användbart om du vill lägga till från HBM staplar till extern cache eller en iGPU . Därför och om vi går tillbaka till det mentala schemat, om flera dör i olika storlekar används med hjälp av ODI 1, får alla ha tillgång till bättre värmespridning, där IHS i vissa fall måste vara specifikt, men en tillgång uppnås. direkt till den och därför löses temperaturproblemen.

Detta är viktigt eftersom om vi tittade på båda dörerna från en santvyn, skulle det bara finnas en del av dem som skulle vara anslutna, det väsentliga, medan resten av munstycket är oberoende och förblir i luften i båda fallen, med två naturliga höjder naturligtvis och det är just det som skiljer det från EMIB som en teknik.

För att inte tala om att blandningen mellan båda stansarna måste göras med termisk kompression, bland annat.

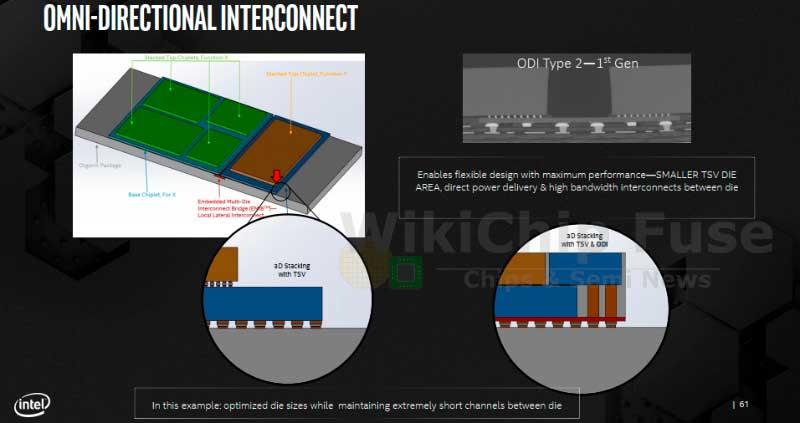

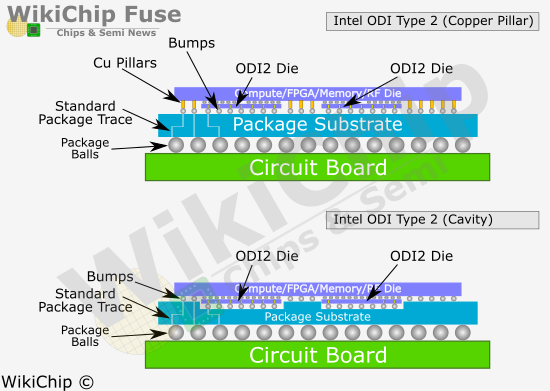

Intel ODI typ 2

Här ökar problemet, eftersom det nedre munstycket alltid är under det övre munstycket, det vill säga att det inte finns någon del av munstycket som är under det som sticker ut från det som är ovanför. Detta ger nackdelen med värme, men det har samtidigt en tydligare fördel: den nedre munstycket kan placeras exakt där det krävs jämfört med det övre munstycket och antalet anslutningar kan vara mycket högre.

Denna teknik är inriktad på att lindra prestanda och anslutningsproblem mellan matriser, där överordnadens prestanda alltid maximeras, såsom bättre ingångs- och utgångsförbindelser, mer hastighet i cacheminnet, outsourcing dem utan straff och oändliga. av möjligheter.

Du kan göra en Zen 2-stil I / O och lämna cachema från kärnorna i olika matriser, göra intakta kärnor och i tre olika nivåer utan förlust av prestanda eftersom de är direkt anslutna till varandra genom fysiska fackföreningar med TSV. Fördelarna med detta är så uppenbara att det är absurt att ens kommentera dem.

Här är problemet temperaturen, men med ODI Type 2 är det tänkt att placera formen med den lägsta energiförbrukningen i nedre delen och att skala vertikalt tills den placerar matriserna som genererar mer värme i det övre skiktet, för att kunna vara kyls med IHS, vilket ger några riktigt fantastiska CPU konfigurationsalternativ och möjliggör segregering för inkluderande effektivitet.

Som vi sagt har ODI Type 1 och Type 2 två olika versioner: Kopparpelare och kavitet där i den första kopparpelaren skulle användas för att kompensera för den högre höjden, medan under det andra underlaget formades till den nedre formen så att man kan använda bulor istället för pelare.

Intel ODI kan blanda båda typerna för att erbjuda mer komplexa CPU: er

En annan fördel med ODI som teknik är att den inte är exklusiv, det vill säga båda typerna kan användas med sina två versioner på samma CPU. Därför modularitet att vi kommer att kunna se i framtidens CPU: er av en sådan kaliber att komplexiteten i dess design kommer att bli den största utmaningen för Intel.

Den mest uppenbara frågan är samtidigt den mest relevanta: när kommer vi att se dessa processorer på marknaden? En riktigt svår fråga att svara på. Tänk på att ODI som teknik bara är några månader gammal, den implementeras för närvarande och den måste förbättras när det gäller att förenkla processen, men Intel har vågat erbjuda ungefärliga datum: 2022 eller 2023.

ODI som teknik kommer att lyckas förkorta tidsfristerna, eftersom det löser de två huvudproblemen för de tre Intel-teknologierna, så de första processorerna (de behöver inte vara för skrivbordet uppenbarligen) kunde ses i produktionen 2024, eftersom de var riktigt optimistiska , eftersom Som ofta är fallet släpps mindre kraftfulla versioner först och när både process och produktion poleras och förbättras erbjuds högpresterande version.

I vilket fall som helst är detta inte science fiction, det här är en verklighet, påtaglig, som redan har funnits på marknaden med Kaby Lake G och Stratix 10 och vilket utan tvekan är processorns framtid, vilket är en mycket större revolution än Multi die eller MCM på grund av dess komplexitet, är det definitiva steget för att kunna pallera väggen som vi kommer att hitta med de litografiska processerna tillbaka 2030 och det kan utan tvekan vara det föregående steget till mer komplexa tekniker som lämnar vad vi för närvarande har i blöjor på marknaden.