Etter hvert som tiden har gått, har vi sett stadig sterkere prosessorer dukke opp, men vi har blitt fortalt mer enn en gang at ytelsen etter et visst punkt ikke lenger skaleres naturlig med de nye nodene. Det er flere grunner til dette, men en av de viktigste er fenomenet kjent som RC Delay.

Maskinvaren til PCene våre gjør bare en ting, overfører elektriske signaler mellom komponentene med forskjellige spenninger. Avhengig av spenningen som brukes, har informasjonen som overføres en eller annen betydning. Etter hvert som nye produksjonsnoder er opprettet, har nye fenomener oppstått, men den som har forverret seg mest har vært RC Delay.

Hva er RC Delay?

RC Delay kan oversettes som forsinkelsen til det elektriske signalet som produseres av kombinasjonen av motstand og kapasitans til den delen av kretsen. Når vi snakker om motstand, snakker vi om vanskeligheter som elektroner må passere gjennom den bestemte delen av kretsen. Kapasitansen er derimot kapasiteten den delen av kretsen har til å lagre den elektriske ladningen.

RC Delay har de siste årene blitt et av de største problemene for designere av nye chips under nye produksjonsnoder. Grunnen? Vi har normalt konseptet at chips består av logiske porter, som består av transistorer. Virkeligheten er at disse logiske portene er sammenkoblet med hverandre gjennom en mikrokobling som går gjennom kretsen og som de forskjellige elektriske signalene sendes gjennom.

Slik at signalet som skiller en logisk gate fra en annen overføres uten at det er variasjoner i det elektriske signalet som kan føre til en variasjon av den uønskede informasjonen. Det som gjøres er å plassere lag av dielektrisk materiale mellom kablene signalet går gjennom. overført. Problemet er at når tettheten per område blir større med de nye produksjonsnodene, da avstanden mellom mikrokoblingen reduseres samtidig, og dermed øker risikoen for at signalet blir forvrengt.

Signaler og kretser

Vi har en tendens til å forstå at enhver digital integrert krets fungerer ved å benytte seg av ener og nuller, noe som er en forenkling av konseptet. I virkeligheten snakker vi om å overføre informasjon gjennom den interne mikrotilkoblingen til brikken under to forskjellige spenninger der den varierer kontinuerlig fra den ene til den andre.

Det som er viktig i en krets er ikke bare at signalet overføres riktig, men at det overføres i riktig periode. RC Delay antar også hastigheten elektronene sirkulerer gjennom den elektriske kretsen og påvirker derfor prosessorens endelige klokkehastighet.

Problemet i de siste nodene? Selv om transistorene har skalert seg innenfor det forventede, har ledningene ikke gjort det i samme grad, og de er forholdsvis større med hensyn til de tidligere nodene, og derfor har ikke klokkehastigheten skalert som forventet. Med andre ord er det sammenkoblingen mellom de forskjellige logiske komponentene i en prosessor og dens interne minner som førte til slutten av MHz-løpet.

Leieregelen og dens forhold til RC Delay

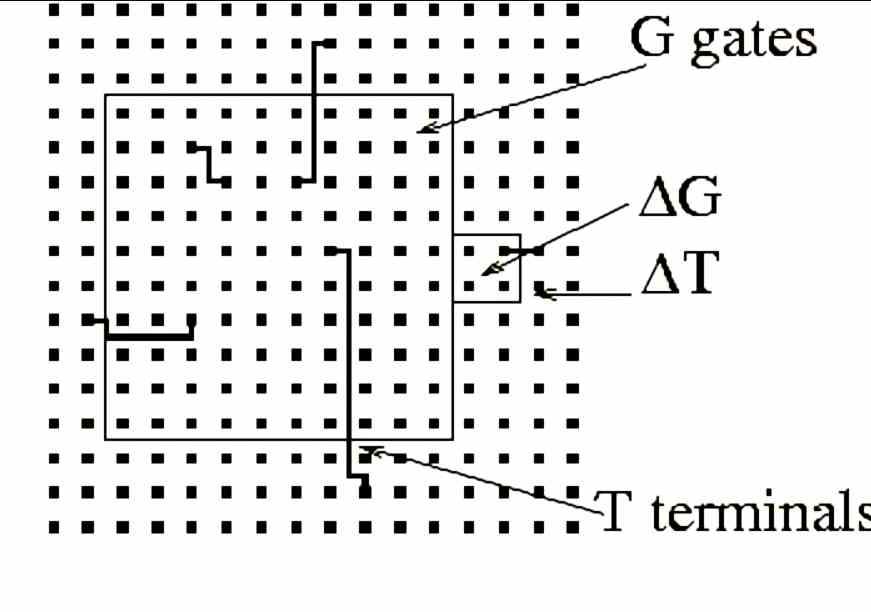

Rent's regel er relatert til organisering av beregningslogikk i en chip og spesifikt til ledningene som kobler sammen de forskjellige logikkmodulene som er en del av en prosessor når den er på designbordet. Hva er leieregelen for? Vel, å vite hvor mange sammenkoblinger en mikroprosessor skal ha.

Formelen for leieregelen er som følger:

T = AK p

Der T er antall terminaler og derfor mikrokabler i hele brikken, er A gjennomsnittlig antall mikrokabler innen hver logikkblokk, og K er gjennomsnittlig antall logiske porter i hver blokk i brikken. Hva har det med RC Delay å gjøre? Vel, fordi Rent-regelen tillater systemarkitekter ikke bare å kjenne ledningene og plasseringen av designene deres, men også lengden på mikrokablingen og derfor RC Delay.

Vi kan ikke glemme at kablingens avstand også er relatert til energiforbruk, og jo lenger en kabel er, jo større er forbruket i dataoverføring, så arkitekter må vite hvordan de skal balansere mellom forventet klokkehastighet og chipforbruk.

Ikke alt håp er tapt

RC Delay til tross for at det er et eksisterende problem, er ikke noe som blir ignorert av skaperne av nye mikroprosessorer og minner. Det er fremskritt de siste årene som har å gjøre med målet om å lindre det voksende problemet med RC Delay med de nye produksjonsnodene, spesielt to typer fremskritt blir brukt parallelt:

Den første av disse er søket etter nye dielektriske materialer som tillater mer effektiv isolasjon av det elektriske signalet som distribueres gjennom terminal til terminal. Så en god del av forskningen og utviklingen for de nye produksjonsnodene for å lage nye CPUer, GPUer og minne er ikke bare basert på å redusere størrelsen på transistorene, men på å løse problemene som oppstår med de nye nodene.

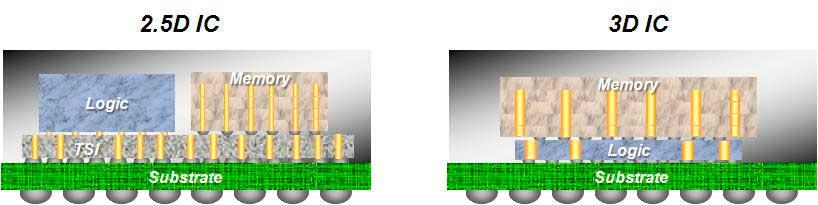

Den andre er i bruk av vertikale strukturer for kommunikasjon av elementene, som vi ikke øker antall terminaler med, men hvis avstanden mellom dem og derfor ender vi opp med å redusere mulighetene for at signalet fra en mikrokabel påvirker en annen avstanden mellom disse. Det eneste problemet med denne tilnærmingen? For øyeblikket har vi sett implementert i stor skala hva som er vertikale sammenkoblinger av minne over minne og til og med logikk over minne, men fremtiden peker på det faktum at vi skal se logikk over logikk for å skalere klokkehastigheten til forskjellige prosessorer.