Als het gaat om het meten van de prestaties van RAM en VRAM hebben we het meestal over twee prestatieparameters, namelijk bandbreedte en latentie. Maar wat is de relatie tussen deze twee kenmerken en kunnen we ze als constant classificeren?

Een van de problemen met technische specificaties is dat ze de neiging hebben om de gegevens onder perfecte omstandigheden 100% te laten werken. In het geval van geheugen gebeurt dit niet, aangezien niet alle gegevens dezelfde latentie hebben en de bandbreedte nooit 100% is.

Meer bandbreedte betekent niet minder latentie

We begrijpen als latentie tussen een verwerkingseenheid en het bijbehorende geheugen, de tijd die nodig is om de gevraagde informatie te ontvangen of om het signaal te ontvangen dat er een wijziging in het geheugen is aangebracht. Latency is dus echt een manier om tijd te meten.

De bandbreedte is in plaats daarvan de hoeveelheid gegevens die in elke seconde wordt verzonden, dus het is een snelheid. Dus door directe logica kunnen we gaan denken dat met een hogere snelheid wanneer we naar gegevens zoeken, dan in minder tijd de CPU, GPU of een andere verwerkingseenheid krijgt de gegevens.

De realiteit is dat dit niet het geval is, bovendien is er de bijzonderheid dat hoe meer bandbreedte een geheugen heeft, het gewoonlijk meer latentie heeft in vergelijking met andere. Dit fenomeen heeft een verklaring, en dat gaan we u in de volgende secties van dit artikel uitleggen.

Het zoeken naar gegevens zorgt voor meer latentie

Bijna alle verwerkingseenheden hebben tegenwoordig een hiërarchie van caches, waarin de processor ze elk eerst zal vragen voordat hij toegang krijgt tot RAM. Dit komt doordat de directe latentie tussen de processor en het RAM groot genoeg is om te resulteren in prestatieverlies ten opzichte van de ideale processor.

Stel je voor dat je op zoek bent naar een specifiek product, het eerste wat je doet is kijken in de plaatselijke winkel, dan in een iets grotere winkel en tenslotte in een warenhuis. het bezoek aan elk etablissement gebeurt niet onmiddellijk, maar vereist reistijd. Hetzelfde gebeurt in de cache-hiërarchie, dit wordt een "cache-misser" genoemd, dus we kunnen de tijd als volgt samenvatten:

Zoektijd = Zoeken tijd in de eerste cache + cache miss-periode +… zoektijd in de laatste cache.

Als de cache-opzoektijd langer is dan de tijd die nodig is om naar het hoofd-RAM te gaan, zal het cachesysteem slecht zijn ontworpen op een processor omdat het het doel waarvoor de cache zou zijn gemaakt, tart.

Nu is het latentieprobleem complexer, aangezien we aan de toegangstijd die wordt toegevoegd door de cache-zoekopdracht de latentie moeten toevoegen die wordt toegevoegd om de gegevens in RAM te doorzoeken als deze niet in RAM worden gevonden. Met welke problemen kunnen we onszelf vinden? Welnu, alle geheugenkanalen zijn bijvoorbeeld bezet en er wordt een conflict gecreëerd, dat optreedt wanneer RAM geheugenkanalen heeft bezet en andere gegevens ontvangt of aflevert.

Hoe beïnvloedt latentie de bandbreedte?

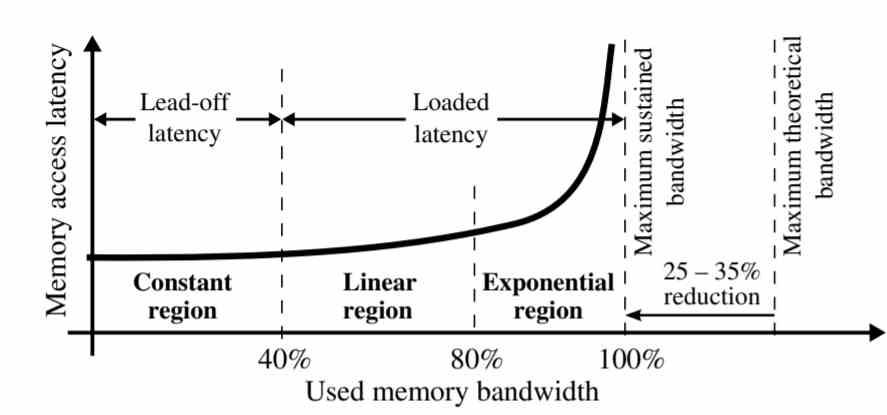

Zoals te zien is in de grafiek, is de latentie niet voor alle geheugenbandbreedte hetzelfde.

- Constante regio: De latentie blijft constant op 40% van de aanhoudende bandbreedte.

- Lineair gebied: Tussen 40 en 80% van de aanhoudende bandbreedte neemt de latentie lineair toe. Dit gebeurt vanwege het feit dat er een oververzadiging is van verzoeken aan het geheugen die zich aan het einde hebben verzameld als gevolg van conflicten.

- Exponentiële regio: In de laatste 20% van het bandbreedtegedeelte groeit de gegevenslatentie exponentieel, alle geheugenverzoeken die in de vorige periode niet konden worden opgelost, stapelen zich op in dit deel, waardoor er onenigheid tussen hen ontstaat.

Dit fenomeen heeft een heel eenvoudige verklaring, de eerste verzoeken aan het geheugen die worden beantwoord, zijn degene die als eerste worden gevonden, de meeste bevinden zich in de cache wanneer deze een kopie heeft, maar de aanvragen die niet in de cache staan, worden verzameld. Een van de verschillen tussen caches en RAM is dat de eerste meerdere gelijktijdige toegangen kan ondersteunen, maar wanneer het zoeken naar gegevens in RAM plaatsvindt, is de latentie veel hoger.

We hebben de neiging om RAM voor te stellen als een soort waterstroom waarin gegevens niet stoppen met circuleren met de opgegeven snelheid, terwijl RAM niet echt gegevens gaat verplaatsen tenzij het erom vraagt. Met andere woorden, latentie heeft invloed op de doorvoer en dus op de bandbreedte.

Manieren om latentie te verminderen

Als we eenmaal weten dat onenigheid over toegang tot gegevens latentie veroorzaakt en dit van invloed is op de bandbreedte, moeten we nadenken over oplossingen. Het duidelijkste is het feit dat het aantal geheugenkanalen met RAM wordt verhoogd, precies dit is een van de sleutels waarmee HBM-geheugen een lagere toegangslatentie heeft dan GDDR6, aangezien 8 geheugenkanalen minder conflicten toelaten dan met 2 kanalen van GDDR6.

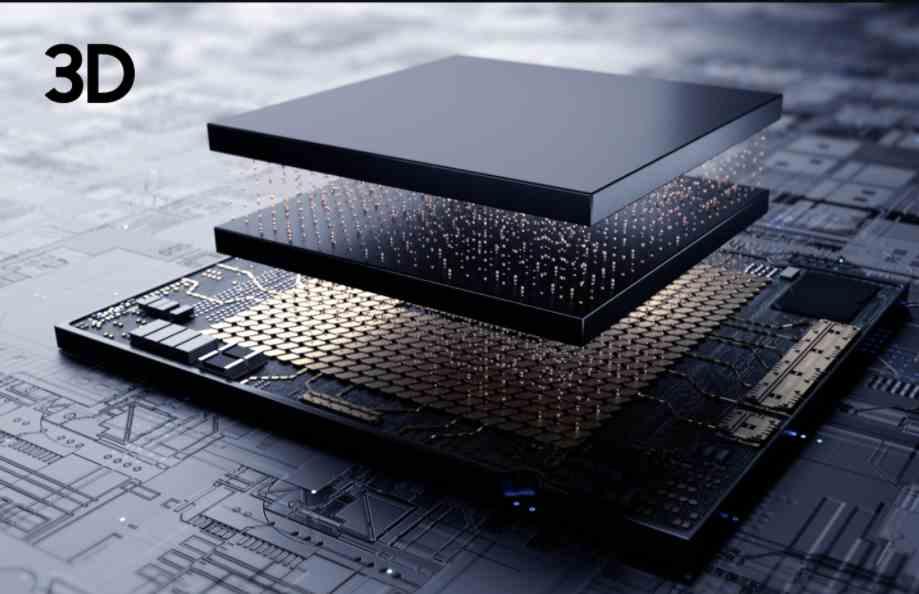

De beste manier om de latentie te verminderen, is door geheugen zo dicht bij de processor als een cache te creëren, maar het is onmogelijk om RAM te creëren met voldoende opslagcapaciteit om volledig functioneel te zijn. We kunnen een geheugenchip plaatsen en deze via TSV verbinden, maar omdat het geheugen zo dichtbij is om thermische verdrinking te voorkomen en daarmee de effectieve bandbreedte.

In dit geval, aangezien latentie de bandbreedte beïnvloedt, vanwege de nabijheid tussen geheugen en processor, zou het effect van latentie op het geheugen veel lager zijn. De afweging van het implementeren van een CPU of GPU met 3DIC? Het zou de kosten van de pc verdubbelen en het complexere fabricageproces zou ervoor zorgen dat er minder eenheden bij ons komen, ergo meer schaarste en dus zelfs duurdere prijzen.