कल हमने उन फायदों के बारे में बात की थी इंटेल खत्म हो चुका था एएमडी, जहां एक खंड नवाचार के ठीक था। इसका प्रमाण इंटेल द्वारा अपनी 3 डी स्टैकिंग तकनीक के लिए प्रस्तुत किया गया है, जो भविष्य की उच्च-प्रदर्शन चिप्स का निर्माण करेगा, न कि बिना किसी समस्या के। लगता है कि कंपनी ने लगभग सभी समस्याओं का हल ढूंढ लिया है जो इस तकनीक को कहते हैं इंटेल ODI।

यह समझाने के मामले में जाने से पहले कि इस तकनीक में क्या है, हमें यह समझना चाहिए कि क्या कारण हैं जिन्होंने इंटेल को इसे विकसित करने के लिए प्रेरित किया है, क्या समस्याएं हुई हैं और कहां सीमाएं थीं।

केवल इस तरह से हम इस पूरे मामले की जटिलता को समझ सकते हैं और कंपनी ने कैसे इन समस्याओं को बहुत ही बुद्धिमानी से हल करने में कामयाबी हासिल की है।

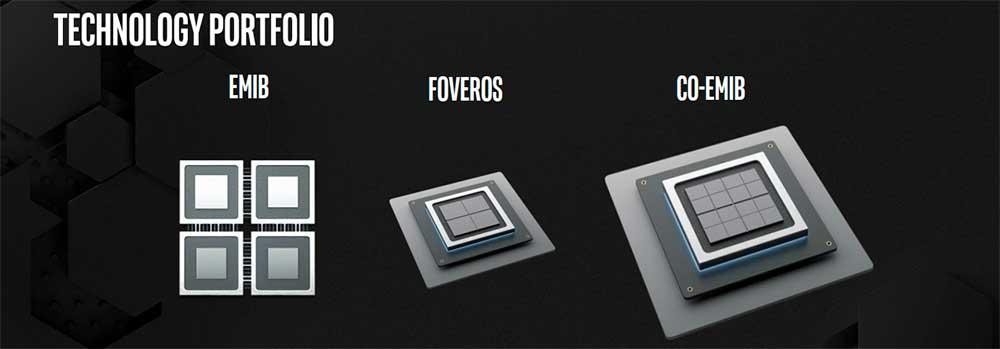

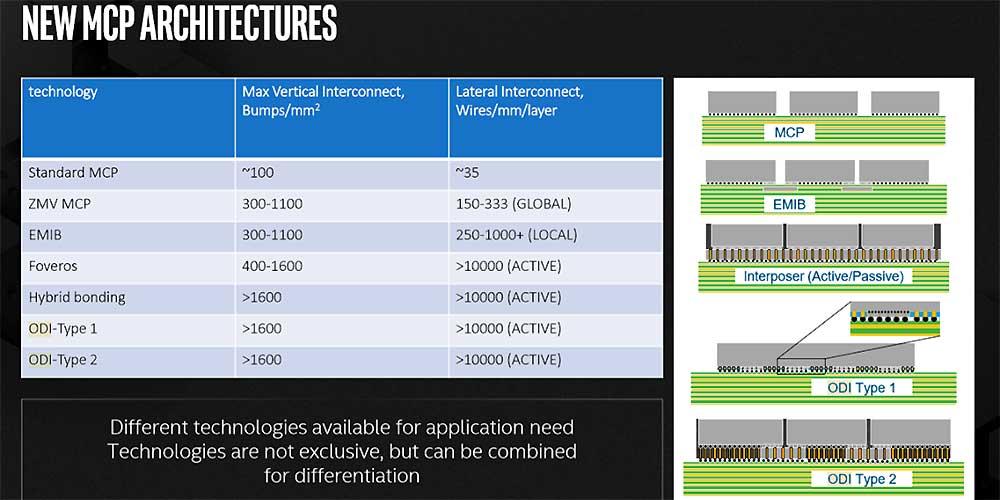

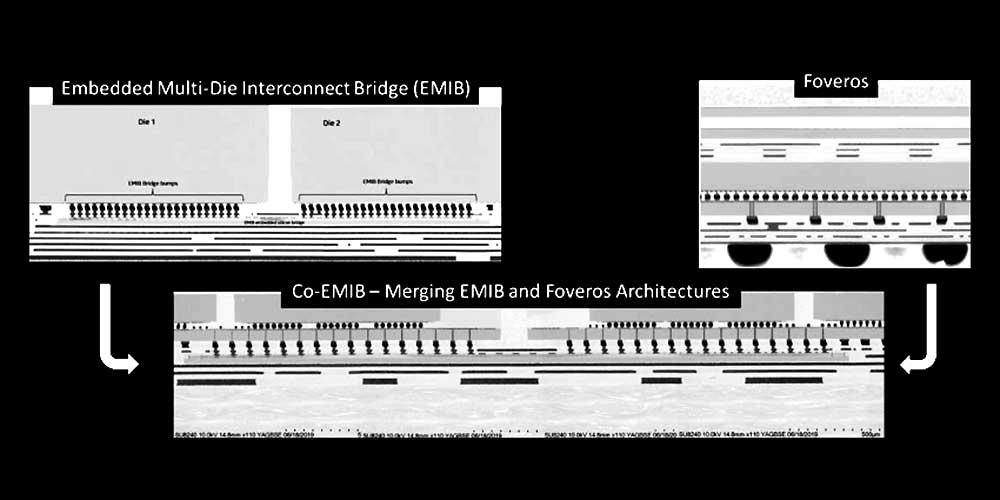

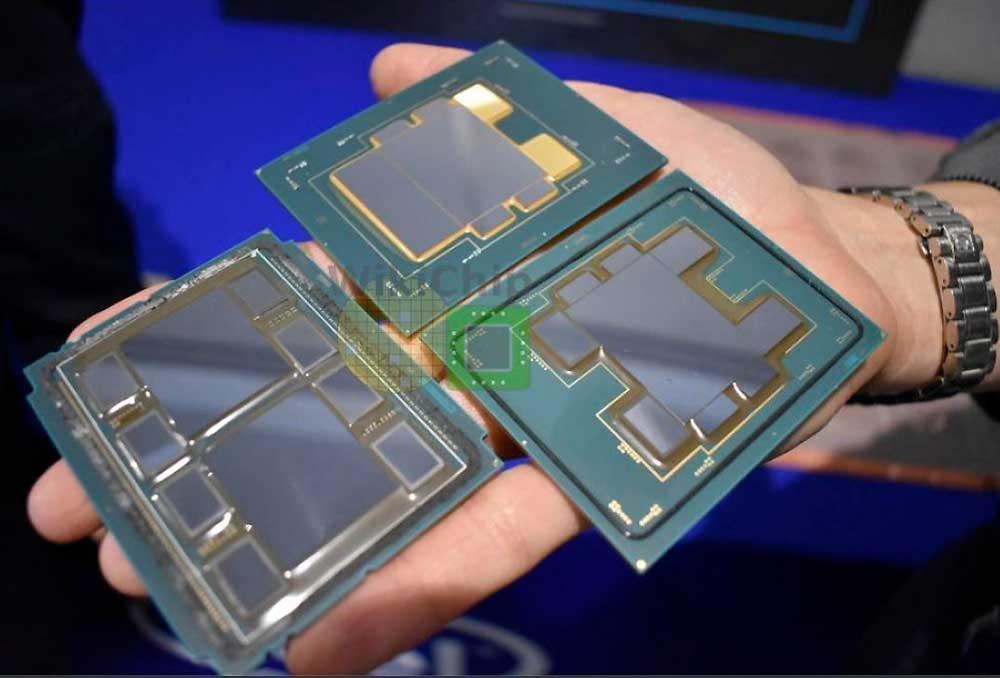

सबसे पहले, और एक मानसिक योजना बनाने के लिए, इंटेल वर्तमान में तीन अलग-अलग स्टैकिंग तकनीकों के साथ काम करता है जो कम से कम सबसे अधिक जटिल हैं: EMIB, Foveros और CO-EMIB।

पहला तथाकथित 2.5 डी तकनीक है, दूसरा पहली वास्तविक 3 डी पीढ़ी है, जबकि बाद वाला दोनों को अधिक जटिल उत्पादों की पेशकश करता है। यद्यपि हमने उन्हें पहले से ही अलग-अलग देखा है, हम फिर से खुद को स्वस्थ करने के लिए उन सभी की त्वरित समीक्षा करेंगे।

इंटेल EMIB

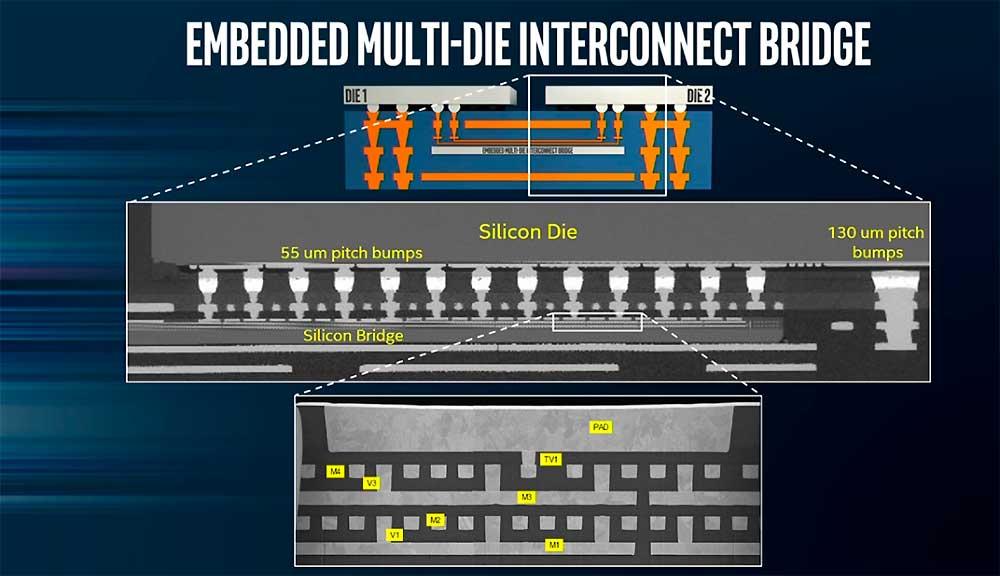

एंबेडेड मल्टीइंटरकनेक्ट ब्रिज के लिए रेटिंग, यह एक 2.5D सिस्टम है जो हमारे लिए पहले से ही परिचित है, क्योंकि यह पहली बार शुरू हुआ था कैबी झील जी और एक इंटेल अपने संबंधित कोर, कैश, रजिस्टर आदि के साथ मर गया ..., एक RX वेगा M और एक 4GB HBM2 स्टैक के माध्यम से एएमडी से संबंधित एक डाई, जो कि सभी एकल इंटरपोसर में लैपटॉप मदरबोर्ड को मिलाया गया था।

EMIB इसलिए एक मध्यम-स्केल इंटरकनेक्ट तकनीक है जो आपको प्रत्येक चिप के पूर्ण प्रदर्शन को निकालने की अनुमति देता है जो कि इंटरपोज़र में शामिल है।

इंटेल फेवरोस

यह क्रांति का पहला चरण है जिसे हम साक्षी देंगे, असली 3 डी स्टैकिंग। यह क्षैतिज रूप से, अब तक किए गए के बजाय, एक के ऊपर एक, विभिन्न मरने को परस्पर जोड़ने से ज्यादा कुछ नहीं है।

यह इंटेल कॉल है आमने सामने और काफी रोचक और उसी समय कुछ तार्किक समस्याओं की एक श्रृंखला का प्रतिनिधित्व करता है। पहली एक विद्युत समस्या है, क्योंकि ऊपरी मरने के लिए पर्याप्त ऊर्जा लाना आवश्यक है और ऐसा करने के लिए, मध्यवर्ती एक / से गुजरना आवश्यक है। यह आंशिक रूप से टीएसवी कॉल के साथ हल किया गया था, लेकिन ये बड़ी मात्रा में वोल्टेज की आपूर्ति करने में अनिच्छुक हैं और हालांकि इसे अधिक जोड़ने से इसे हल किया जा सकता है, समस्या यह है कि वर्तमान में 3 डी चिप की सबसे महंगी ठीक है TSV गुणवत्ता और मात्रा की।

अंत में, इंटेल एक तापमान समस्या का सामना करता है। ऊपरी डाई को प्रशीतित किया जा सकता है, लेकिन साथ ही यह निचले लोगों के लिए एक थर्मल प्रतिरोध का प्रतिनिधित्व करता है, क्योंकि प्रत्येक ऊर्ध्वाधर में ऊपरी एक गर्मी के हस्तांतरण में बाधा डालती है और एक श्रृंखला समस्या उत्पन्न करती है।

इंटेल CO-EMIB

यह मूल रूप से एक विलय है, इसे ईएमआईबी और फेवरोस के बीच कुछ बोलचाल में कहा जाता है। यह एक 3 डी स्टैकिंग है जहां क्षैतिज लंबाई का उपयोग किया जाता है और इसलिए किसी तरह दोनों की समस्याओं को कम करता है, लेकिन उन्हें हल नहीं करता है।

इसलिए इंटेल को एक नई तकनीक के साथ आना पड़ा, जो अपने तीनों पैकेजिंग मॉडलों के साथ संगत थी और साथ ही साथ उन सभी समस्याओं का भी अंत कर दिया, जिनके बारे में हम बात कर चुके हैं, और यह ठीक उसी जगह है जहाँ ODI आता है।

इंटेल ODI

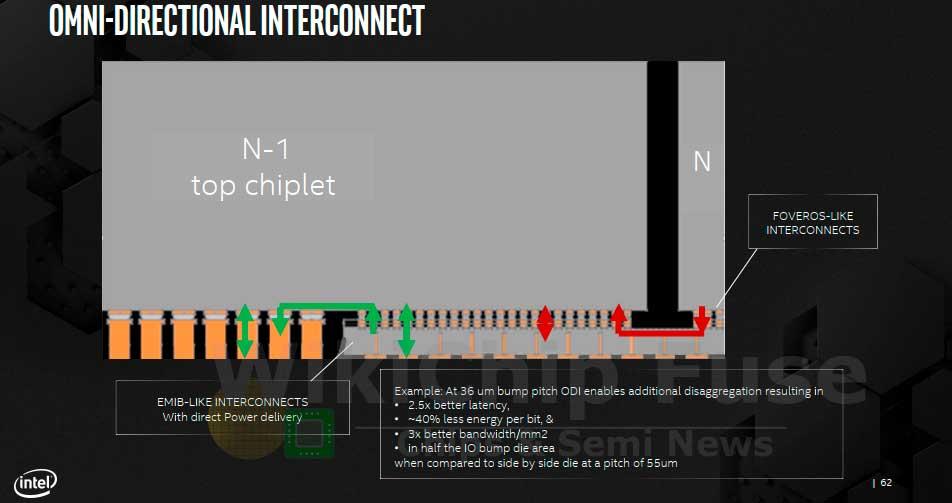

ODI के लिए संक्षिप्त नाम है ओमनी-डायरेक्शनल इंटरकनेक्ट और यह अपने आप में एक तकनीक नहीं है, लेकिन उनमें से एक समूह, अर्थात्, ODI विशिष्ट समाधानों की एक श्रृंखला को शामिल करता है जो समय के साथ बढ़ सकते हैं या इस तरह विकसित हो सकते हैं।

इसका मुख्य कार्य बिजली वितरण पर आधारित है और इसका उद्देश्य EMIB और Foveros की समस्याओं को समाप्त करना है, क्योंकि डिफ़ॉल्ट रूप से ऐसा करने से CO-EMIB की समस्याएं समाप्त हो जाती हैं।

सब कुछ इंटेल क्या कहता है पर आधारित है 3 डी पैकेजिंग प्रवाह , जो ऊर्जा के आगमन को बेहतर बनाने के लिए आंतरिक परस्पर संपर्क मार्ग से अधिक कुछ नहीं हैं और एक ही समय में एक ही प्रकार की प्रौद्योगिकी के साथ गर्मी लंपटता में सुधार करते हैं।

फिलहाल, Intel ODI में विभाजित है दो सामान्य प्रकार और ये दो पूरक प्रौद्योगिकियों में बदल जाते हैं, जो कुल चार वेरिएंट बनाते हैं। टाइप 1 वैरिएंट निचले और ऊपरी मर के बीच की समस्याओं पर ध्यान केंद्रित करता है, जबकि टाइप 2 निम्न मृत्यु के बीच ऐसा करता है जो कि, खड़ी बोली, पूरी तरह से ऊपरी मृत्यु के नीचे है।

यही है, एक Foveros पैकेज और एक CO-EMIB पैकेज, जहां Intel EMIB तार्किक रूप से प्रवेश करता है। यह समझाया कि हम गहराई में विभिन्न प्रकारों के साथ चलते हैं।

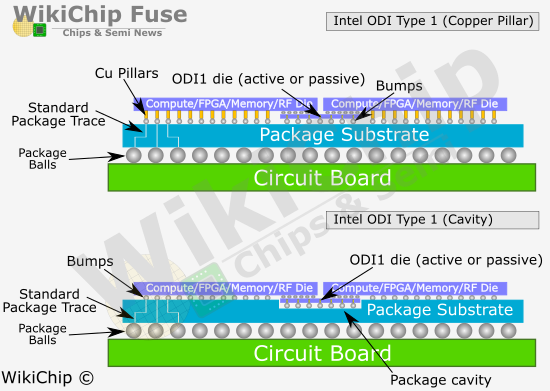

इंटेल ODI टाइप 1

पहली बात जो हमें सोचनी चाहिए वह यह है कि जिस डाई के बारे में हम बात करने जा रहे हैं वह विभिन्न आकारों की है, जो महत्वपूर्ण है क्योंकि उनके परस्पर जुड़ने का तरीका उनके आयामों के कारण भिन्न होता है। इसे ध्यान में रखते हुए हमें एक बड़े डाई की कल्पना करनी होगी जो कि दो छोटे ऊपरी मर के नीचे है, या सबसे चरम मामले में, यह एक बड़ी मौत है जो एक और छोटी मौत से नीचे है जो तार्किक रूप से सभी निचले क्षेत्र को कवर नहीं करता है।

अधिक या कम सरल उपमा देने के लिए, यह एक पिरामिड प्रभाव है: निचला आधार हमेशा ऊपरी एक से अधिक क्षेत्र का होता है, इस अंतर के साथ कि यहां केवल एक ही मरता है और शीर्ष पर यह एक छोटा या कई हो सकता है, लेकिन वे कभी भी नीचे तक नहीं पहुंच पाते हैं।

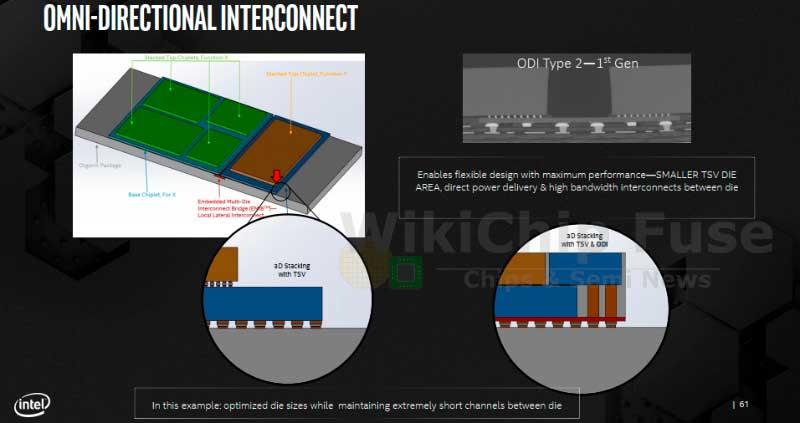

इसका लाभ यह है कि इंटेल ने सिस्टम को डिज़ाइन किया है ताकि नीचे की डाई केवल शीर्ष मरने के हिस्से को कवर करे जहां उनके बीच बॉन्डिंग आवश्यक हो। इसका कारण इसके तर्क हैं: आप टीएसवी के नुकसान को खत्म करते हैं और उन सभी फेवरोस को रखते हैं। चूंकि मरने के बीच संघ के केवल भाग का उपयोग किया जाता है, इंटेल एक सक्रिय या निष्क्रिय प्रकार 1 ODI बना सकता है।

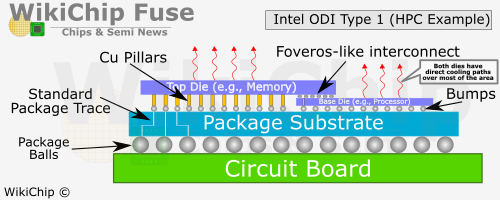

इसका मतलब यह है कि निष्क्रिय होने की स्थिति में यह केवल दोनों के बीच मिलन तक सीमित है, लेकिन यदि यह सक्रिय है, तो यह एक इंटरकनेक्ट डेटा ट्रांसमीटर के रूप में काम करता है, जो यदि आप जोड़ना चाहते हैं तो बहुत उपयोगी है HBM बाहरी कैश या एक के लिए ढेर iGPU । इसलिए और मानसिक योजना में वापस जाना, अगर ODI 1 के माध्यम से विभिन्न आकारों में से कई का उपयोग किया जाता है, तो उन सभी को बेहतर गर्मी लंपटता तक पहुंच की अनुमति है, जहां IHS को कुछ मामलों में विशिष्ट होना होगा, लेकिन एक पहुंच हासिल की है। इससे प्रत्यक्ष और इसलिए तापमान की समस्याएं हल हो जाती हैं।

यह महत्वपूर्ण है क्योंकि अगर हम दोनों की दृष्टि से मरते हैं, तो उनमें से केवल एक हिस्सा होगा जो जुड़ा होगा, एक आवश्यक, जबकि बाकी की मृत्यु स्वतंत्र है और प्रत्येक मामले में हवा में रहता है, बेशक दो अलग-अलग ऊंचाइयां और यह ठीक वही है जो इसे एक तकनीक के रूप में ईएमआईबी से अलग करता है।

यह उल्लेख नहीं करने के लिए कि दोनों के बीच के संघ को अन्य चीजों के बीच, थर्मल संपीड़न के साथ बनाया जाना है।

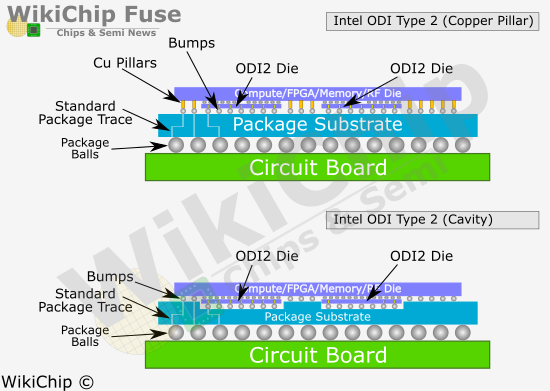

इंटेल ODI टाइप 2

यहां समस्या बढ़ जाती है, क्योंकि निचली मृत्यु हमेशा ऊपरी मृत्यु से नीचे होती है, अर्थात, मरने वाले का कोई भी हिस्सा नीचे नहीं होता है जो ऊपर है उस से फैलता है। यह गर्मी का नुकसान लाता है, लेकिन एक ही समय में इसका एक स्पष्ट लाभ होता है: ऊपरी डाई की तुलना में निचले डाई को ठीक उसी स्थान पर रखा जा सकता है जहां आवश्यक हो और कनेक्शन की संख्या बहुत अधिक हो सकती है।

यह तकनीक मरने के बीच प्रदर्शन और कनेक्शन की समस्याओं को दूर करने पर केंद्रित है, जहां बेहतर प्रदर्शन हमेशा अधिकतम होता है, जैसे बेहतर इनपुट और आउटपुट इंटरकनेक्ट, कैश में अधिक गति। आउटसोर्सिंग उन्हें दंड और अंतहीन के बिना। संभावनाओं का।

आप एक झेन 2-शैली I / O कर सकते थे, अलग-अलग मरने में कोर से बाहर निकलने वाले कैश को छोड़कर, प्रदर्शन को नुकसान के बिना तीन अलग-अलग स्तरों में और तीन अलग-अलग स्तरों में बना रहे क्योंकि वे टीएसवी के साथ शारीरिक यूनियनों के माध्यम से एक-दूसरे से सीधे जुड़े हुए हैं। इसके फायदे इतने स्पष्ट हैं कि उन पर टिप्पणी करना भी बेतुका है।

यहाँ समस्या तापमान है, लेकिन ओडीआई टाइप 2 के साथ क्या उद्देश्य है कि निचले हिस्से में सबसे कम ऊर्जा की खपत के साथ मरने को जगह दी जाए और ऊपरी स्तर पर अधिक गर्मी उत्पन्न करने वाले मर को रखने तक सक्षम किया जा सके। IHS के साथ प्रशीतित, जो वास्तव में कुछ अद्भुत देता है सी पी यू कॉन्फ़िगरेशन विकल्प और समावेशी दक्षता के लिए अलगाव को सक्षम करता है।

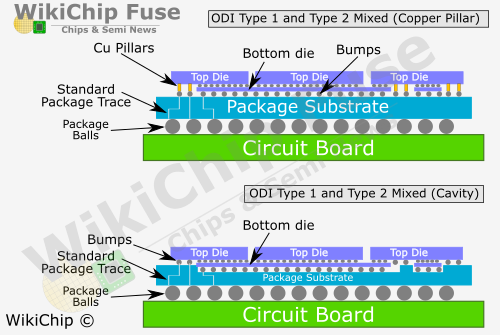

जैसा कि हमने कहा, ODI टाइप 1 और टाइप 2 के दो अलग-अलग संस्करण हैं: कॉपर पिलर और कैविटी , जहां पहले एक तांबे के खंभे का उपयोग अधिक ऊंचाई की क्षतिपूर्ति के लिए किया जाएगा, जबकि दूसरे में सब्सट्रेट को खंभे के बजाय धक्कों का उपयोग करने की अनुमति देने वाली निचली डाई में ढाला जाएगा।

Intel ODI अधिक जटिल CPU की पेशकश करने के लिए दोनों प्रकारों को मिला सकता है

एक तकनीक के रूप में ODI का एक और लाभ यह है कि यह अनन्य नहीं है, अर्थात दोनों प्रकारों का उपयोग एक ही CPU पर अपने दो संस्करणों के साथ किया जा सकता है। इसलिए प्रतिरूपकता हम भविष्य के सीपीयू में देखने में सक्षम होने जा रहे हैं, ऐसे कैलिबर का है कि इसके डिजाइन में जटिलता इंटेल के लिए मुख्य चुनौती होगी।

सबसे स्पष्ट सवाल एक ही समय में सबसे प्रासंगिक है: हम बाजार पर इन सीपीयू को कब देखेंगे? जवाब देने के लिए वास्तव में मुश्किल सवाल। ध्यान रखें कि एक तकनीक के रूप में ODI कुछ महीने पुराना है, यह वर्तमान में लागू किया जा रहा है और इसे प्रक्रिया को सरल बनाने के संदर्भ में सुधार करना है, लेकिन इंटेल ने अनुमानित तारीखों की पेशकश करने की हिम्मत की है: 2022 या 2023।

प्रौद्योगिकी के रूप में ODI समय सीमा को कम करने का प्रबंधन करेगा, क्योंकि यह तीन इंटेल प्रौद्योगिकियों की दो मुख्य समस्याओं को हल करता है, इसलिए पहले प्रोसेसर (उन्हें स्पष्ट रूप से डेस्कटॉप के लिए नहीं होना चाहिए) 2024 में उत्पादन में देखा जा सकता है, वास्तव में आशावादी होने के नाते चूंकि, जैसा कि अक्सर होता है, कम शक्तिशाली संस्करण पहले जारी किए जाते हैं और जब प्रक्रिया और उत्पादन दोनों को पॉलिश और बेहतर किया जाता है तो उच्च प्रदर्शन संस्करण पेश किया जाता है।

किसी भी मामले में, यह विज्ञान कथा नहीं है, यह एक वास्तविकता है, स्पष्ट है, जो पहले से ही बाजार पर है केबी लेक जी और स्ट्रैटिक्स 10 और जो निस्संदेह प्रोसेसर का भविष्य है, जो अपनी जटिलता के कारण द मल्टी डाई या एमसीएम की तुलना में बहुत बड़ी क्रांति है, यह निश्चित कदम है कि हम 2030 में वापस लिथोग्राफिक प्रक्रियाओं के साथ मिल रही दीवार को पलीता लगा पाएंगे और यह एक शक के बिना और अधिक जटिल प्रौद्योगिकियों के लिए पिछले कदम हो सकता है जो बाजार में वर्तमान में हमारे पास डायपर में हैं।