Il est pas un secret que AMD va tirer beaucoup de profit de sa technologie de cache vertical à l'avenir. Nous l'avons déjà vu dans les processeurs EPYC Milan-X pour les serveurs et dans le Ryzen 7 5800X3D pour les PC. Cependant, les plans pourraient aller plus loin et on pourrait parler d'un éventuel cache L4 et IA dans le futur AMD Ryzen.

La mémoire cache d'un processeur a une fonction claire, pour accélérer l'exécution des instructions. Cependant, cela peut ne pas être plus lent à récupérer les données que RAM. Ainsi, le point est atteint où l'ajout de niveaux de cache supplémentaires est contre-productif et ne conduit pas à de meilleures performances. La raison en est que les niveaux ne sont pas continus et qu'un accès supplémentaire doit être effectué pour chacun des niveaux jusqu'à atteindre la mémoire système.

Cependant, l'arrivée de la mémoire DDR5 et sa latence d'accès plus élevée ouvrent une fenêtre d'opportunité pour un niveau de plus dans la hiérarchie. Ce qui dans le cas des ordinateurs de bureau AMD Ryzen ne serait pas situé dans les chiplets CCD, mais bien plus loin. Plus précisément dans le contrôleur de mémoire intégré. Qu'est-ce qu'un cache L4 dans les processeurs AMD. EPYC, Threadripper et Ryzen.

Comment savons-nous que les futurs processeurs AMD auront un cache L4 ?

La réponse à la question est simple, ni plus ni moins qu'un brevet. Et c'est qu'AMD entend répondre à l'une des capacités qui Intel a en ce moment. Nous faisons référence aux unités XMX des Xeons basés sur Intel Core 12 et Sapphire Rapids. C'est-à-dire l'unité du type de tableau systolique ou de l'unité de tenseur pour calculer les tableaux. En d'autres termes : pour accélérer les algorithmes d'intelligence artificielle afin qu'ils s'exécutent plus facilement sur le processeur.

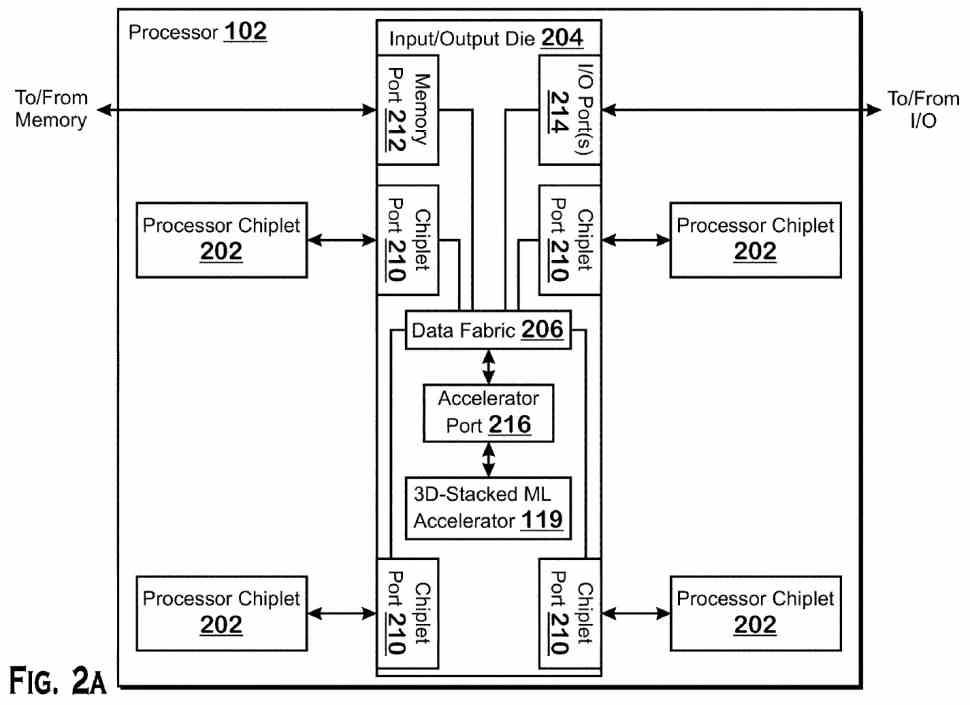

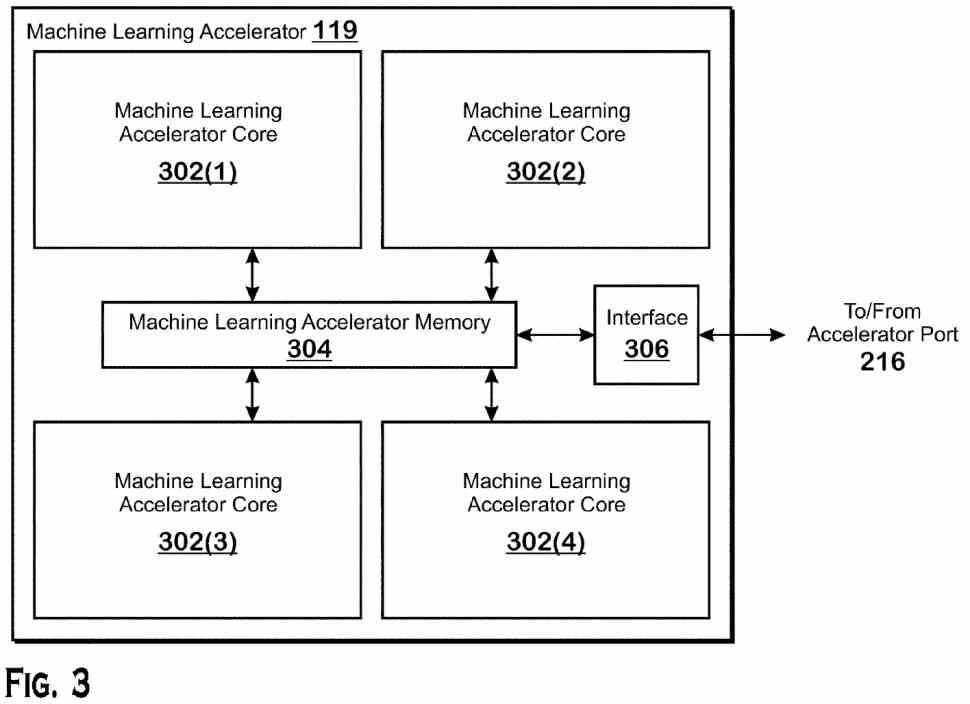

Pour ce faire, AMD a créé une nouvelle unité IOD, qui se distingue par le sacrifice de certains ports pour les différents processeurs en échange de l'intégration d'une unité pour accélérer les algorithmes de Machine Learning. Nous sommes donc confrontés à la réponse d'AMD à l'inclusion de l'unité XMX dans les derniers processeurs de son principal rival. La grâce de cela est qu'Intel a choisi que certains de ses Xeon Sapphire Rapids utilisent la mémoire HBM. Dans le cas d'AMD, la solution est plus simple. L'utilisation du même V-Cache en plus du processeur pour que l'IA accélère lesdits algorithmes . Bien que dans ce cas sous forme de cache L4 . Un niveau jusqu'alors inédit dans les processeurs à architecture Zen.

Pour le moment, c'est encore un brevet, mais cela risque d'entraîner une nouvelle Processeur variante . C'est en tout cas un marché auquel AMD s'est le moins intéressé. Bien que des rumeurs prétendent que ladite unité pourrait en fait être un FPGA embarqué ou eFPGA de Xilinx . À ce sujet, nous laisserons des doutes le moment venu.