Die Ankündigung des 2-nm-Prozesses durch IBM ist ein Beweis dafür, dass die Hardware für die nächsten 5 Jahre wie immer und kontinuierlich skalieren wird, aber diese Ankündigung erzeugt wiederum eine Reihe von Unbekannten seit der Anzahl von Nanometern für eine lange Zeit Zeit entspricht mehr dem Marketing als der physischen Realität.

Diese Woche wurde der neue IBM Manufacturing Node angekündigt. Was können wir von diesem Node erwarten und was wird der Sprung im Vergleich zu den Nodes sein, die derzeit für die Herstellung verschiedener Chips und Speicher verwendet werden?

Vergleich des 2nm-Knotens von IBM mit aktuellen

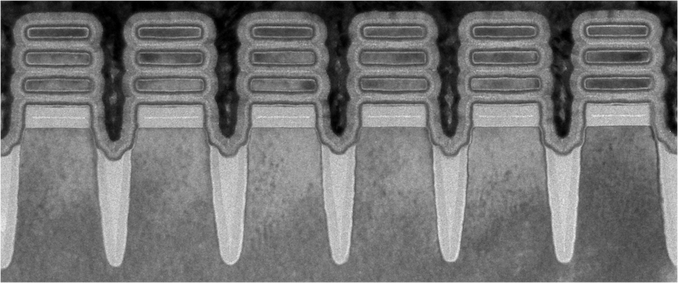

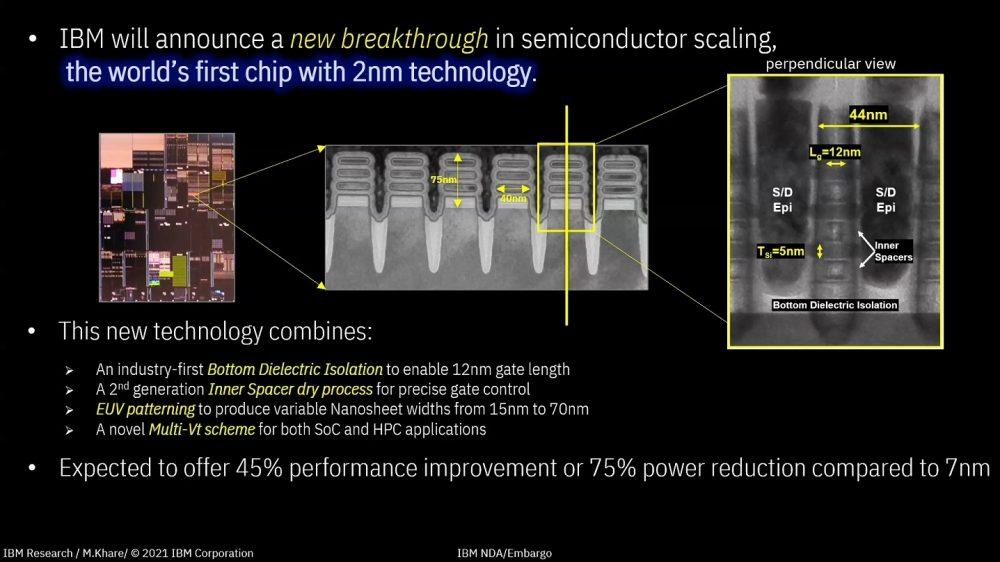

Der mit dem 2nm-Knoten von IBM hergestellte Musterchip hat eine Dichte von 333 Millionen Transistoren pro Quadratmillimeter. Denken Sie daran, dass die Dichte der Transistoren davon abhängt, was mit ihnen gebaut wird und dass der Speicher viel dichter ist als die Logik. Daher haben nicht alle Bereiche des von IBM in seinem experimentellen 2-nm-Knoten hergestellten Prozessors eine solche Dichte. In jedem Fall ist es in diesen Fällen normal, die Dichte aus dem, was der SRAM in jedem Knoten belegt, zu messen.

Die Nachricht ist wichtig angesichts einer Situation, in der das Mooresche Gesetz immer langsamer zu werden scheint und mit dem allgemeinen Gefühl, dass ein Knoten erreicht wird, der es in Bezug auf Entwicklungskosten, Bereitstellung oder physische Einschränkungen nicht zulässt, dass die Chips weiter skaliert werden. .

In Wirklichkeit stehen wir vor einem Knoten, also sollten wir zumindest auf 2024 oder 2025 warten, was die Markteinführung betrifft.

Sind die wirklich 2nm?

Die 7-nm-Knotendichte von TSMC beträgt 96.5 Millionen Transistoren pro Quadratmillimeter. Dabei ist zu berücksichtigen, dass die Dichte der Transistoren mit abnehmender Größe quadratisch zunimmt. Um beispielsweise die Dichte eines Knotens zu verdoppeln, müssen wir nur die Größe mit 0.7 multiplizieren. Wenn wir beispielsweise den 7-nm-Knoten nehmen, müssen wir diese Größe nur mit 0.7 multiplizieren, was uns einen 4.9-5-nm-Knoten ergibt.

Aber betrachten wir wirklich einen 2-nm-Knoten? Um die Dichte eines hypothetischen zukünftigen Knotens zu kennen, müssen wir nur die folgende Berechnung durchführen:

Skalierungsfaktor des zu konvertierenden Knotens = (1 / bekannter Knoten) ^ 2

Dann müssen wir nur noch Folgendes tun:

Transistordichte des neuen Knotens = Transistordichte des bekannten Knotens / Skalierungsfaktor des Knotens, auf den umgerechnet werden soll.

Mit der ersten Formel erhalten wir einen Skalierungsfaktor von 0.08, was darauf hindeutet, dass ein hypothetischer „echter“ 2 nm Knoten eine Dichte von fast 1200 Millionen Transistoren pro Quadratmillimeter hätte. Fast viermal mehr als das von IBM angekündigte, aber es muss auch hinzugefügt werden, dass die 7 nm von TSMC nicht wirklich genau 7 nm sind, sondern eine viel geringere Dichte und damit ein viel höherer Knoten in realen Nanometern.

Wie schneidet es im Vergleich zu den anderen vorhandenen Knoten ab?

Der Grund, warum er als 2-nm-Knoten bezeichnet wird, liegt darin, dass seine Dichte höher ist als die der von beworbenen 3-nm-Knoten Samsung und TSMC. Im Fall von Samsung beträgt die beworbene Dichte für seinen 3nm-Knoten 180 Millionen pro Quadratmillimeter, während der 3nm-Prozess von TSMC eine beworbene Dichte von 315 Millionen hat.

Der Grund, warum IBM seinen Knoten „2nm“ nennt, liegt einfach darin, dass seine Spezifikationen denen von TSMC und Samsung weit überlegen sind. Jetzt werden wir die Argumente dafür sehen.

IBM 2-nm-Knotengeschwindigkeit und Stromverbrauch

Ein weiterer wichtiger Punkt ist, wie Prozessoren in Geschwindigkeit und Verbrauch skalieren, dh wenn wir einen vorhandenen Chip unter dem neuen Knoten herstellen. Wie schnell würde es ankommen oder wie würde der Verbrauch reduziert? Beides gleichzeitig kann nicht sein, daher werden die beiden Zahlen getrennt angegeben.

Ein Prozessor, der unter dem 7-nm-Knoten von TSMC, unter dem 2-nm-Knoten von IBM hergestellt wurde, würde bei gleichem Verbrauch 45% schneller in der Taktrate sein. Würden wir die Taktrate beibehalten, würde der Energieverbrauch auf 75% sinken.

Die Taktrate hat jedoch einen Trick, da immer genau der Punkt der höchsten Spannungs- und Taktkurve gesucht wird. Das gleiche gilt für den Verbraucherknoten, wo es scheint, dass IBM einen besseren Knoten aus der Perspektive des Energieverbrauchs erhalten hat.

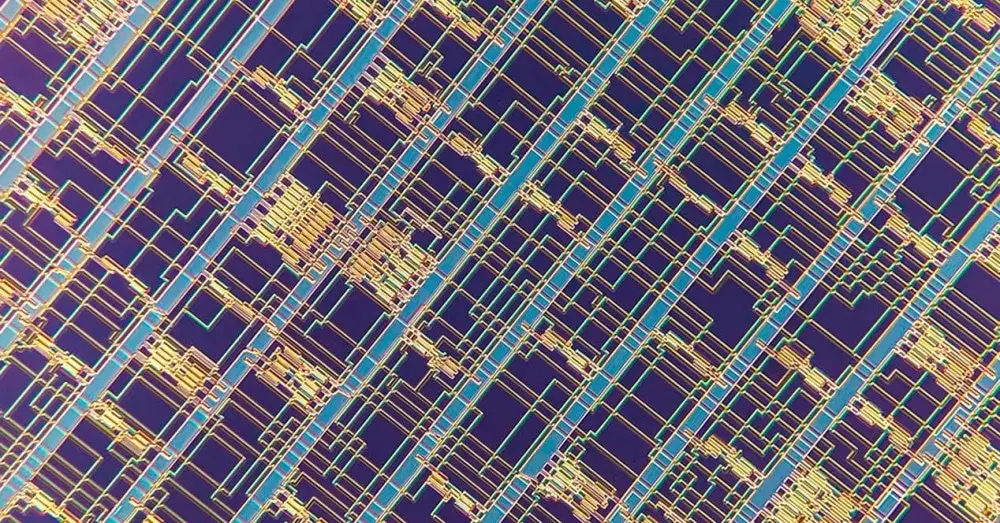

In der höchsten Energieeffizienz hat der IBM 2 nm-Knoten seinen Namen erhalten, und dies liegt an der Verwendung von sogenannten HNS oder Horizontal Nanosheets, einer Technologie, die Intel wird in seinem 5-nm-Knoten verwendet, der von Ihrem bis zu Ihrem Gesicht mit den 3-nm-Knoten von Samsung und TSMC konkurriert. Wir wissen, dass Samsung sie in Zukunft übernehmen wird, aber wir wissen nicht, ob TSMC dies tun oder sich für eine andere Lösung entscheiden wird.

Das Joint Venture zwischen IBM und Intel

Ja, diese Aussage mag Ihnen sehr schockierend erscheinen, aber wir müssen bedenken, dass IBM im Gegensatz zu Intel keine eigenen Foundries hat, sondern Chips entwirft und vor allem viel in das Design neuer Chipfertigungen investiert Knoten, die es an Dritte lizenziert. Es handelt sich also um ein anderes Geschäftsmodell als bei TSMC, Samsung und Intel.

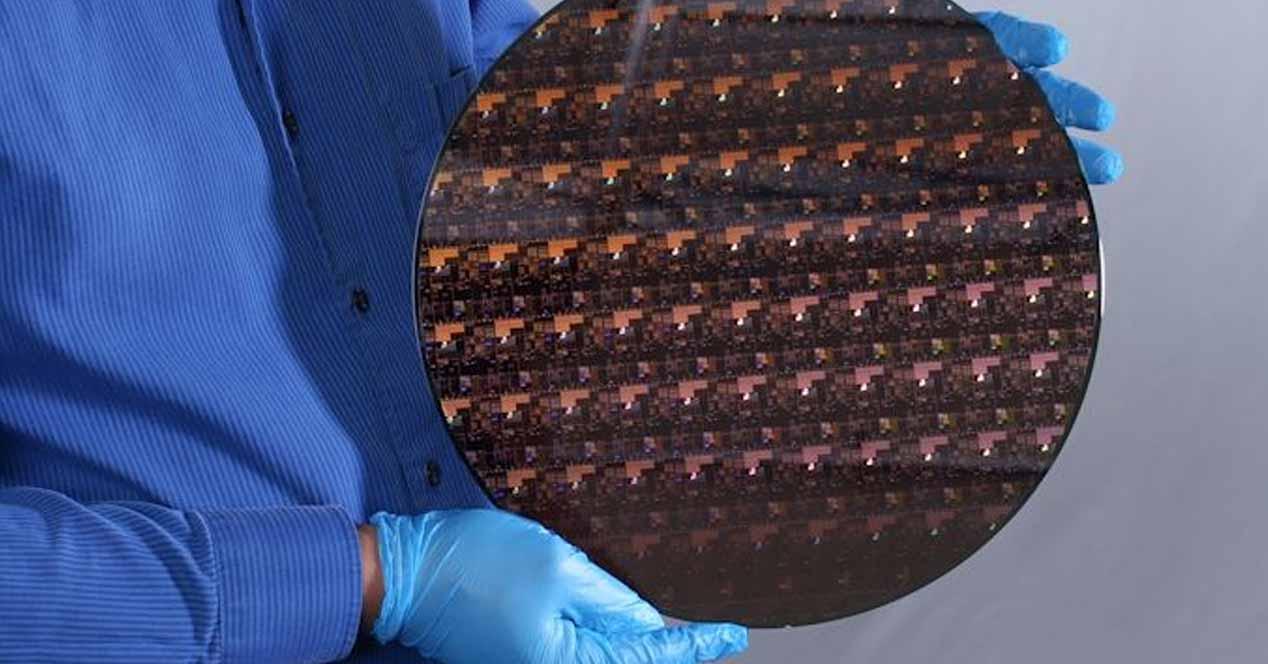

Das heißt, was IBM getan hat, ist, die Standards für einen neuen Fertigungsknoten zu entwerfen und dann einen Musterchip zu erstellen, der ein Design ist, das alle gemeinsamen Elemente des Designs eines zeitgenössischen Prozessors vereint und mit Hilfe von . neu erstellt wurde eine experimentelle Version seines 2-nm-Knotens.

IBM hat routinemäßig mit GLOBAL FOUNDRIES zusammengearbeitet, aber sie schieden komplett aus und kamen nicht in 7nm. Der IBM-Partner in diesem Fall ist also Intel, und wir sehen uns möglicherweise die Spezifikationen eines zukünftigen lntel-Knotens an.

Darüber hinaus ist es möglich, dass wir uns den Spezifikationen des 5-nm-Knotens von Intel gegenübersehen, mit denen sie den zuvor in diesem Artikel besprochenen 3-nm-Knoten von TSMC und Samsung standhalten würden.