RAM hukommelse har været i alle computere siden 70'erne, mens det er sket i al den tid, vi har set, hvordan komponenter er opstået og forsvundet. Nogle på grund af ubrug, andre fordi de er integreret i andre. Men ved siden af processoren er den der stadig. Men hvad nu hvis vi integrerede RAM inde i processoren og fik det til at forsvinde? Er dette muligt at gøre? Vi forklarer det for dig.

Tendensen inden for hardware er, at bundkort bliver enklere sammenlignet med, hvad de var for et par år siden. I et par år nu har folk talt om visse teknologier, der ville tillade RAM og CPU at smelte sammen til den samme enhed. Vil vi se det i fremtiden, eller er der i stedet begrænsninger for det?

Er det muligt at integrere RAM inde i processoren?

Et af koncepterne vedrørende processorers ydeevne er, at jo tættere hukommelsen er på de enheder, der udfører instruktionerne, jo bedre ydeevne, da det tager kortere tid at løse instruktionen. Grunden? Enkelt, det elektriske signal har mindre afstand at rejse. Så det ideelle ville være, at processor og hukommelse var på samme chip.

Vi befinder os dog med, at der er RAM-hukommelse, som er den støttehukommelse, som hver processor bruger til at udføre programmer. Hvilket, som du allerede ved, er uden for chippen og derfor ikke giver den ideelle ydeevne. Som om det ikke var nok, øger denne afstand energiforbruget ved overførsel af data.

I betragtning af at RAM-hukommelse er en grundlæggende del af enhver arkitektur, og vi ikke kan slette den, har vi spekuleret på, hvad der ville ske, hvis vi fjernede denne komponent. Altså hvis vi integrerede det i processoren. Under alle omstændigheder findes der allerede chips af denne type, da mikrocontrollere har netop den hukommelse, som de arbejder med inde i chippen, men dens funktion er meget begrænset.

Fordele ved at integrere RAM inde i processoren

Først og fremmest skal vi tale om fordelene ved at integrere RAM i processoren. Vi sætter det på betinget, fordi vi ikke kommer til at tage højde for de tekniske begrænsninger, der forhindrer producenter i at gøre det indtil videre. Som vi kommer ind på senere. Så for øjeblikket vil vi begrænse os til, hvad konceptet ville være i teorien, og hvilke fordele det ville bringe med sig.

BMI ville forsvinde

Den integrerede hukommelsescontroller ville ende med at forsvinde, da den er ansvarlig for at administrere adgangene med den eksterne hukommelse, og dens plads vil derfor blive optaget af RAM-hukommelsen inde i processoren. På samme måde ville hele den del af periferien, som er grænsefladen for at kommunikere med systemets hukommelse eksternt, også ophøre med at eksistere, da nævnte hukommelse ikke eksisterer i teorien.

Processorens ydeevne vil stige

Det er klart, at ved fuldstændig at reducere adgangstiden til dataene og instruktionerne, vil alle af dem blive eksekveret på kortere tid, og naturligvis måles ydeevnen af disse ved antallet af instruktioner, der kan udføres på en given tid. Hvorfor? Tja, på grund af det faktum, at dette udmønter sig i at udføre programmerne hurtigere eller, hvis det ikke sker, at være i stand til at administrere flere af dem på samme tid.

Forbruget ville falde

At overføre en smule data i processoren har i øjeblikket en energiomkostning på 0.1 pJ/bit, at gøre det til DDR5 koster 7 pJ/bit, det vil sige, at energiforbruget vil blive reduceret op til 70 gange. hvad angår datakommunikation.

Cachen ville ikke forsvinde

Cachens opgave er at have en midlertidig kopi af informationen i RAM, men inde i chippen, så det tager kortere tid at komme til den. Hvis vi lagde random access-hukommelsen inde i chippen, så ville vi opdage, at vi ville komme til den med mindre latenstid, og dermed ville højere cache-niveauer blive unødvendige. Så i teorien ville vi indlæse cache-værktøjet. Dette er dog ikke helt tilfældet, og vi vil støde på et problem.

I betragtning af at cacherne har den anden nytte til at reducere blokeringer i hukommelsesadgange ved at have lokale kopier i hver kerne på de laveste niveauer af samme, hvis der ikke var nogen cache, ville vi have et overbelastningsproblem i databussen på grund af det enorme antal anmodninger, der ville være. Det vil sige, at have en hukommelsespulje til alle processorer og uden en lokal backup belastes ydeevnen af overskydende adgang.

Så vi ville ende med at have mindst ét niveau af cache, det første niveau, som normalt er opdelt i data og instruktioner og er det med mindst latens. Det ville være muligt at tilføje et mellemliggende cache-niveau, der allerede er delt mellem flere kerner, men designere skulle sørge for, at dets latens var lavere end processorens integrerede RAM.

Så hvorfor gøres det ikke?

Hvis du undrer dig over, hvorfor vi har forklaret cachehukommelsen for dig, er det fordi en af årsagerne er manglen på plads på chippen. Når man fremstiller en processor, som du allerede ved, skal den, der ønsker at sælge den, tage højde for, hvor mange wafere der er tilgængelige, hvor mange processorer pr. wafer og til hvilken pris. Tag en DIMM eller SO-DIMM med RAM-hukommelse og se på alle chipsene der, tror du, det ville passe inde i processoren? Nej det kan ikke lade sig gøre.

Det er grunden til, at metoderne til fremstilling af RAM-hukommelse og processorer har været forskellige over tid, til det punkt, hvor støberier som TSMC, der har specialiseret sig i processorer, i dag ikke skiller sig ud, når det kommer til at fremstille hukommelser og processorer. omvendt. Det er meget svært at se en proces, der gør det muligt at kombinere begge typer chips på samme tid, medmindre der er en chip under udvikling til samme, som økonomisk berettiger det, hvilket er sjældent at se i hjemmesystemer.

Alternativer til RAM i processoren

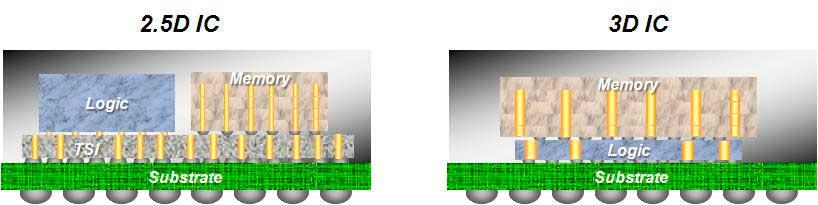

Alternativerne er intet andet end at bruge de nye metoder til at bygge integrerede kredsløb baseret på vias gennem silicium, enten ved at placere processoren side om side med RAM og begge monteret i en interposer, som er kendt som 2.5DIC, og som vi allerede har set. i systemer med HBM-hukommelse. Den anden løsning er at stable RAM-chips oven på processoren eller 3DIC. Problemet? De ekstra omkostninger ved disse metoder er så høje, at de ikke er levedygtige for hjemmemarkedet, selvom den hukommelse, der tilbydes i begge tilfælde, har lavere latenstid og forbrug end konventionel RAM.

På markedet for serverprocessorer vil vi snart se konfigurationer med HBM-hukommelse, problemet er, at de er faste størrelsesmæssigt, og hvis der er behov for en større mængde RAM, vil det være nødvendigt at smide konventionelle RDIMM-sokler ud. Hvilket fuldstændig ødelægger integration af RAM i processoren for at spare os for at skulle implementere det i systemet. Disse løsninger giver i hvert fald ikke en lavere latens eller forbrug i forhold til dataadgang end en komplet integration af RAM'en i processoren, da vi egentlig ikke gør det, men bringer RAM'en tættere på.