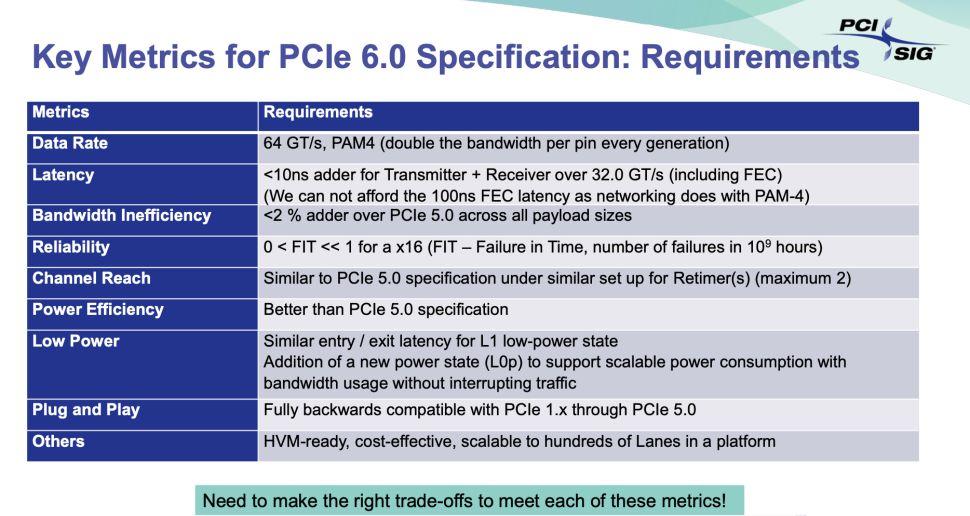

- PCIe 6.0 规范在其初稿中就已经存在于我们之中,因此,有许多新功能,我们已经在有关该总线新版本的文章中进行了介绍。 但是与其他产品不同的是,必须包含一项功能,这将标志着主板的未来以及它们从5.0版过渡到此新6.0的原因,因为尽管后者兼容,但第一个将不兼容。这归功于一个叫做 前向纠错或FEC .

为什么新标准很难开发? 为什么从5.0版本开始花了这么长时间,却花了这么少的时间呢? 好吧,这些改进远不止是广泛的,因为我们当前使用的是PCIe 4.0,并且我们正在谈论将其速度在x16线的相同宽度上提高三倍。 从逻辑上讲,PCI-SIG必须实施一系列改进以保证数据传输,包括PAM 4和FEC,但是后者是什么?它如何在这种特定总线上工作?

前向纠错或FEC,PCIe 6.0的必要技术

尽管我们已经说过有关PAM 4的内容,但没有它,就无法理解FEC。 PAM 4进入网络工程师已有数年了,在大型数据中心中,PAM XNUMX是保存基础架构或更新基础架构以及其他技术的圣杯。

但是它并没有止步于此,因为它已被引入PCIe总线中,这显然是由于调制波的原因,当然,对于每个可用的Hz,它都具有更大的带宽。 即使具有其优点,它也具有必须减轻的缺点,例如其信号更加脆弱,因此并且是其实施的真正原因,PCI-SIG包括了所谓的 前向纠错或FEC .

顾名思义,FEC只是纠正不同链路或主机之间信号发送和接收中的错误的一种手段,它设法提供包括纠错在内的恒定数据流。

它所实现的是,它从对数据完整性而言至关重要的信号变为没有错误的稳定信号,从而保证了设备及其组件的正确运行。

该技术的问题在于其高延迟

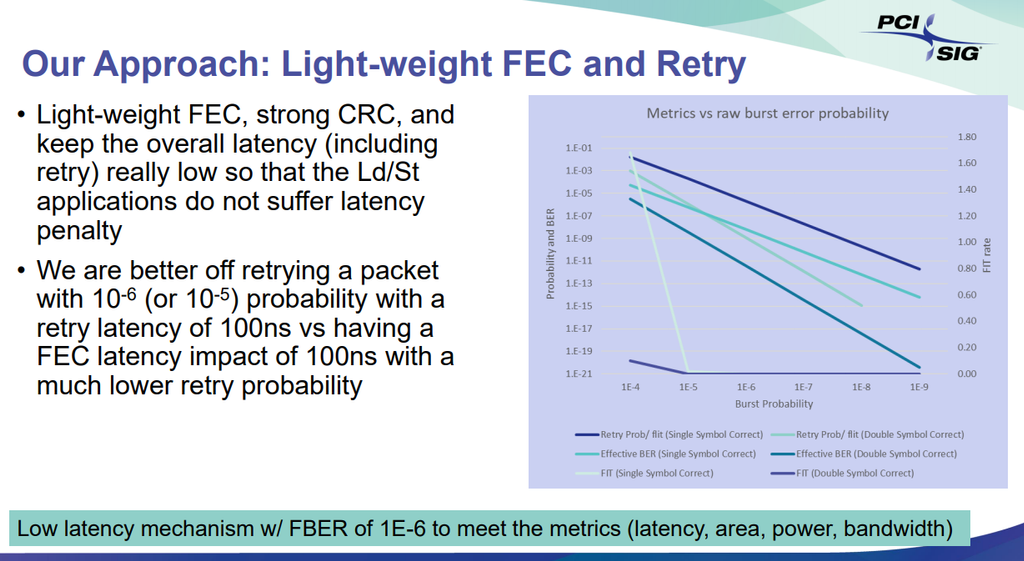

但是,并不是所有闪闪发光的都是黄金。 FEC本身及其纠正以最纯净的CRC样式发现的错误的性质不适合用于PCIe等总线,而其版本6.0的128 Gb / s则不适用,根本不是。

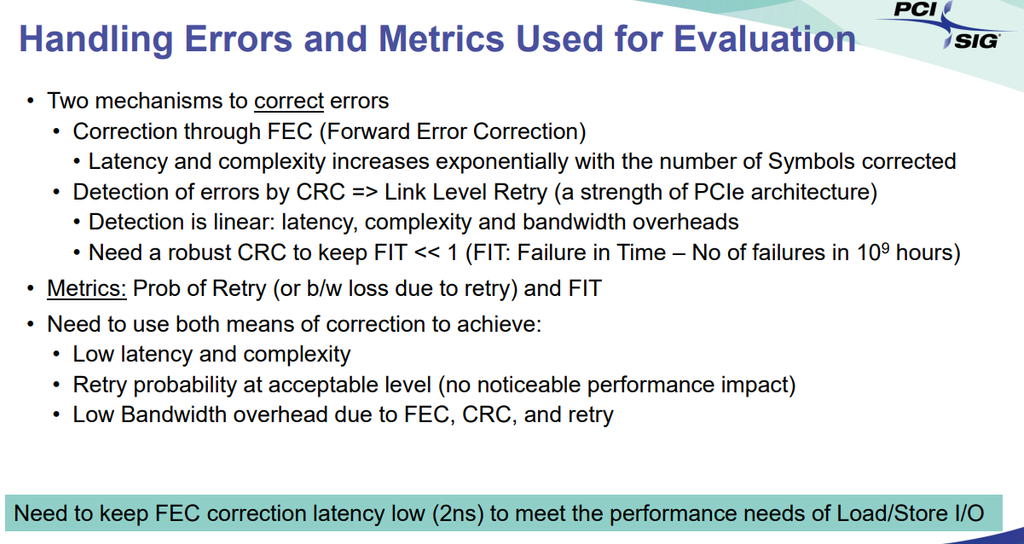

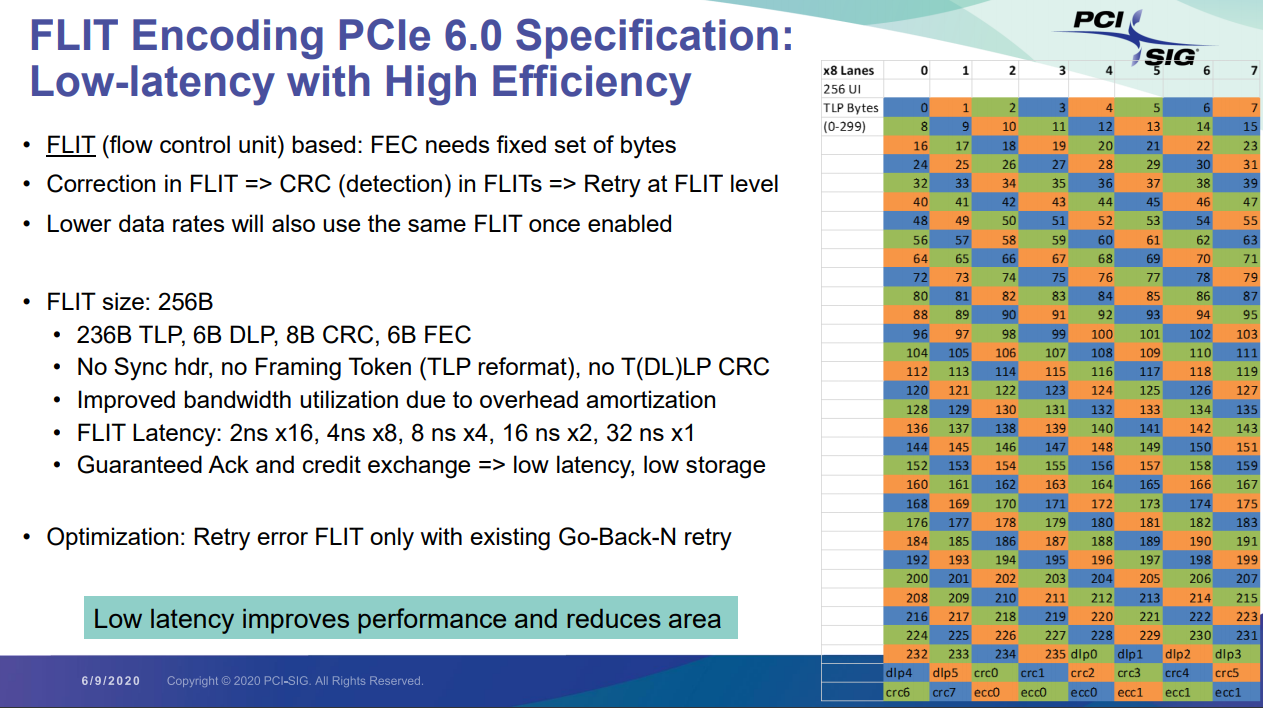

FEC的问题在于它给总线引入了延迟,因此降低了数据包的传输速率并可能产生不必要的延迟。 因此,PCIe 6.0技术使用独特的方法通过结合第一位误码率(FBER为10 -6) 结合轻量级,低延迟的FEC来完成初始修复。

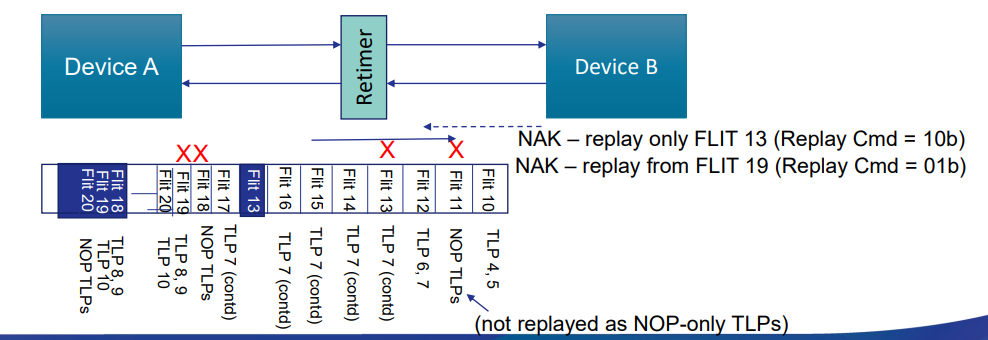

但是可以,FEC可以纠正错误,但是为此,它必须知道错误的确切位置和大小才能做出相应的选择。 为什么? 非常简单,目标是支付接近零的延迟损失(不可能为零),然后依靠非常强大的CRC进行检测,并结合快速的链路级重播来处理FEC无法纠正的任何错误(这是并非绝对可靠,因此需要CRC)。

另一方面,如果速度从 128 Gb /秒 在PCIe 6.0中,可能会绕过FEC,这会降低系统延迟。

如果FEC无法纠正错误,该怎么办? 好了,现在该是CRC进入生成NAK的时候了,但它将触发等待时间来回检查数据,直到100 ns。

显然,FEC的使用是合理的,不是完美的方法,但是它是产生具有纠错功能的最小延迟的最佳方法,这对于从数据传递中获取数据这样的微妙操作是完全必要的。 中央处理器,记忆和 GPU.