Om du har följt världen av mikroprocessorer ganska länge är det säkraste att du kommer att känna till förkortningarna RISC och CISC, som inte är något annat än en definition av strukturen för den uppsättning instruktioner som en processor hanterar. Nåväl, på senare år har ett nytt paradigm dykt upp som har döpts till VISC. Vad består den av?

De flesta av processorerna på marknaden har blivit tråkiga, eftersom de ger lite på bordet. De bygger på att förbättra prestandan genom att justera små delar så att helheten fungerar bättre än tidigare, men de senaste åren har det inte skett en revolution som den som inträffade med utförandet i oordning i mitten av 90-talet, dock kan detta ändras tack vare VISC-arkitekturer, som representerar ett nytt paradigm.

Är VISC en uppsättning instruktioner?

Det första som kan komma att tänka på när man läser dessa förkortningar och på grund av deras likhet är orden RISC och CISC, som hänvisar till arten av uppsättningen av register och instruktioner från processorn, vilket inte är föremål för denna artikel, eftersom under VISC-konceptet syftar vi inte på ett nytt sätt att kategorisera instruktioner, utan till något helt annat.

För att förstå hur VISC-paradigmet fungerar måste vi ta hänsyn till två olika begrepp ang CPU prestanda. Den första av dessa är det faktum att PC-processorer idag har en intern instruktionsuppsättning som är ännu mindre än RISC, eftersom vad de gör är att överföra var och en av instruktionerna i mindre mikroinstruktioner internt under processen. avkodningsfas. Om vi är purister så är slutsatsen idag att alla processorer inte är att de är RISC, utan att de har en mycket reducerad uppsättning instruktioner som fungerar internt och som tjänar till att bygga resten av instruktionerna. Det vill säga, så snart en instruktion når CPU-styrenheten bryts den ner i en lista med instruktioner.

Så kriget mellan RISC och CISC vann den förstnämnda, men med fällan som x86, den mest använda CISC-arkitekturen, gjorde fällan att bete sig internt som en RISC. Till denna dag, förutom ARM, resten av ISA RISC saknas eller är på väg att försvinna. Dessutom har till och med ARM anammat konceptet att dela upp instruktionerna i enklare, så båda paradigmen utanför definitionen av den gemensamma ISA för en familj är redan utdöda.

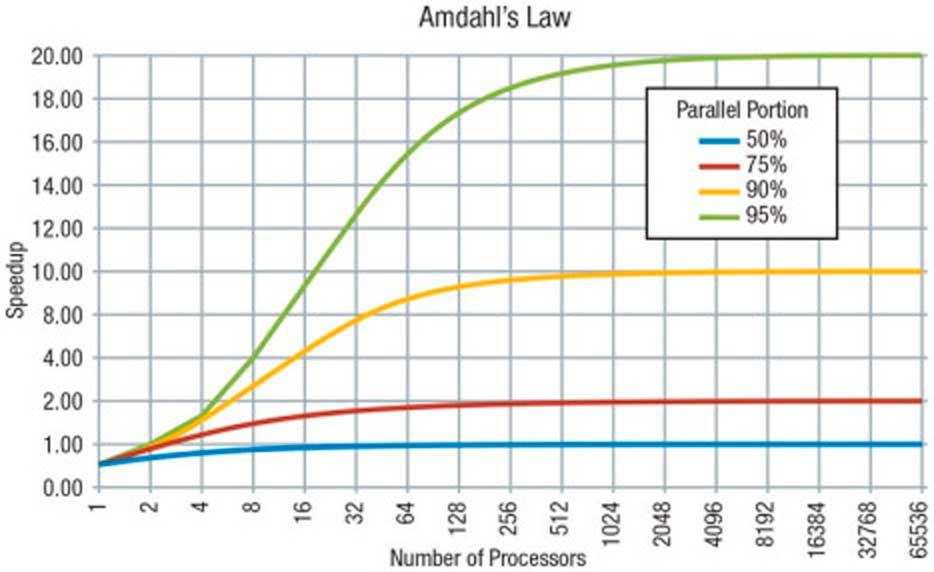

Amdahls lag

För att förstå ett program måste vi förstå att ett program har två olika delar:

- Den som bara kan köras i serie och därför bara kan lösas av en enda kärna genom att köra en solo-exekveringskärna.

- Den delen av koden som kan exekveras parallellt, vilket innebär att den kan lösas av flera kärnor samtidigt och ju fler av dem det finns i processorn, desto snabbare kommer denna del att lösas.

Om vi tar hänsyn till det som förklarades i föregående avsnitt kommer du att dra slutsatsen att några av processorinstruktionerna som blir mikrokod vad de gör blir en följd av instruktioner som kan arbeta i serie eller parallellt mellan flera kärnor, även om det vanliga är att de flesta instruktionerna exekveras i en enda kärna och att det är av delade element som koden exekveras parallellt.

Därför beror det faktum att en del av koden exekveras av flera kärnor uteslutande på programutvecklaren, som explicit måste programmera den så att vissa delar fungerar parallellt.

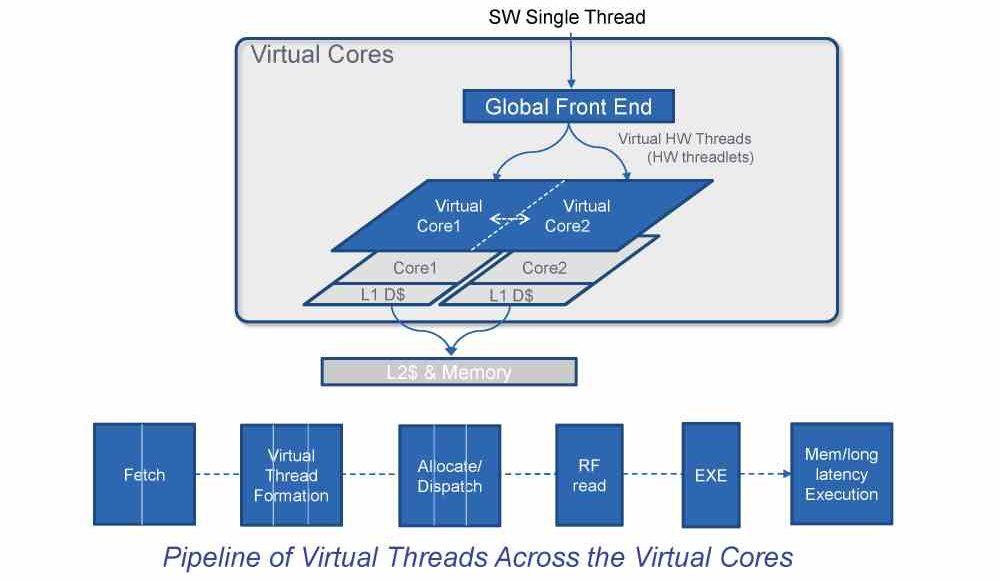

VISC och virtuella kärnor

När vi har förklarat allt ovan kan vi förklara vad akronymen VISC betyder, vars definition är det direkta svaret på följande fråga: Kan de inte fungera när mikroinstruktionerna genereras i avkodningsstadiet? parallellt med flera kärnor istället för att göra det i en enda dito?

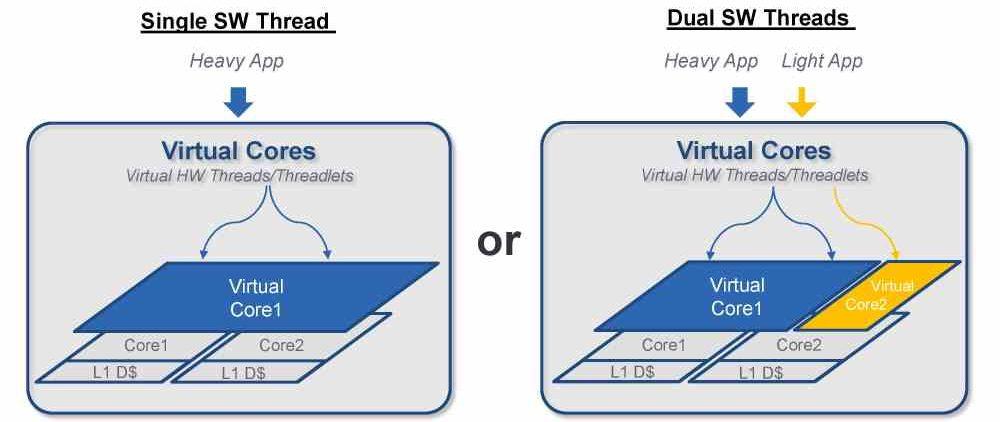

Tja, svaret på frågan om VISC-arkitekturen, som först togs upp av ett företag som heter Soft Machines 2015 som ett koncept för att förbättra CPU-prestanda. Denna lilla startup köptes av Intel 2016 och de har arbetat med att utveckla en VISC-arkitektur sedan dess. Hur fungerar det? Jo, det kan definieras väldigt enkelt: en enda exekveringstråd skickas till processorns Global Front End, som omvandlas till flera som utför samma funktion och som arbetar parallellt och körs i virtuella kärnor. Konverteringsprocessen exekveras på mjukvarunivå genom ett översättningslager, men vi måste komma ihåg att detta kan vara något så enkelt som en mikrokontroller som utför överföringen av instruktionerna.

I motsats till vad som händer i distributionen av uppgifter i en konventionell flerkärnig processor, är det i en VISC-arkitektur inte avsett att en kärna är fri att exekvera en instruktion, utan att elementen för att exekvera den är tillgängliga inom processorn för att exekvera den. Till exempel kan det hända att vektorenheten inte används i en konventionell kärna, men under detta paradigm kan den användas för att bilda en av instruktionerna.

VISC och prestanda

När man antar ett nytt paradigm i termer av arkitektur är det första man bör tänka på hur det påverkar prestanda, eftersom det inte är värt att ändra det nuvarande paradigmet om det inte leder till en ökning av den totala processorprestanda. Det mest klassiska sättet att öka prestandan hos en processor är att öka antalet instruktioner som löses per klockcykel, detta innebär att göra hårdvaran allt mer komplex, på grund av det faktum att tillägget av kärnorna måste vi räkna all infrastruktur som omger dem som blir samma eller mer komplexa.

Det som skiljer VISC från resten är ingen mindre än att fördelningen av processorresurser för exekvering av de olika instruktionerna utförs i några klockcykler, mellan 1 och 4 kärnor. På detta sätt, om det finns två instruktioner som konkurrerar om andra resurser i en kärna, kan de omfördelas mycket snabbt till en annan del av processorn där samma resurser finns tillgängliga.

Det nuvarande paradigmet, som är exekveringen i oordning, vad det gör är att ordna om exekveringen av instruktionerna enligt de fria resurserna vid alla tillfällen och sedan omordna utmatningen av redan bearbetade data. Begränsningen? Resursallokering utförs på enkelkärnig snarare än multikärnnivå, och detta är nyckeln till högre prestanda för VISC-arkitekturer.

Finns dessa processorer idag?

Även om konceptet är mycket bra på pappret har ingen ännu presenterat en processor som fungerar under detta paradigm, men med tanke på att vi gradvis närmar oss gränserna för det nuvarande paradigmet är det viktigt att ha i åtanke att det finns lösningar som kan tjäna för att förbättra CPU-prestandan på våra datorer för framtiden.

Att ha en kraftfullare processor är inte bara att ha en snabbare eller med fler kärnor, utan det bygger på att veta hur man drar fördel av tillgängliga resurser. Utförandet i oordning var det första steget i den meningen, men sedan dess, förutom att gå till multicore, har förändringarna i allmänhet varit små. VISC är fortfarande ett koncept, men det är inte omöjligt och det är ett sätt att dra nytta av de resurser som finns i processorn på ett mycket mer effektivt sätt.

Än så länge vet vi att konceptet är möjligt i en CPU eftersom Soft Machines designade och byggde en med detta paradigm, så även om det var på en experimentell nivå vet vi att det är möjligt att genomföra en sådan design. En annan sak är svårigheten att ta med hela uppsättningen x86-instruktioner och register till detta paradigm, som är extremt komplext till sin natur.