När det gäller att mäta prestanda för RAM och VRAM, vi brukar prata om två prestandaparametrar, som är bandbredd och latens. Men vad är förhållandet mellan dessa två egenskaper och kan vi klassificera dem som konstanta?

Ett av problemen med tekniska specifikationer är att de tenderar att ge data som körs med 100% prestanda under perfekta förhållanden. När det gäller minne händer detta inte, eftersom inte alla data har samma latens och bandbredden aldrig är 100%.

Mer bandbredd betyder inte mindre latens

Vi förstår som latens mellan en bearbetningsenhet och dess tillhörande minne, den tid det tar att ta emot en begärd information eller att ta emot signalen att en ändring har gjorts i minnet. Så latens är verkligen ett sätt att mäta tid.

Bandbredden är istället mängden data som överförs i varje sekund, så det är en hastighet. Så genom direkt logik kan vi komma att tänka att vid högre hastighet när vi letar efter data, då på kortare tid CPU, GPU eller någon annan bearbetningsenhet kommer att få informationen.

Verkligheten är att detta inte är fallet, dessutom finns det den särdrag att ju mer bandbredd ett minne har, då har det vanligtvis mer latens jämfört med andra. Detta fenomen har en förklaring, vilket är vad vi ska förklara för dig i följande avsnitt i den här artikeln.

Att söka efter data lägger till latens

Nästan alla bearbetningsenheter idag har en hierarki av cachar, där processorn frågar var och en av dem först innan de får åtkomst till RAM. Detta beror på att den direkta latensen mellan processor och RAM är tillräckligt stor för att resultera i förlust av prestanda jämfört med den perfekta processorn.

Tänk dig att du letar efter en specifik produkt, det första du gör är att titta i den lokala butiken, sedan i en något större butik och slutligen i ett varuhus. besöket till varje anläggning görs inte omedelbart utan kräver restid. Samma sak händer i cachehierarkin, detta kallas en "cache miss" så att vi kan sammanfatta tiden enligt följande:

Söktid = Sök tid i första cache + cachemissperiod + ... söktid i sista cache.

Om cache-uppslagstiden är längre än den tid det tar att gå till huvud-RAM, kommer cachesystemet att vara dåligt utformat på en processor eftersom det trotsar syftet för vilket cachen skulle ha skapats.

Nu är latensproblemet mer komplicerat, eftersom vi måste lägga till den latens som läggs till för att söka efter data i RAM om den inte finns i RAM till åtkomsttiden som läggs till av cachesökningen. Vilka problem kan vi hitta? Tja, till exempel är alla minneskanaler upptagna och konflikt skapas, vilket inträffar när RAM har upptaget minneskanaler och tar emot eller levererar annan data.

Hur påverkar latens bandbredd?

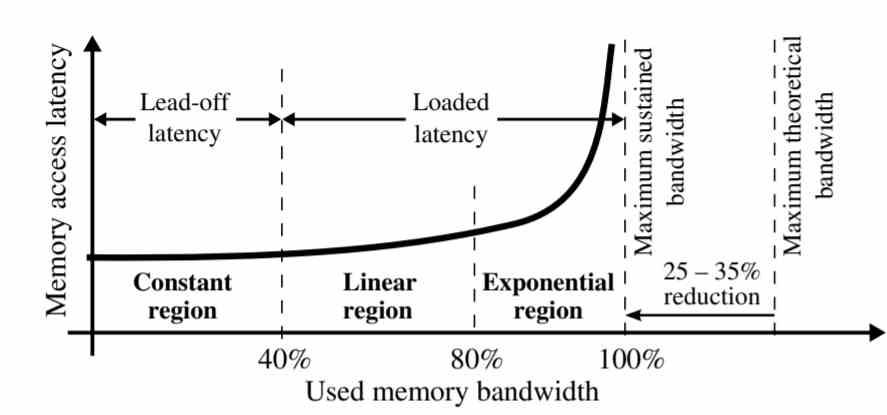

Som framgår av grafen är latens inte densamma för all minnesbandbredd.

- Konstant region: Latency förblir konstant vid 40% av den ihållande bandbredden.

- Linjär region: Mellan 40 och 80% av den ihållande bandbredden ökar latensen linjärt. Detta beror på att det finns en övermättnad av minnesförfrågningar som har ackumulerats i slutet på grund av strid.

- Exponentiell region: Under de senaste 20% av bandbreddssektionen växer datalatens exponentiellt, alla minnesförfrågningar som inte kunde lösas under den föregående perioden ackumuleras i denna del och skapar stridigheter mellan dem.

Detta fenomen har en mycket enkel förklaring, de första förfrågningarna till minnet som besvaras är de som hittas först, de flesta är i cachen när den har en kopia, men de som inte finns i cachen ackumuleras. En av skillnaderna mellan cacheminnen och RAM är att den förra kan stödja flera samtidiga åtkomster, men när sökningen efter data sker i RAM är latensen mycket högre.

Vi brukar föreställa oss RAM som ett slags ström av vatten där data inte slutar cirkulera med den specificerade hastigheten, när RAM inte riktigt kommer att flytta data såvida det inte har en begäran om det. Med andra ord påverkar latens genomströmning och därmed bandbredd.

Sätt att minska latens

När vi väl vet att strid om tillgång till data skapar latens och detta påverkar bandbredd, måste vi tänka på lösningar. Det tydligaste av det är faktumet att öka antalet minneskanaler med RAM, just detta är en av tangenterna med vilka HBM-minne har lägre åtkomstlatens än GDDR6, eftersom 8 minneskanaler tillåter mindre strid än med 2 kanaler med GDDR6.

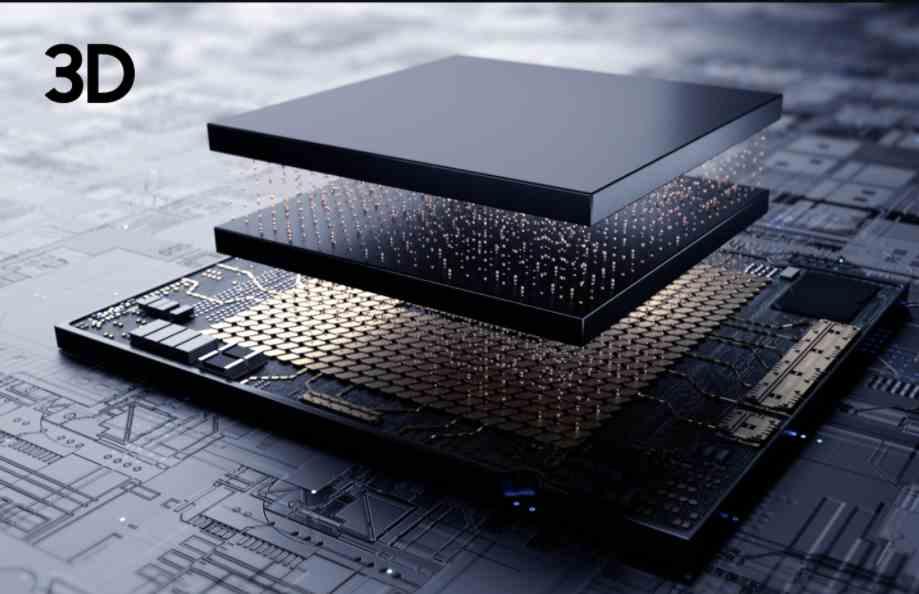

Det bästa sättet att minska latensen skulle vara att skapa minne så nära processorn som en cache, men det är omöjligt att skapa RAM med tillräcklig lagringskapacitet för att vara fullt funktionell. Vi kan placera ett minneschip och ansluta det via TSV, men eftersom minnet är så nära att undvika termisk drunkning och därmed effektiv bandbredd.

I det här fallet, eftersom latens påverkar bandbredd på grund av närheten mellan minne och processor, skulle effekten av latens på minnet vara mycket lägre. Avvägningen mellan att implementera en CPU eller GPU med 3DIC? Det skulle fördubbla datorns kostnader och den mer komplexa tillverkningsprocessen skulle få färre enheter att nå oss, ergo mer knapphet och därmed ännu dyrare priser.