Smakämnen litografi på de marker som används i processorer som vi känner dem har länge kämpat för att minska tillverkningsprocesserna, och vi ser att nanometrarna blir mindre och mindre. Men när det gäller 3D NAND-minne , det har "fastnat" på 40nm under ganska lång tid nu, och trenden är att det ska förbli så åtminstone på medellång sikt. Varför förbättrar de inte litografin minne? Vi berättar allt nedan.

3D NAND-teknik introducerades först 2013 och Samsung gjorde ett bra jobb med att förbättra det 2015; Men sedan dess har varken Samsung eller dess konkurrenter gjort ytterligare förbättringar av detta minne utöver att skapa fler och fler lager för att öka densiteten. Så om 3D NAND-minnet är 40 nm, varför ser vi inte förbättringar med mindre noder som 32 nm, 20 nm osv?

Svaret är att det är nästan omöjligt att minska litografi på grund av hur specifikt kommunikationskanalerna mellan lager tillverkas och vi kommer att förklara det för dig nedan.

Så här tillverkas 3D NAND-kanaler vid 40 nm

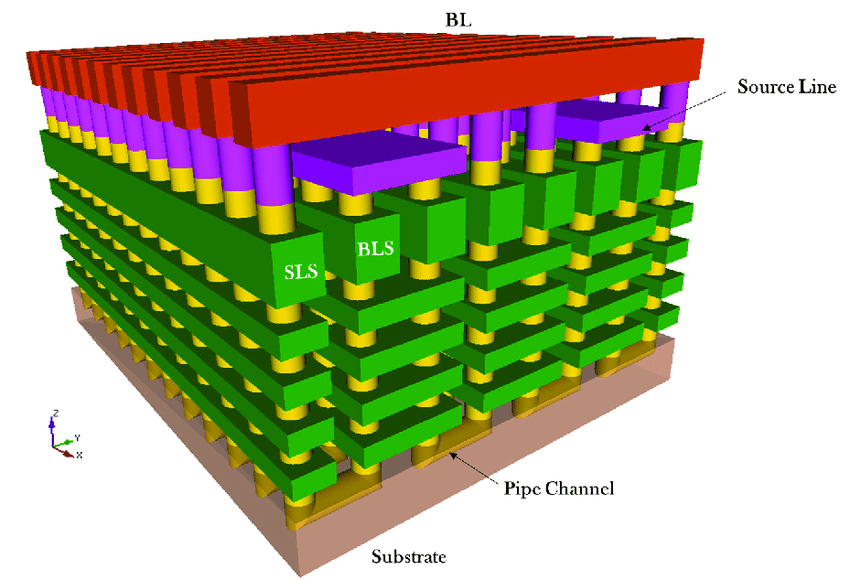

För att förklara varför litografi av 3D NAND-minne inte kan minskas mycket mer kommer vi att använda Toshibas BiCS-struktur (nu används av KIOXIA) som ett exempel.

- Först görs mycket smala hål i alla lager av 3D NAND. Idag har dessa hål ett bildförhållande på cirka 60: 1, vilket är ganska anmärkningsvärt. Tänk på att för denna litografi skulle ett hål på en tum (2.5 ″) vara 1.5 meter långt. Dessa hål är så här, med väggar nästan perfekt parallella från topp till botten som går igenom alla materialskikt och som tjänar till att kommunicera med varandra.

- Dessa hål fylls sedan med stor precision med 5 lager material:

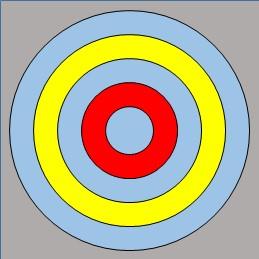

- Det ursprungliga skiktet är kiseloxid (SiO2), vilket gör hålet ännu smalare. Detta visas i ljusblått i diagrammet som vi ska sätta nedan.

- Därefter täcks den med ett annat tunt lager kiselnitrid (Si3N4) också från topp till botten, vilket gör hålet ännu smalare. Detta är laddningsfångarskiktet och visas i gult.

- Det finns ett mycket tunt tredje lager av SiO2, vilket gör hålet ännu smalare.

- Nästa lager är ledande polysilikon. Detta lager visas i rött och fungerar som dataöverföringskanal.

- Slutligen fylls det lilla utrymmet som återstår med SiO2 (blå) igen. Detta slutisolerande fyllmedel hjälper till att "tunna" kanalen så att den fungerar bättre och är mer stabil.

Således bestämmer tjockleken på skikten som fyller hålen deras minsta diameter, och även om vi här har visat det som "stort", är tjockleken på varje inre skikt bara några atomer tjocka och det är praktiskt taget omöjligt att göra dem mindre. .

Av detta skäl måste 3D NAND-minne förbli vid 40 nm under överskådlig framtid, och det är därför alla ansträngningar från tillverkare på senare tid är att öka antalet lager som passerar genom dessa kommunikationshål, logiken i matrisen och förbättrade trappuppsättningar, men inte för att minska litografi eftersom det just nu är nästan omöjligt fysiskt.